优化硅前软件开发

在当今快速发展的技术时代,处理市场需求的最常见方法是片上系统 (SoC)。 SoC 基本上是一个处理器,周围环绕着功能加速器和大量用于它支持的相关外设的 I/O。自 2002 年的移动数据革命以来,使用 SoC 促进定义智能手机的关键功能已成为先决条件。同样,SoC 已成为打造“智能”消费产品(如电视、汽车和不断扩大的物联网 (IoT) 市场)的首选设备。

对 SoC 不断增长的需求创造了一个竞争激烈的市场。正因为如此,SoC 变得越来越复杂,SoC 中的外设在不断发展,上市时间也在缩短。与 SoC 开发的复杂性相匹配的一个关键组件是软件的可用性。几乎没有犯错的余地,软件必须尽快准备就绪。为了应对这一挑战,必须在 SoC 部分可用之前启动软件开发。

SoC 软件开发

传统上,软件开发会在第一个硅样品从制造中出来后开始。当 SoC 样品到达时,软件和验证团队将开始他们的开发活动,并开始大规模的 SoC 开发工作。从事 SoC 工作的团队将来自全球各地,在有限的时间内集中在一个屋檐下,以支持 SoC 的启动。

软件开发通常需要在第一个样本到达之后几个月才能投入生产。同时,硅验证将完成,这将给相关产品的量产提供有限的信心。

然而,由于 SoC 设计的复杂性不断增加,通常需要数月的软件开发时间现在可能需要数年才能投入生产。支持的外围设备数量的增加和这些外围设备的发展也造成了主题专业知识的差距。软件团队需要通过为在这些领域(音频、视频、USB、以太网等)方面具有专业知识的新开发人员提供资源来填补这些特定空白。

为了能够在项目早期交付生产就绪的软件,软件开发不能等到第一个硅样品可用。在软件开发尽早开始的情况下,最好是在 SoC 硬件设计开始的同时,采用左移方法。 Pre-silicon 软件开发还可以帮助识别 SoC 实现错误,并有可能降低金属修复或全掩模流片的成本。考虑了几种方法来满足这些要求。

硅前开发方法

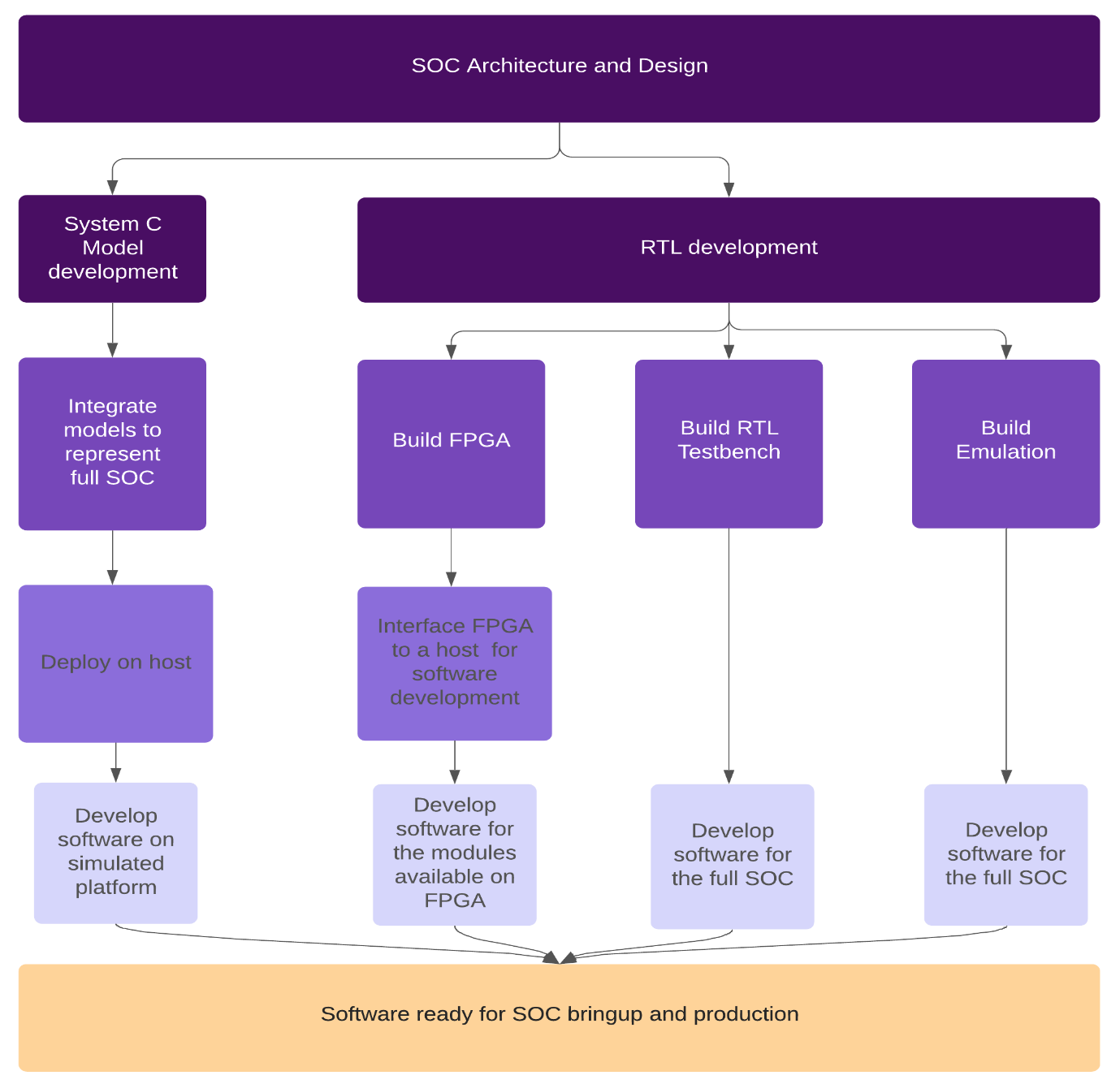

为了在 SoC 流片之前开始软件开发,开发人员可以使用一些方法,例如软件原型、RTL 测试平台、FPGA 板、硬件仿真器等。 由于这些方法通常专注于单个模块,因此这些方法中的每一种都有自己的挑战,因为目标是开发用于启动整个 SOC 而不是单个模块的软件。如果我们将问题分解为更小的模块,那么在开始驱动程序开发之前首先需要了解正在开发的每个处理器、加速器或外围设备。

系统 C 模型

可以为 SoC 的每个 IP 构建 C 行为模型,并且可以在这些行为模型上测试独立的软件驱动程序。但是这种方法有几个问题。首先,需要大量的软件工作,这意味着需要一个庞大的软件团队或专门的模型团队来支持模型本身的实现。因此,模型的开发不会具有成本效益。其次,行为模型的准确性取决于开发人员的解释。 IP 设计所有者和模型开发人员之间的任何沟通差距都可能导致不准确的行为。这导致浪费大量精力来解决与设计误解相关的问题。

RTL 测试平台

为了解决这个不准确问题,可以采取的另一种方法是使用 Verilog 测试平台。测试平台通常由 SoC 设计团队开发和维护以进行验证。 Verilog 测试平台基于 SoC 的寄存器传输语言 (RTL) 规范,代表完整的 SoC,而不仅仅是一些 IP 块。因此,它是周期到周期准确的。随着 RTL 的发展,测试平台也随之发展。这确保它是正在开发的 SoC 的最新和准确表示。出于软件开发目的,Verilog 测试平台也可用于开发软件驱动程序。

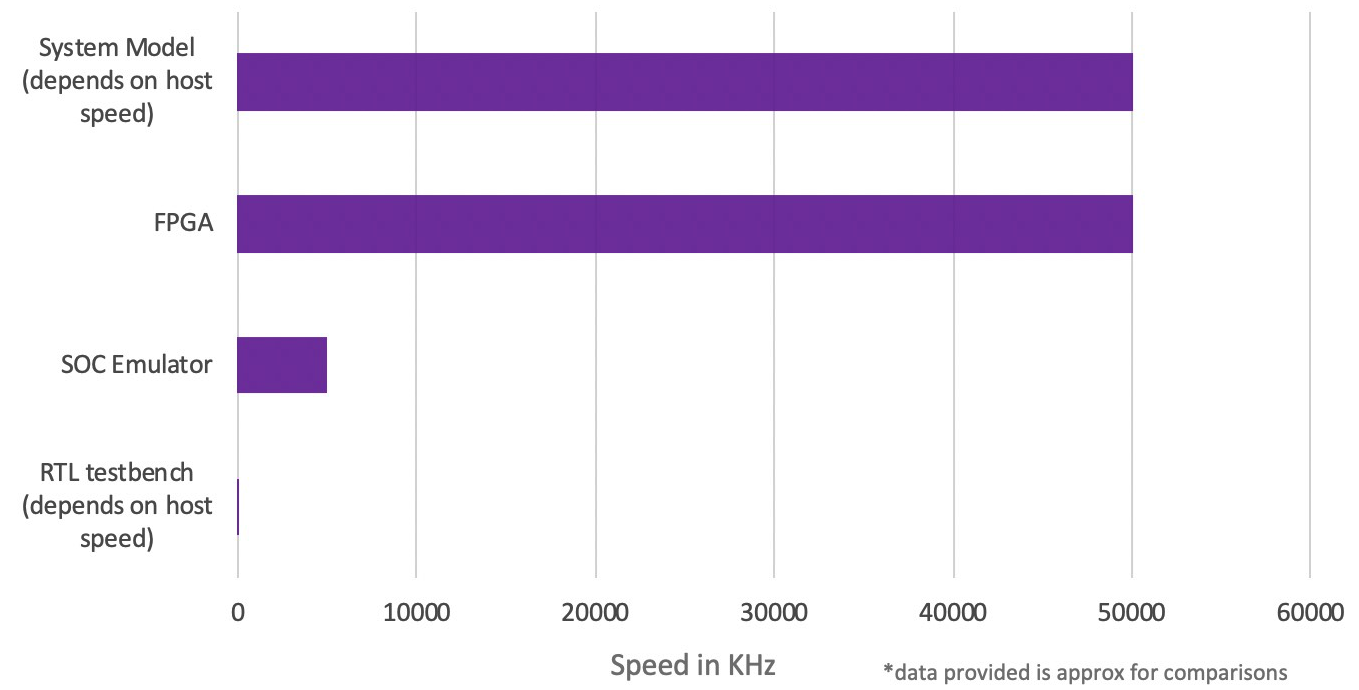

使用这种方法开发的软件是准确的,可以帮助减少 SoC 样品在制造过程后到达时的软件启动时间。但是这种方法有一个问题。因为 Verilog 测试平台是周期准确的,所以速度很慢。在这样的环境中开发软件是可能的,但开发和调试将非常缓慢。使用这种方法开发驱动程序可能需要几个月的时间。 Verilog 测试平台可以通过更早开始使用——本质上增加了硅前所需的时间来解决解决方案的缓慢速度(但取决于测试平台的可用性)。在另一种方法中,另一个软件团队可以使用这种方法(仅用于硅前开发)——本质上增加了所需的资源数量,从而不会消除与 C 行为模型方法类似的问题。

在实践中,我们不能接受不准确或长的开发周期,也不能接受复制或增加资源数量以保持正常设计周期时间表所需的额外成本。因此,我们必须考虑另一种硅前软件开发方法。这种方法将涉及在现场可编程门阵列 (FPGA) 上对每个 SoC IP 模块进行仿真。

FPGA 原型

现代 FPGA 速度相当快,而且由于 FPGA 是从 RTL 构建的,因此它们的周期到周期准确。随着设计复杂性的增加,IP 块比几年前拥有更多的门。多年前,FPGA 受到 ASIC 门数量的限制,这意味着不可能将更大的逻辑块放入单个 FPGA 中。现在可以为每个模块构建一个 FPGA 并在其上开发快速准确的驱动程序。

这种方法更快,并且不需要软件团队尽早分配时间。因为它适用于每个单独的 IP 块而不是整个集成 SoC 设计,所以这种方法限制了软件进行完整的 SoC 级开发。它省略了各种 IP 块如何一起工作的集成细节。因此,虽然这种方法会降低启动工作,但仍然存在差距,因为它错过了相关的 SoC 集成细节。这种方法对于衍生 SoC 来说是一种可以接受的方法,它们的变化数量有限,但不具备 SoC 软件开发所需的全面覆盖。

点击查看大图

图。硅前软件开发解决方案概要。 (来源:Nitin Garg)

SoC 模拟器

为了解决准确性、速度和覆盖范围的问题,可以采用更强大的方法,即使用 SoC 仿真器。市面上有很多 SoC 仿真器,它们可以仿真非常大和复杂的 SoC。 SoC 仿真器基于 RTL,因此它们是准确的,并且比 Verilog 测试平台快 100 倍,使其更适合软件开发。由于它们相当快,因此可以在合理的时间内执行完整的操作系统移植和驱动程序开发。 SoC 仿真器可以扩展整个 SoC,因此软件开发更适合最终生产的 SoC。

使用 SoC 仿真器进行硅前软件开发和设计可以减少软件启动时间和精力,因为它可以消除或减少整体开发差距。还可以使用 SoC 仿真器上的标准 JTAG 工具调试软件。仿真器可用于多种任务,例如 ROM 开发和验证、固件和操作系统开发以及 IP 或 SoC 级验证。 SoC 仿真器的另一个有趣功能是它们可以将 SoC 连接到真实组件,例如开发板上的那些组件。例如,可以将真实或虚拟的 NAND 设备连接到仿真器中的 SoC 并开发 ROM、OS 驱动程序等。

SoC 模拟器比其他软件开发方法提供了更多的可能性。仿真器可以将 SoC 同时连接到 UART、I2C、各种显示器、存储设备、PCIe 设备、以太网和 Wi-Fi 等连接设备以及摄像头和传感器等捕获设备。换句话说,SoC 模拟器可以代表一个实际的开发板,因此可以调出像 Android 这样的完整框架,并在流片 SoC 之前运行完整的用例。例如,在 SOC 模拟器上启动 Android 和解码几帧视频可能需要几个小时,但在分析 SOC 性能方面可能非常有用。

由于 SoC 上外设的可用性不断增加,SoC 仿真对于性能基准测试也非常有用,它可以在流片前突出设计中的弱点。此功能可以降低与 SoC 中未识别的性能缺陷相关的风险或后续流片。如果第三方 IP 需要,SoC 仿真器还可以将 SoC 连接到第三方 FPGA 或软模型。

考虑到仿真器与真实硬件运行相同的操作系统、驱动程序和框架,因此在 SoC 样本到达后调试问题对仿真器也很有帮助。通常需要将在硅中观察到的问题复制到仿真器,以便可以在信号级别对其进行调查。在模拟器和芯片之间使用相同的软件可以更快、更准确地重现问题,从而可以完全访问芯片内部的细节。

比较不同的 SoC 软件开发方法,从硅前开发和硅后调试的角度来看,使用 SoC 仿真器是更好的选择。软件团队运行 SoC 仿真器的成本似乎很昂贵。但是,SoC 仿真器通过更快地提供生产软件并帮助降低风险和成本而提供的贡献,在考虑对上市时间目标的影响时可能证明是无价的。其他软件开发方法没有相同的覆盖范围,这是有风险的,并且可能需要更大的软件团队资源。考虑到所有因素,相比之下,使用 SoC 仿真器以外的软件开发方法可能成本更高。

图 2. 每种解决方案的比较执行速度。 (来源:Nitin Garg)

根据摩尔定律,由于集成电路 (IC) 的功能增加,集成电路 (IC) 中的晶体管数量每两年翻一番。目前大多数基于 ARM 的 64 位 SoC 都有 100-3 亿个逻辑门。在当前的 SoC 软件开发方法中,SoC 模拟器已被证明可以扩展和支持软件开发团队的需求,这些团队面临着与当今竞争激烈的市场中 SoC 日益增加的复杂性相关的挑战。

参考文献

- Trimberger、Stephen M。“FPGA 的三个时代”。 IEEE Xplore 全文 PDF: 2015 年,ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7086413。

- 布鲁内特,让-玛丽。 “为什么现代 SoC 设计采用仿真。” 嵌入式计算设计 ,2018 年 9 月 5 日,embedded-computing.com/embedded-computing-design/why-modern-soc-designs-embrace-emulation。

- “社交模拟”。 社交模拟 , 2019, www.aldec.com/en/solutions/hardware_emulation_solutions/co-emulation–soc-emulation。

- “在集成电路上塞入更多组件。” http://www.cs.utexas.edu/ , 2006, cs.utexas.edu/~fussell/courses/cs352h/papers/moore.pdf。

嵌入式