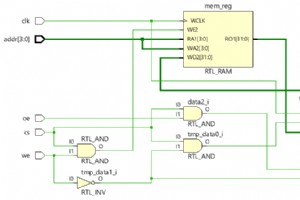

设计 module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); reg [D

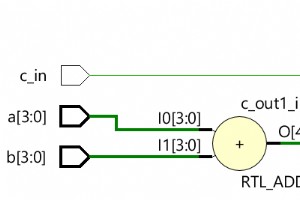

加法器是执行两个数字相加的数字组件。它是处理器 ALU 中的主要组件,用于递增地址、表索引、缓冲区指针以及许多其他需要添加的地方。 全加器将一个进位输入与其他输入二进制数相加,产生一个和和一个进位输出。 真值表 A B 辛 考特 总和 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 设计 下面显示了一个 4 位加法器的示例,它通过信号 a 和 b 接受两个二进制数,这两个信号都是 4 位宽。由于加法器是一个组合电路,它可以在 Verilog

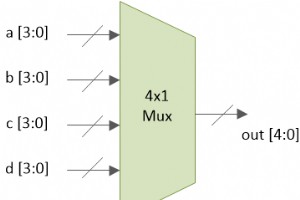

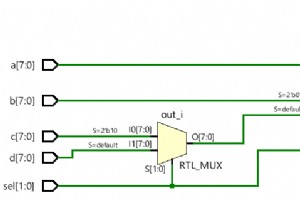

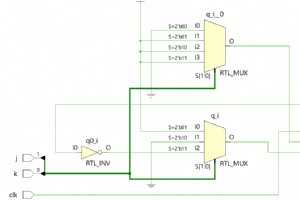

什么是多路复用器或多路复用器? 多路复用器或 mux 简而言之,它是一种基于选择信号将数据从 N 个输入之一传输到输出的数字元件。下面显示的情况是 N 等于 4。例如,一个 4 位多路复用器将有 N 个输入,每一个 4 位,每个输入都可以通过使用选择信号传输到输出。 sel 是一个 2 位输入,可以有四个值。选择线上的每个值都将允许将其中一个输入发送到输出引脚。 sel a b c d out 0 3 7 1 9 3 1 3 7 1 9 7 2 3

设计 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if (

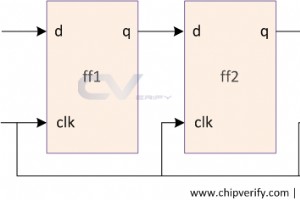

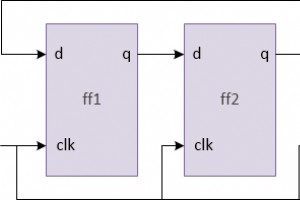

在数字电子学中,移位寄存器 是触发器的级联,其中输出引脚 q 一个触发器连接到下一个触发器的数据输入引脚 (d)。因为所有触发器都在同一个时钟上工作,所以存储在移位寄存器中的位数组将移位一个位置。例如,如果一个 5 位右移位寄存器的初始值为 10110,并且移位寄存器的输入绑定为 0,那么下一个模式将是 01011 和下一个 00101。 设计 此移位寄存器设计有五个输入和一个 n 位输出,该设计使用 parameter 进行参数化 MSB 表示移位寄存器的宽度。如果 n 为 4,则它成为一个 4 位移位寄存器。如果n为8,则成为8位移位寄存器。 这个移位寄存器有几个关键特性:

设计 module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i = 0

设计 module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else out <=

设计 module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1) be

设计 module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) begin

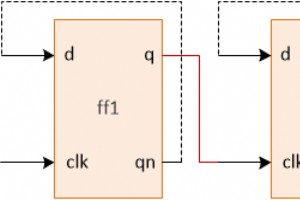

涟漪 计数器是一个异步计数器,其中除第一个触发器之外的所有触发器都由前一个触发器的输出提供时钟。 设计 module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else q <= d;

4 位计数器开始从 4b0000 递增到 4h1111,然后返回到 4b0000。只要它有一个运行时钟并且复位保持高电平,它就会一直计数。 当最终添加的最重要位被丢弃时,就会发生翻转。当计数器达到最大值 4b1111 并再收到一个计数请求时,计数器会尝试达到 5b10000,但由于它只能支持 4 位,因此 MSB 将被丢弃,导致为 0。 0000 0001 0010 ... 1110 1111 rolls over 0000 0001 ... 该设计包含两个输入,一个用于时钟,另一个用于低电平有效复位。低电平有效复位是指当复位引脚的值为 0 时复位设计。

触发器在时钟的上升沿或下降沿在其输入端捕获数据。需要注意的重要一点是,在时钟沿之后直到下一个时钟沿发生的任何数据都不会反映在输出中。一个闩锁 另一方面,不会在时钟边缘捕获,而是只要使能引脚被置位,输出就会跟随输入。 设计 在此示例中,我们将构建一个具有三个输入和一个输出的锁存器。输入 d 代表可以是0或1的数据,rstn 代表低电平有效复位和en 代表使能,用于使输入数据锁存到输出。复位为低电平有效意味着当该输入变为 0 时设计元素将被复位,换句话说,当其值为低时复位有效。输出q的值 由输入 d 决定 , zh 和 rstn . module d_latch ( input

设计 module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule 测试台 module tb; reg clk; reg rstn; r

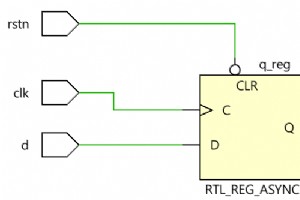

A D 触发器 是跟随输入引脚 d 的顺序元素 在时钟的给定边沿。 设计#1:异步低电平有效复位 module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn) if (!rstn) q <= 0; else q <= d; endmodule 硬件示意图 测试台 modu

设计 module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule 硬件示意图

最好从一个非常简单的示例开始,除了“Hello World !”之外,没有一个最能达到目的。 // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionality module tb; // Initial block is another construct typically used to in

Verilog具有系统任务和功能,可以打开文件、输出值到文件、从文件中读取值并加载到其他变量和关闭文件。 打开和关闭文件 module tb; // Declare a variable to store the file handler integer fd; initial begin // Open a new file by the name my_file.txt // with write permissions, and store the file // handler pointer in variable fd fd = $fopen(

默认时间刻度 虽然预计 Verilog 模块在模块之前定义了时间刻度,但模拟器可能会插入默认时间刻度。可以使用系统任务 $printtimescale 打印在 Verilog 详细层次结构中的任何范围内应用的实际时间刻度 它接受范围作为参数。 module tb; initial begin // Print timescale of this module $printtimescale(tb); // $printtimescale($root); endendmodule 看到即使在这个模块之前没有放置时间刻度指令,模拟器最终还是应用了 1ns/1ns 时间刻度值。

Verilog timescale 指令指定模拟的时间单位和精度。 Verilog $timeformat 系统函数指定 %t $display 等显示语句中的格式说明符报告样式 和 $strobe . 语法 $timeformat(<unit_number>, <precision>, <suffix_string>, <minimum field width>); 单位编号 是所有 `timescale 中最小的时间精度 源代码中使用的指令 精度 表示当前时间刻度的小数位数 后缀字符串 是在实时值旁边显示比例的选项

Verilog 数学函数可以用来代替常量表达式,并且支持 integer 和真实的 数学。 整数数学函数 函数$clog2 返回给定参数的 log2 的上限。这通常用于计算寻址给定大小的内存所需的最小宽度。 例如,如果设计有 7 个并行加法器,则表示所有 7 个加法器所需的最小位数为 $clog2 7 产生 3。 module des #(parameter NUM_UNITS = 7) // Use of this system function helps to reduce the // number of input wires to this m

Verilog