Verilog 全加器

加法器是执行两个数字相加的数字组件。它是处理器 ALU 中的主要组件,用于递增地址、表索引、缓冲区指针以及许多其他需要添加的地方。

全加器将一个进位输入与其他输入二进制数相加,产生一个和和一个进位输出。

真值表

| A | B | 辛 | 考特 | 总和 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

设计

下面显示了一个 4 位加法器的示例,它通过信号 a 和 b 接受两个二进制数,这两个信号都是 4 位宽。由于加法器是一个组合电路,它可以在 Verilog 中使用 assign 的连续赋值进行建模 或 always 带有包含所有输入的敏感度列表的块。下面显示的代码是前一种方法的代码。

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum);

assign {c_out, sum} = a + b + c_in;

endmodule

下面显示的代码使用 always 每当其任何输入更改值时都会执行的块。

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output reg c_out,

output reg [3:0] sum);

always @ (a or b or c_in) begin

{c_out, sum} = a + b + c_in;

end

endmodule

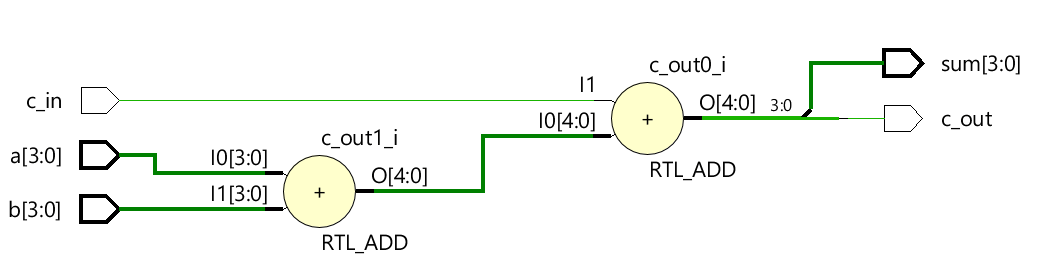

硬件示意图

<无脚本>

测试台

module tb_fulladd;

// 1. Declare testbench variables

reg [3:0] a;

reg [3:0] b;

reg c_in;

wire [3:0] sum;

integer i;

// 2. Instantiate the design and connect to testbench variables

fulladd fa0 ( .a (a),

.b (b),

.c_in (c_in),

.c_out (c_out),

.sum (sum));

// 3. Provide stimulus to test the design

initial begin

a <= 0;

b <= 0;

c_in <= 0;

$monitor ("a=0x%0h b=0x%0h c_in=0x%0h c_out=0x%0h sum=0x%0h", a, b, c_in, c_out, sum);

// Use a for loop to apply random values to the input

for (i = 0; i < 5; i = i+1) begin

#10 a <= $random;

b <= $random;

c_in <= $random;

end

end

endmodule

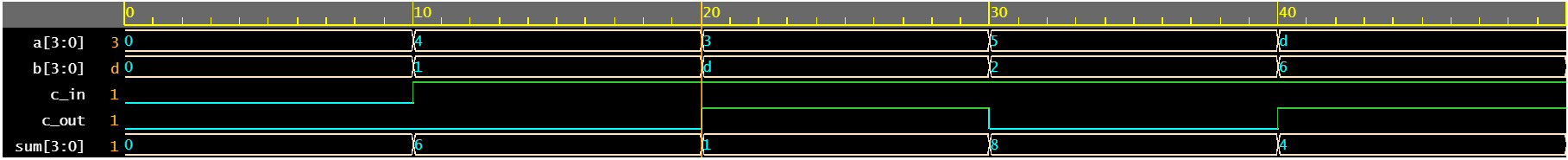

请注意,当 a 和 b 相加得到一个超过 4 位宽的数字时,总和会归零并且 c_out 变为 1。例如,以黄色突出显示的行相加得到 0x11,而低 4 位被分配给sum 和 bit#4 到 c_out。

模拟日志ncsim> run a=0x0 b=0x0 c_in=0x0 c_out=0x0 sum=0x0 a=0x4 b=0x1 c_in=0x1 c_out=0x0 sum=0x6 a=0x3 b=0xd c_in=0x1 c_out=0x1 sum=0x1 a=0x5 b=0x2 c_in=0x1 c_out=0x0 sum=0x8 a=0xd b=0x6 c_in=0x1 c_out=0x1 sum=0x4 a=0xd b=0xc c_in=0x1 c_out=0x1 sum=0xa ncsim: *W,RNQUIE: Simulation is complete.<无脚本>

Verilog