异步复位同步和分配——ASIC 和 FPGA

异步复位和同步逻辑时钟之间缺乏协调会导致上电时出现间歇性故障。在本系列文章中,我们讨论了异步复位的要求和挑战,并探索了 ASIC 与 FPGA 设计的高级解决方案。

VLSI 设计中传统上采用异步复位,用于在上电后将同步电路置于已知状态。异步复位释放操作必须与同步逻辑时钟信号协调,以消除由于复位和时钟之间可能的争用而导致的同步失败。缺乏这种协调会导致上电时出现间歇性故障。当考虑大型、多时钟域设计时,问题会加剧。除了同步问题之外,将异步复位分配到数百万个触发器也具有挑战性,需要类似于 CTS(时钟树合成)的技术并需要类似的面积和布线资源。

回顾了异步复位的要求和挑战,重点是同步和分布问题。讨论了重置同步(重置树源同步)和分发(重置树合成)的经典解决方案的缺点。提供了用于更快、更简单的时序收敛和更可靠的复位同步和分配的高级解决方案。详细介绍了 ASIC 与 FPGA 设计的不同方法。

第 1 部分描述了围绕异步重置的问题并概述了解决这些问题的方法。第 2 部分(本文)讨论了在 ASIC 和 FPGA 中正确异步复位的其他解决方案。第 3 部分讨论了一些有用的特殊情况。

2.异步复位时序收敛技术

第 1 部分中讨论的主要问题之一是大型设计(具有高延迟复位分配网络)的复位释放的复杂性,尤其是在采用短时钟周期时。基于标准 STA 优化的时序收敛导致设计成本高昂,在某些情况下甚至是不可能的。在这里,我们将讨论缓解此时序问题的两种技术。这两种技术都适用于 ASIC 和 FPGA 设计。

2.1.异步复位流水线

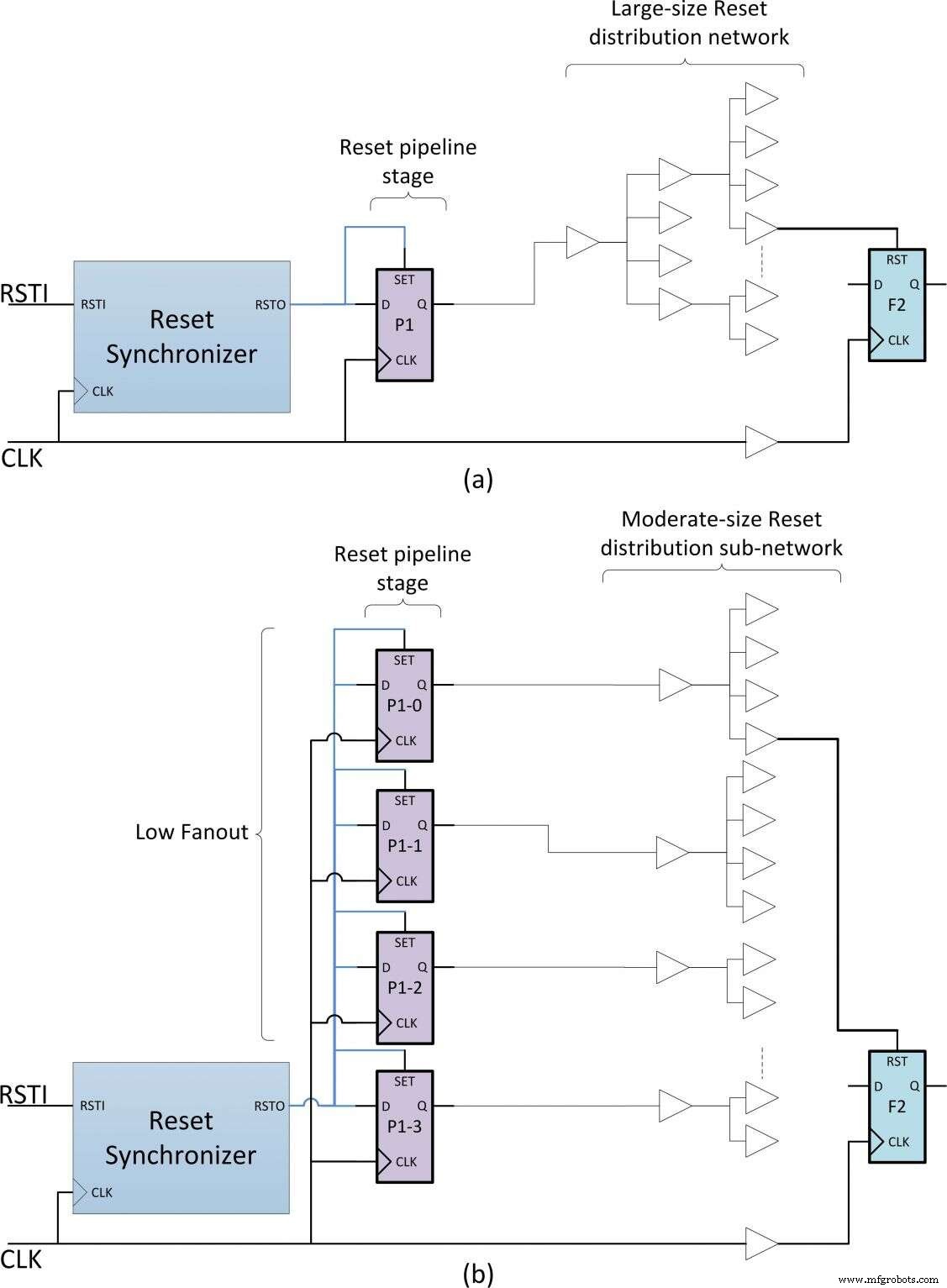

处理异步复位释放时序问题的一种方法是权衡复位释放延迟以获得更宽松的时序。这可以通过以下方式流水线化重置树来实现。在每个同步器之后,复位线上包含一个额外的异步置位触发器级 P1(图 6a)。触发器的 SET 和 D 输入都连接到来自复位同步器的高电平有效复位 RSTO。在 RSTO 版本中,P1 D 和 SET 输入满足建立和保持条件,因为它们被限制为常规同步路径。

点击查看大图

图 6:带有流水线的异步重置(来源:vSync Circuits)

新方案的功能操作类似于第 1 部分(图 3d)中描述的常规方案,除了复位释放时的额外单周期延迟。这种技术产生的较高复位延迟对于大多数应用来说通常是可以接受的,因为每次上电只会产生一次。

该技术的补充部分涵盖了设计约束。虽然同步器触发器必须限制重复以防止重新收敛路径问题,如第 1 部分所述,但流水线阶段 P1 受 MAX_FANOUT 约束。最大扇出约束的示例如图 6b 所示。 P1 触发器自动 由综合工具复制,为重置分布创建四个子网络。每个子网的时延都比原网低,满足复位释放的时序要求。此外,复位同步器的输出很容易满足8个扇出。

这种异步复位流水线技术可针对任何设计尺寸进行扩展,并且在设计发生变化时无需更改,因为综合工具会自动复制 P1 级,从而保持中等延迟复位子网有界。同步器输出的复制 P1 级扇出通常很小,不会导致时序违规。然而,当单个流水线级不会导致时序收敛时,可以包含额外的流水线级 P2 – PN 并使用不同的 MAX_FANOUT 约束进行约束。

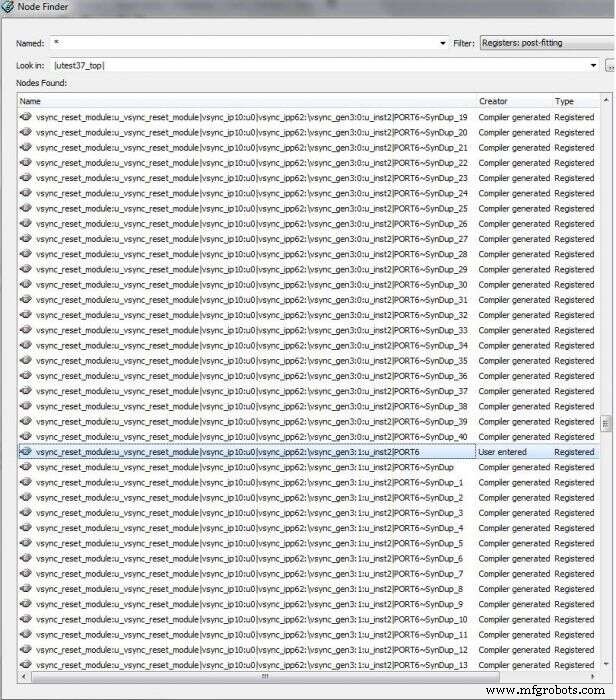

这种技术应用于实际设计的示例如图 7 所示。名为 PORT6 的 P1 级寄存器被综合工具 [6] 自动复制了大约 40 次以满足 MAX_FANOUT 约束。 40 个子网中的每一个都满足其本地扇出的时序要求。

点击查看大图

图 7:异步重置流水线示例(来源:vSync Circuits)

嵌入式