异步复位同步和分发——挑战和解决方案

异步复位和同步逻辑时钟之间缺乏协调会导致上电时出现间歇性故障。在本系列文章中,我们讨论了异步复位的要求和挑战,并探索了 ASIC 与 FPGA 设计的高级解决方案。

VLSI 设计中传统上采用异步复位,用于在上电后将同步电路置于已知状态。异步复位释放操作必须与同步逻辑时钟信号协调,以消除由于复位和时钟之间可能的争用而导致的同步失败。缺乏这种协调会导致上电时出现间歇性故障。当考虑大型、多时钟域设计时,问题会加剧。除了同步问题之外,将异步复位分配到数百万个触发器也具有挑战性,需要类似于 CTS(时钟树合成)的技术并需要类似的面积和布线资源。

回顾了异步复位的要求和挑战,重点是同步和分布问题。讨论了重置同步(重置树源同步)和分发(重置树合成)的经典解决方案的缺点。提供了用于更快、更简单的时序收敛和更可靠的复位同步和分配的高级解决方案。详细介绍了 ASIC 与 FPGA 设计的不同方法。

第 1 部分(本文)描述了围绕异步重置的问题并概述了解决这些问题的方法。第 2 部分讨论了在 ASIC 和 FPGA 中正确异步复位的其他解决方案。第 3 部分讨论了一些有用的特殊情况。

1.异步重置挑战

复位功能通常包含在数字 VLSI 设计中,以便将逻辑置于已知状态。控制逻辑大多需要复位,可以从数据路径逻辑中去除,减少逻辑面积。复位相对于时钟信号可以是同步的,也可以是异步的。

同步复位需要一个活动时钟,会产生某些与时钟周期相关的延迟,并可能影响数据路径的时序。另一方面,同步复位是确定性的,不会引起亚稳态。

异步复位不需要活动时钟来使触发器进入已知状态,具有比同步复位更低的延迟,并且可以利用不影响数据路径时序的特殊触发器输入引脚。但是,异步重置有许多缺点:

它们可能会导致触发器的亚稳态,从而导致非确定性行为。

异步重置必须可以直接访问以启用 DFT。

异步重置可能会导致辐射难应用中的可靠性问题,容易受到单事件瞬态 (SET) 现象的影响 [1]。

撇开关于哪种类型的重置更好的讨论 [2],在本文中,我们专注于与异步重置相关的问题和解决方案。本文中介绍的一些技术适用于异步和同步复位。

异步复位广泛用于数字设计。异步复位的典型驱动器是外部端口,取决于电源状态(RC 电路、看门狗设备)、手动复位按钮和外部主控器,例如微处理器。

在许多情况下,异步复位可以被同步复位代替,但在某些情况下,异步复位功能是强制性的。一个例子是一种同步设计,它在上电时没有活动时钟(时钟不稳定或门控以降低功耗),但需要其外部接口的某个已知状态。另一个例子是低功耗设计,需要在上电过程中最小化功耗,没有活动时钟。

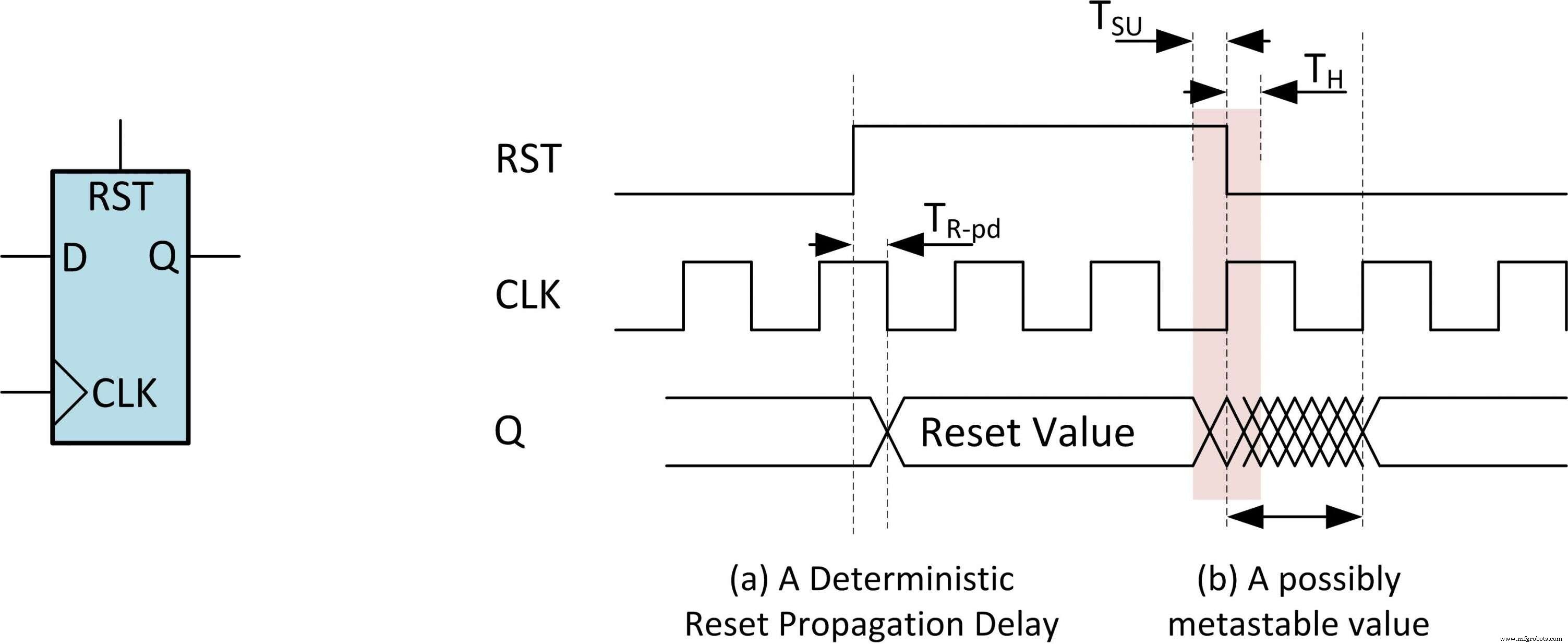

异步复位的使用并不简单。虽然在复位断言期间可以忽略时钟和复位之间的相对时序,但复位释放必须与时钟同步。避免复位释放边缘同步可能会导致亚稳态。参考图 1,显示了一个高电平有效异步复位。复位断言 (a) 在确定性有界时间(传播延迟,TR-pd)内影响触发器输出 Q,而不管时钟信号 CLK。在复位释放 (b) 期间,必须满足 RST 端口相对于时钟端口 CLK 的建立和保持时序条件。违反 RST 端口的建立和保持条件(也称为复位恢复和移除时序)可能会导致触发器变为亚稳态,从而由于切换到未知状态而导致设计失败。请注意,这种情况类似于违反触发器数据端口 D 的建立和保持条件。

点击查看大图

图 1:高电平有效异步复位断言和释放。 (a) 异步复位断言 (b) 具有时序违规的异步复位释放。 (来源:vSync 电路)

嵌入式