嵌入式设计与 FPGA:实现

更强大的 FPGA 和更有效的编程环境的可用性使得 FPGA 实现可广泛访问,但使用 FPGA 似乎令人生畏。

编者注:随着用于智能产品设计的高级算法不断涌现,开发人员经常发现自己难以实现能够满足这些算法相关处理需求的嵌入式系统。 FPGA 可以提供所需的性能,但长期以来,使用 FPGA 进行设计一直被认为仅限于 FPGA 编程专家的权限。然而,如今功能更强大的 FPGA 和更有效的开发环境的出现使得 FPGA 开发变得更加容易。在此摘录中,即《架构高性能嵌入式系统》一书中的第 4 章,作者全面回顾了 FPGA 器件、实现语言和 FPGA 开发过程,并详细介绍了如何开始在您自己的环境中实现 FPGA。设计。完整的摘录在以下系列文章中提供:

编者注:随着用于智能产品设计的高级算法不断涌现,开发人员经常发现自己难以实现能够满足这些算法相关处理需求的嵌入式系统。 FPGA 可以提供所需的性能,但长期以来,使用 FPGA 进行设计一直被认为仅限于 FPGA 编程专家的权限。然而,如今功能更强大的 FPGA 和更有效的开发环境的出现使得 FPGA 开发变得更加容易。在此摘录中,即《架构高性能嵌入式系统》一书中的第 4 章,作者全面回顾了 FPGA 器件、实现语言和 FPGA 开发过程,并详细介绍了如何开始在您自己的环境中实现 FPGA。设计。完整的摘录在以下系列文章中提供:

1:硬件资源

2:实现语言

3:开发过程

4:构建项目

5:实现(本文)

改编自《架构高性能嵌入式系统》,作者:Jim Ledin。

测试逻辑行为

在尝试在 FPGA 中运行之前,使用仿真测试逻辑的行为非常重要。这是因为在仿真环境中检测和修复问题比在 FPGA 内部运行的逻辑要容易得多。 Vivado 仿真工具在表示电路行为方面做得非常好:

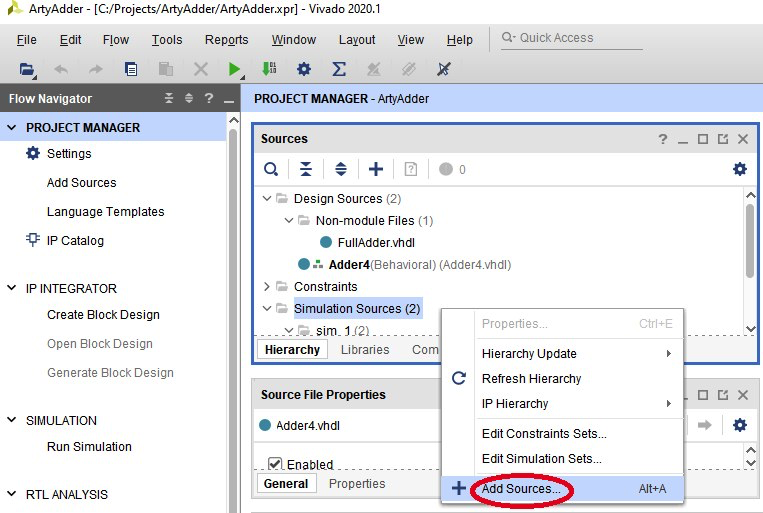

- 在来源 在子窗口中,右键单击 Simulation Sources 并选择添加来源... :

图 4.18 – 模拟源的添加源...菜单选择

- 在添加来源 对话框,确保添加或创建模拟源 被选中,然后点击下一步 .

- 在添加或创建模拟源 对话框,点击创建文件 .

- 输入文件名vhdl 然后点击确定 .

- 点击完成 关闭添加或创建模拟源 对话框,然后单击确定 在定义模块 对话框并点击是 当被问及是否确定要使用这些时

- 双击Adder4 TestBench(行为)(Adder4TestBench.vhdl) 在模拟源下 .删除 vhdl 自动填充的内容 编辑器窗口并在 Adder4TestBench.vhdl 中输入以下代码 编辑:

图书馆IEEE;使用 IEEE.STD_LOGIC_1164.ALL;使用 IEEE.NUMERIC_STD.ALL;entity ADDER4_TESTBENCH isend entity ADDER4_TESTBENCH;architecture BEHAVIORAL of ADDER4_TESTBENCH is component ADDER4 is port (A4:in std_logic_vector(3 downto 0); B4 :in std_logic_vector(3 downto 4_0); 0); C_OUT4 :输出 std_logic );终端组件;信号 a :std_logic_vector(3 downto 0);信号 b :std_logic_vector(3 downto 0);信号 s :std_logic_vector(3 downto 0);信号 c_out :std_logic;信号 expected_sum5:unsigned(4 downto 0);信号 expected_sum4:unsigned(3 downto 0);信号预期_c:std_logic;信号错误:std_logic;开始TESTED_DEVICE:ADDER4端口映射(A4 => a,B4 => b,SUM4 => s,C_OUT4 => c_out);测试:进程开始——在 0 到 15 循环中为 a_val 测试两个 4 位加数的所有组合(总共 256 个测试)对于 0 到 15 循环中的 b_val —— 设置 ADDER4 组件的输入 a <=std_logic_vector(to_unsigned( a_val, a'length)); b <=std_logic_vector(to_unsigned(b_val, b'length));等待 1 ns; -- 计算两个 4 位值的 5 位总和 expected_sum5 <=unsigned('0' &a) + unsigned('0' &b);等待 1 ns; -- 将总和分成 4 位输出和进位位 expected_sum4 <=expected_sum5(3 downto 0); expected_c <=expected_sum5(4);等待 1 ns; -- 如果 ((unsigned(s) =unsigned(expected_sum4)) 和 (c_out =expected_c)) then error <='0';否则错误 <='1';万一; -- 每次通过内循环需要 10 ns 等待 7 ns;结束循环;结束循环;等待;端流程测试;端架构行为; 此代码通过向每个 A4 呈现 4 位数字的所有组合来练习 4 位加法器功能 和 B4 Adder4 的输入 零件。它比较 SUM4 和 C_OUT4 Adder4 的输出 组件独立计算相同输入的值。每次添加操作后,error 如果 Adder4 信号设置为 0 输出与预期值匹配,或者设置为 1 如果不匹配。

Adder4TestBench.vhdl 中的代码 类似于传统的软件代码,它使用嵌套的 for 循环将所有测试输入组合应用到 Adder4 被测组件。在模拟模式下运行测试的代码是不可综合的,这意味着它并不纯粹代表硬件逻辑电路,并且能够进行传统的类似软件的操作,例如迭代执行for 循环。

但是,与物理电路一样,在测试台代码中使用 <=运算符分配值的信号不能在随后的表达式中同时使用。这是因为仿真环境代表了传播延迟的真实世界影响,即使在微型 FPGA 设备中也很重要。三个等待1 ns;测试台代码中的语句暂停电路操作以允许传播延迟。这些 1 ns 的延迟为在 wait 之前计算的信号值提供了时间 语句进行传播,以便它们可以在以下语句中使用。最后的等待7 ns;内循环中的语句是一个暂停,可以让我们在信号轨迹显示中清楚地看到仿真循环每次迭代的结果。

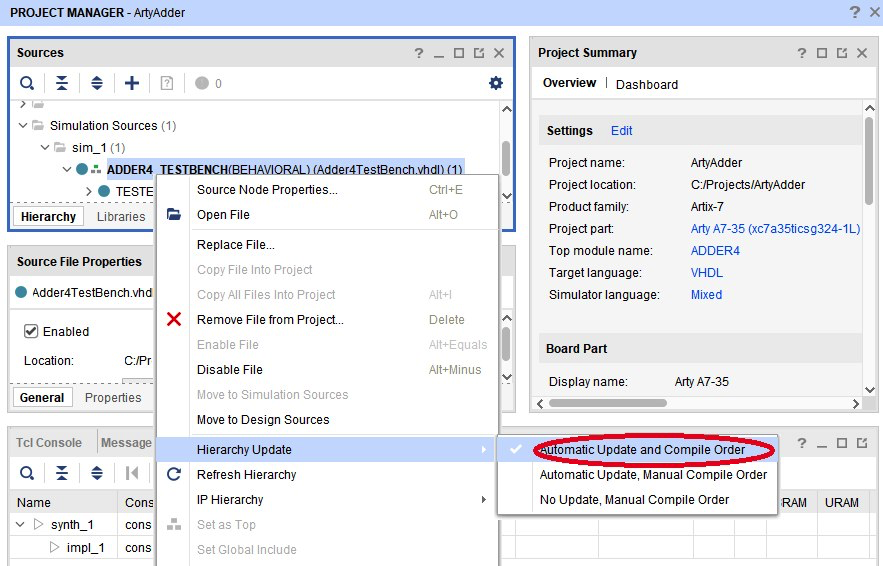

- 右键单击 Adder4 TestBench(行为)(Adder4TestBench.vhdl) 在模拟源下 并选择自动更新和编译顺序 .这将设置 ADDER4_TESTBENCH 作为模拟运行的顶级对象:

图 4.19 – 设置自动更新和编译顺序的菜单选择

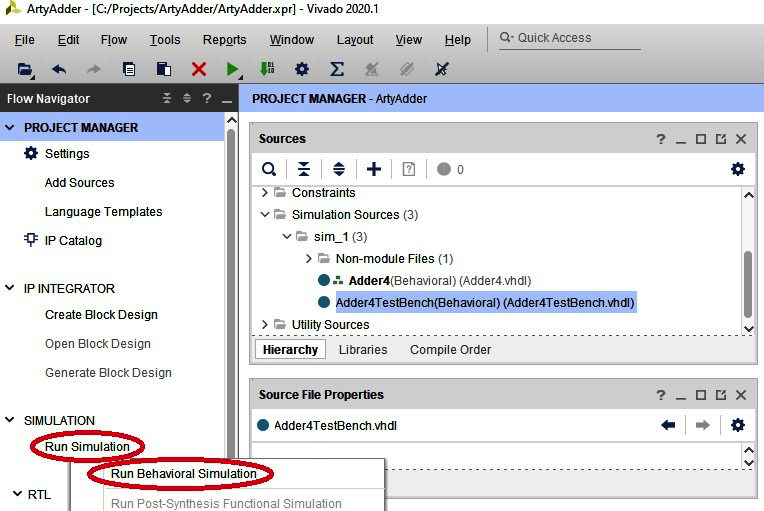

- 点击运行模拟 ,然后运行行为模拟 在流导航器 窗口进入模拟模式。如果您尚未保存编辑器文件,系统会提示您这样做。点击保存 .然后将运行模拟:

图 4.20 – 运行行为模拟菜单选择

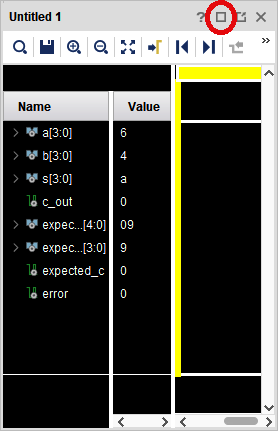

- 当模拟 窗口打开,单击模拟输出窗口中标题为 Untitled 1 的最大化按钮 :

图 4.21 – 模拟结果窗口

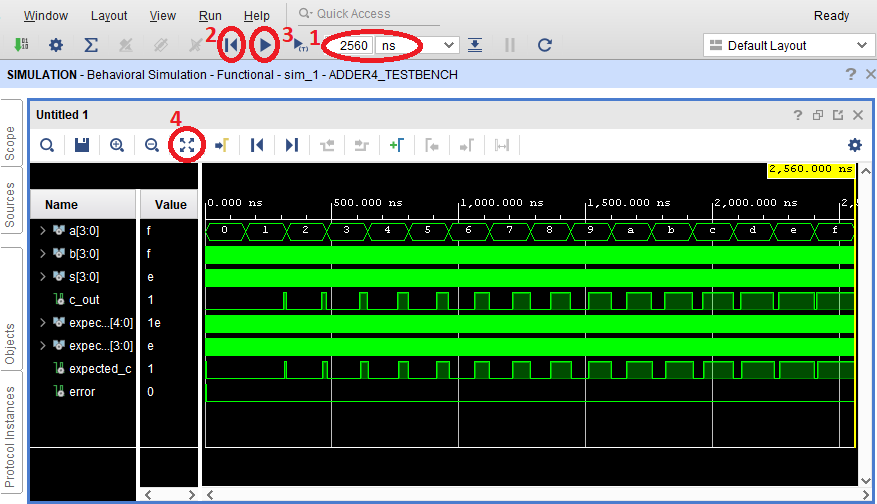

每次通过内循环的总模拟时间为 10 ns。因为在 Adder4TestBench.vhdl 中有 256 次循环通过 , 运行仿真时间为 2560 ns。

- 在顶部工具栏中将模拟运行时间设置为 2560 ns(步骤 1 在下图中),按下左指的重启按钮(步骤 2 ),然后按向右的按钮运行 2560 ns 的模拟(步骤 3 ),最后,按下 Zoom Fit 按钮(第 4 步 ) 缩放模拟输出数据范围以适应窗口:

图 4.22 – 从运行开始到结束的模拟结果

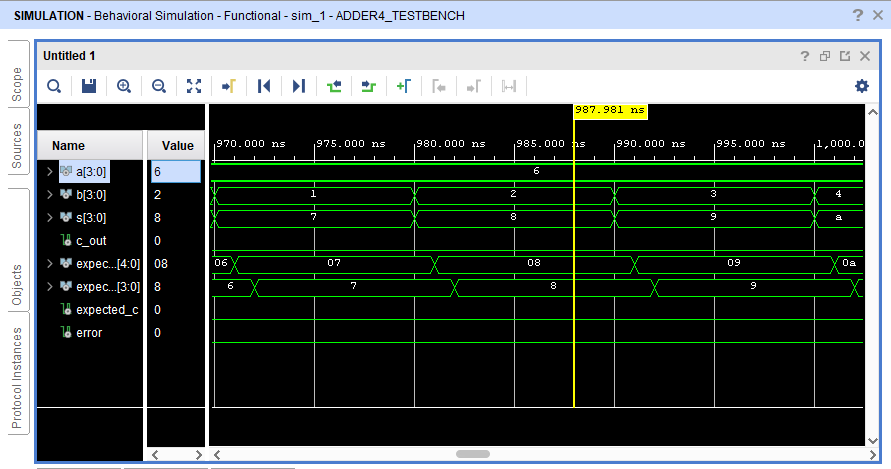

您可以使用放大镜图标放大迹线的任何点并观察测试期间执行的每个加法操作的结果。例如,下图显示了十进制值 6 和 2 相加产生进位为 0 的结果 8。这些值与预期值匹配,从而导致 error 设置为 0。error 256个测试用例的信号都是0,说明我们的逻辑电路通过了所有的测试:

图 4.23 – 模拟结果的放大视图

- 点击 X 关闭模拟模式 在蓝色模拟 数据轨迹上方的栏单击确定 当系统询问您是否要关闭模拟时。

通过行为测试后,我们将定义设计中使用的 I/O 信号。

定义 I/O 信号

我们的下一步是将电路的输入和输出连接到 Arty 板上的硬件设备。输入将是电路板开关和按钮,输出将是 LED。

以下步骤将创建一个约束文件,该文件描述了我们将在 FPGA 设备上使用的 I/O 引脚以及连接到 Arty 板上这些引脚的功能。约束文件具有 xdc 扩展名:

- 在来源 子窗口,右键单击约束 并选择添加来源... .

- 在添加来源 对话框,确保添加或创建约束 被选中,然后点击下一步 .

- 在添加或创建约束 对话框,点击创建文件 .

- 输入文件名Arty-A7-100.xdc (或 Arty-A7-35.xdc 如果适用于您的设备)并点击确定 .

- 点击完成 取消添加或创建约束

- 扩展约束 源树并双击 Arty-A7-35.xdc .

- Digilent 为 Arty A7 板提供预先填充的约束文件访问 https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc 并将浏览器窗口的全部内容复制到 Vivado 中的 Arty-A7-35.xdc 编辑器窗口中。如果适合您的设备,请使用 https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc 上的文件 相反。

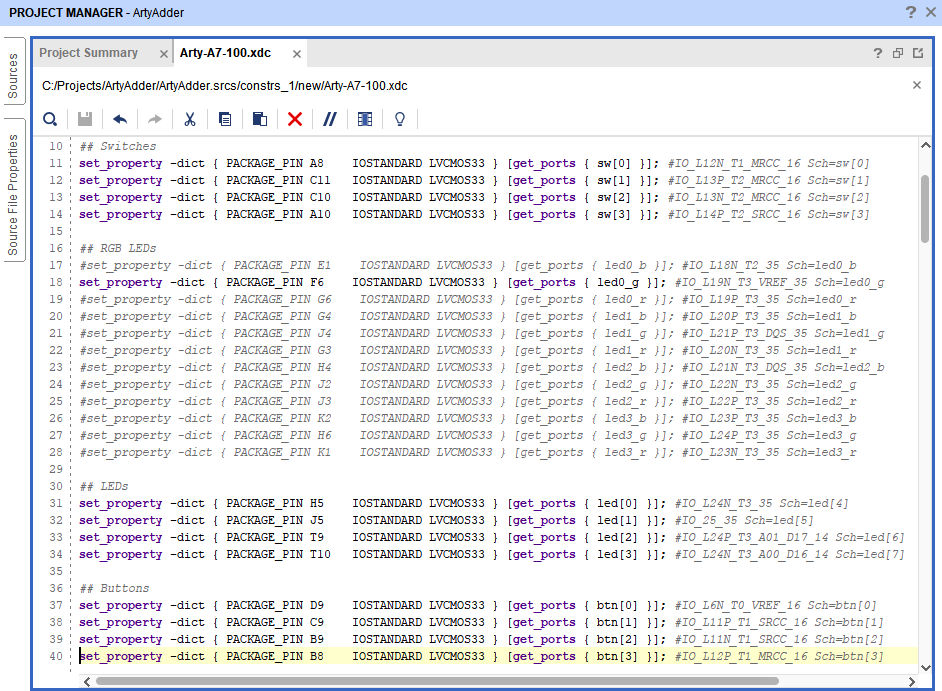

- 通过从每行的开头删除 # 字符,取消对文件中相应行的注释,从而在约束文件中注释掉所有 I/O 引脚。我们将在 Arty- 中使用以下部分中列出的引脚 A7-100.xdc 文件:开关 , RGB LED (但只有 led0_g , 第一个绿色 LED), LEDs , 和 按钮 .下图显示了取消注释后的这些行:

图 4.24 – 约束编辑器窗口

在下一节中,我们将创建一个顶级 VHDL 文件,它将加法器代码与 I/O 设备连接起来。

创建顶级 VHDL 文件

接下来,我们将创建一个顶级 VHDL 文件,将我们的 4 位加法器组件连接到相应的电路板 I/O 信号:

- 在来源 子窗口,右键单击 Design Sources 并选择添加来源... .

- 在添加来源 对话框,确保添加或创建设计源 被选中,然后点击下一步 .

- 在添加或创建设计源 对话框,点击创建文件 .

- 输入文件名vhdl 然后点击确定 .

- 点击完成 关闭添加或创建设计源 对话框,然后单击确定 在定义模块 对话框并点击是 当被问及是否确定要使用这些时

- 双击 vhdl 在设计来源下 .删除 ArtyAdder.vhdl 自动填充的内容 编辑器窗口并在 ArtyAdder.vhdl 中输入以下代码 编辑:

-- 加载标准库 IEEE;使用 IEEE.STD_LOGIC_1164.ALL;entity ARTY_ADDER 是端口(sw:在 STD_LOGIC_VECTOR(3 downto 0)中;btn:in STD_LOGIC_VECTOR(3 downto 0);led:out STD_LOGIC_VECTOR(3 downto 0); ARTY_ADDER;ARTY_ADDER 的架构行为是——参考之前定义的 4 位加法器组件 ADDER4 是端口 ( A4 :in std_logic_vector(3 downto 0); B4 :in std_logic_vector(3 downto 0); SUM4 :out std_logic_vector(3) downto 0); C_OUT4 :out std_logic );末端组件;开始加法器:ADDER4 端口映射(A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g );末端架构行为;

此代码映射 Arty-A7-100.xdc 中命名的 I/O 设备的信号名称 作为 sw (4 个开关), btn (4 个按钮),led (4 个单色 LED)和 led0_g (第一个多色 LED 的绿色通道)到 ADDER4 输入和输出。

虽然 VHDL 不区分大小写,但 xdc 的处理 Vivado 中的约束文件区分大小写。 xdc 中定义的 I/O 设备名称中使用的大小写 在 VHDL 文件中引用时,文件必须相同。具体来说,VHDL中的I/O信号名称在这个文件中必须是小写的,因为它们在约束文件中是小写的。

我们现在已准备好对 Arty 板的设计进行综合、实施和编程。

合成和实现FPGA比特流

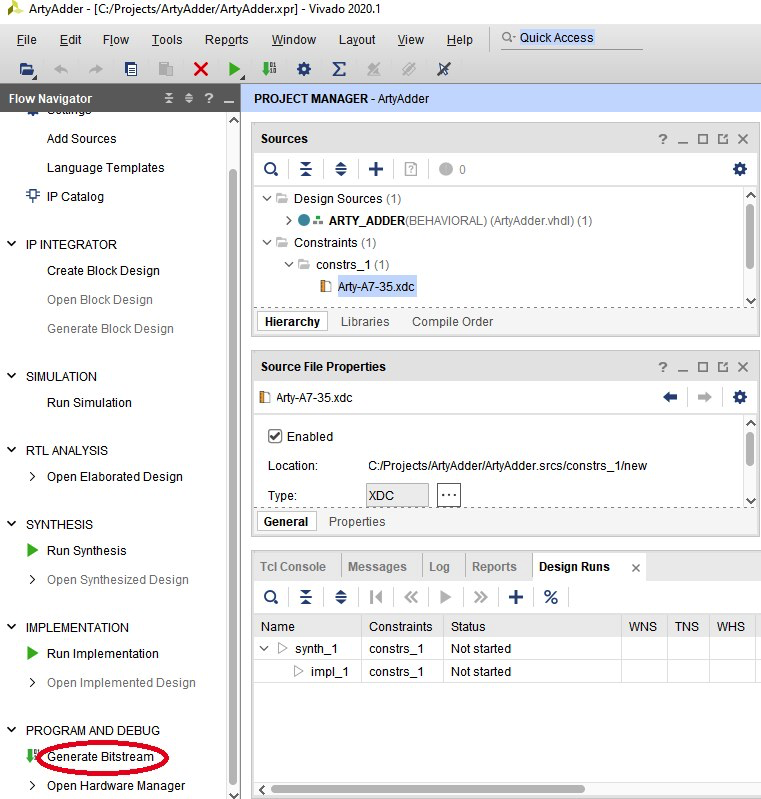

或者,您可以选择生成比特流 Vivado 将执行所有必需的步骤,包括综合、实现和比特流生成,无需进一步的用户干预。如果发生致命错误,进程将停止并显示错误消息。执行以下步骤来生成比特流:

- 点击生成比特流 开始构建 您可能会被问到是否要保存文本编辑器。点击保存 .您可能会被告知没有可用的实施结果,并询问是否可以启动综合和实施。点击是 :

图 4.25 – 生成比特流菜单选择

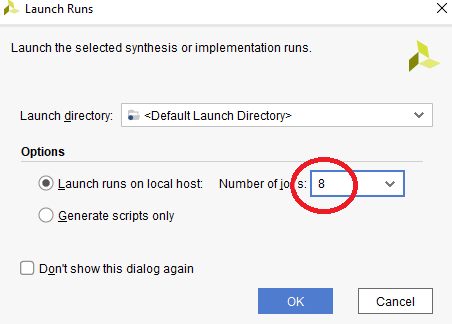

- 启动运行 然后您可以为作业数量选择一个值 最多为您计算机中的处理器内核数。使用更多内核可以加快进程,但如果您想在漫长的构建过程中继续使用它,它可能会使您的机器陷入困境。点击确定 开始构建:

图 4.26 – 启动运行对话框

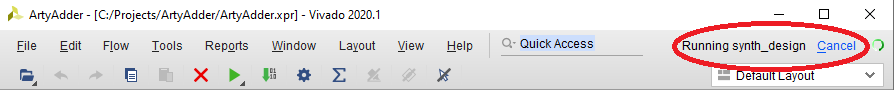

- 在构建过程中,Vivado 将在主窗口的右上角显示状态。如有必要,您可以通过单击取消来取消构建过程 状态显示旁边:

图 4.27 – 编译状态显示

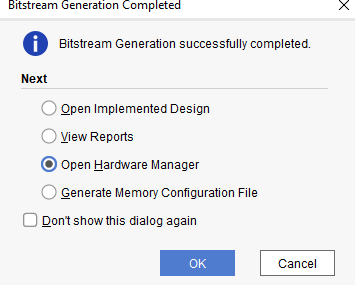

- 当构建过程完成时,假设没有致命错误,比特流生成完成 对话框将 尽管提供了其他选项,但我们将直接将比特流下载到 Arty 板。选择打开硬件管理器 然后点击确定 :

图 4.28 – 比特流生成完成对话框

接下来,我们将把比特流下载到 FPGA 中。

下载比特流到板

执行以下步骤将比特流下载到 Arty A7 板:

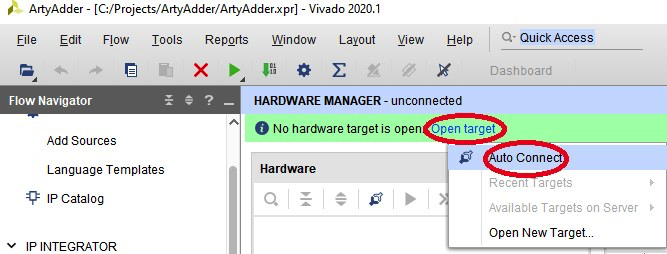

- 硬件经理 将出现对话框并指示没有打开硬件目标 .

- 使用 USB 将 Arty A7-35 或 A7-100 板连接到计算机 等待几秒钟以识别板,然后单击打开目标 ,然后自动连接 :

图 4.29 – 打开目标和自动连接选择

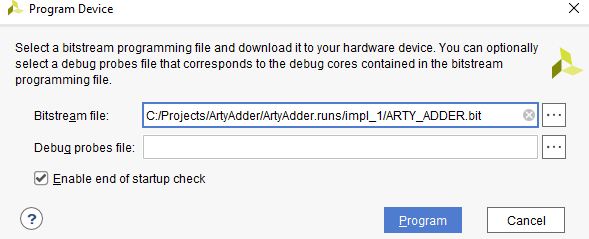

- 几秒钟后,Vivado 应指示电路板已连接。点击编程设备 将 FPGA 比特流下载到 Arty 系统将提示您选择比特流文件。如果您使用与本示例相同的目录结构,则该文件将位于 C:/Projects/ArtyAdder/ ArtyAdder.runs/impl_1/ARTY_ADDER.bit :

图 4.30 – 编程设备对话框

- 点击程序 将程序下载到 FPGA 设备并启动它

- 您现在可以使用 Arty I/O 测试程序的运行情况 将所有四个开关置于 off 位置(将开关移向相邻的板边缘)并且不要按下四个按钮中的任何一个。所有四个绿色 LED 均应熄灭。

- 如果您打开任何单独的开关或按下任何一个按钮,相应的绿色 LED 应亮起。在按下任意数量的按钮的同时打开任意组合的开关将添加相应的 4 位数字,并点亮带有进位的 LED(例如,打开 SW3 然后按 BTN3 同时),绿色进位 LED 将亮起。

此处执行的编程过程将程序存储在 FPGA RAM 中。如果您在 FPGA 板上循环上电,您将需要重复编程过程以重新加载程序。或者,您可以将 FPGA 配置文件存储在板载闪存中,如下一节所述。

将比特流编程到板载闪存

为了在每次给 Arty 板加电时配置 FPGA,FPGA 配置文件必须存储到板上的闪存中。如果安装了 MODE 跳线,FPGA 将在上电时尝试从板载闪存下载配置文件。该存储器位于与 Artix-7 FPGA 相邻的单独芯片中。按照以下步骤将配置文件编程到闪存:

- 安装模式 在 Arty 板上的跳线(如果它尚未进入)

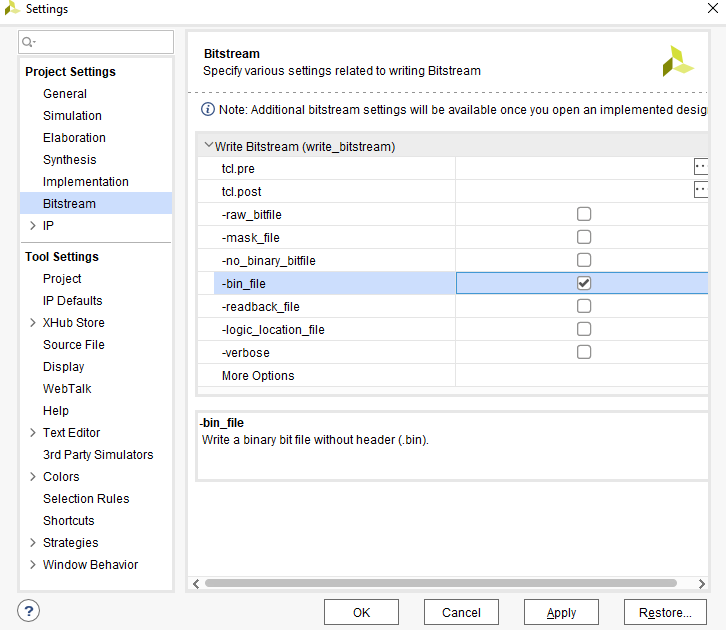

- 右键单击生成比特流 并选择比特流设置... .

- 在设置 对话框,选中 -bin_file 旁边的框 然后点击确定 :

图 4.31 – 比特流设置对话框

- 在 Vivado 主对话框中,单击 Generate Bitstream 并重复比特流生成过程。点击取消 当比特流生成完成 对话框

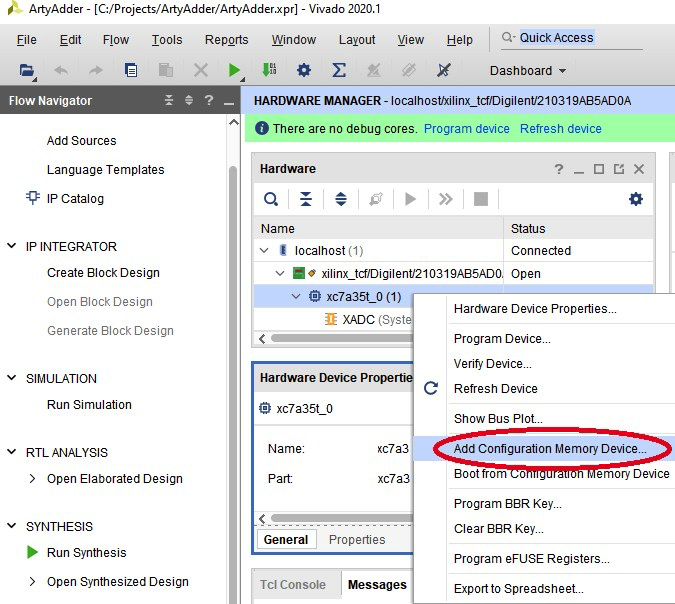

- 在硬件 对话框中,右键单击 FPGA 部件号 (xc7a100t_0 ) 并选择添加配置存储设备... :

图 4.32 – 添加配置存储设备...菜单选择

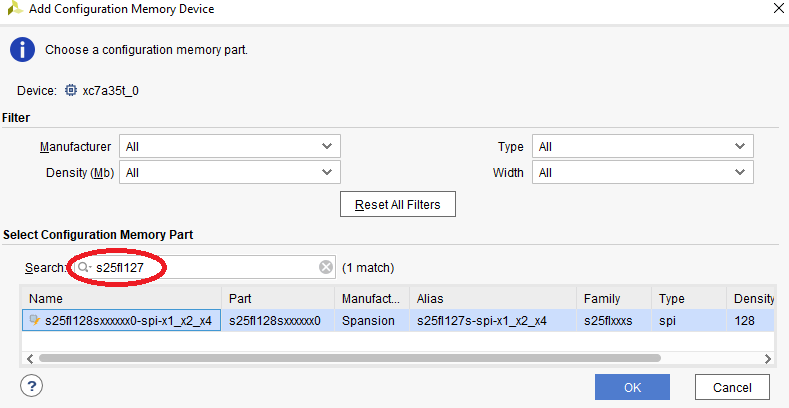

- 输入 s25fl127 进入搜索 这应该会显示一个匹配的部件号。选择零件并单击确定 :

图 4.33 – 添加配置存储设备对话框

- 您将看到一个对话框,询问您现在要对配置存储设备进行编程吗? 点击确定 .

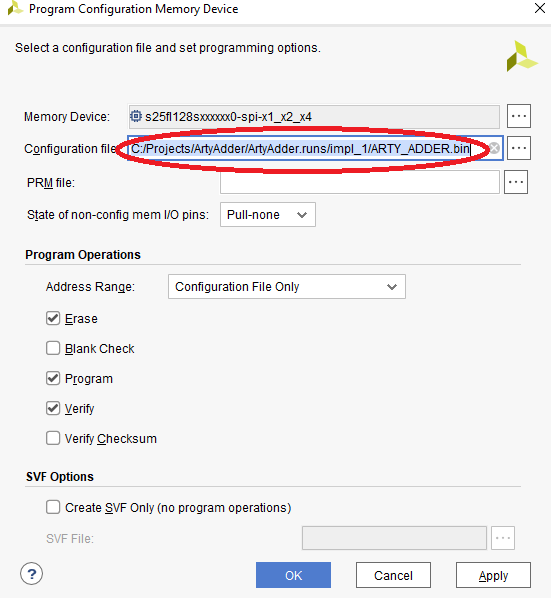

- 这将打开一个程序配置存储设备 对话框请求配置文件名。点击… 配置文件右侧的按钮 并选择 C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin。 点击确定 :

图 4.34 – 程序配置存储设备对话框

- 编程过程将需要几秒钟的时间,您应该会在文件被编程到板闪存后收到一条指示成功的消息:

图 4.35 – Program Flash 完成对话框

在此之后,每次循环电路板电源时,都会加载并运行 4 位加法器程序。程序需要很长时间才能加载我们用于加载配置文件的设置。为避免等待FPGA加载程序,您可以通过执行以下步骤来提高配置文件加载的速度:

- 选择打开综合设计 在 流导航器 .

- 在 Vivado 主菜单中,选择 Tools/Edit Device Properties… .

- 在一般 选项卡,设置启用比特流压缩 真 .

- 在配置 选项卡,设置配置速率(MHz) 到 33,然后点击确定 .

- 再次生成比特流,并按照说明对闪存进行编程。您需要移除配置存储设备并将其重新添加回来以显示重新编程选项。

- 关闭硬件 经理 .

- 拔下 Arty 板 USB 电缆并将其插入 程序应该在开机时几乎立即开始运行。

本节介绍了一个简单的组合逻辑与 FPGA I/O 引脚上的信号交互的示例。这里的目的是让您熟悉 Vivado

工具套件,并演示如何使用这些工具来执行完整的 FPGA 开发周期。

总结

本章首先讨论在实时嵌入式系统架构中有效使用 FPGA,然后描述标准 FPGA 设备及其包含的低级组件。介绍了一系列 FPGA 设计语言,包括 HDL、框图方法和流行的软件编程语言,如 C/C++。介绍了 FPGA 开发过程的概要。本章以一个完整的 FPGA 开发周期示例结束,从需求声明开始,以在低成本 FPGA 开发板上实现的功能系统结束。

完成本章后,您应该知道如何在实时嵌入式系统架构中有效地应用 FPGA,并了解 FPGA 集成电路内部的组件。您已经了解了FPGA算法设计中使用的编程语言,FPGA开发周期中的步骤,并了解了FPGA开发过程中的步骤顺序。

下一章将扩展 FPGA 开发过程,以提供构建包含 FPGA 的实时嵌入式系统的完整方法。还将开始开发高性能嵌入式系统原型,即数字示波器,作为后续章节的示例。

经 Packt Publishing 许可转载。版权所有 © 2021 Packt Publishing

吉姆·莱丁 是 Ledin Engineering, Inc. 的首席执行官。Jim 是嵌入式软件和硬件设计、开发和测试方面的专家。他还擅长嵌入式系统网络安全评估和渗透测试。他拥有学士学位爱荷华州立大学航空航天工程学士学位和硕士学位。佐治亚理工学院电气和计算机工程学士学位。 Jim 是加利福尼亚州的注册专业电气工程师、认证信息系统安全专家 (CISSP)、认证道德黑客 (CEH) 和认证渗透测试员 (CPT)。

吉姆·莱丁 是 Ledin Engineering, Inc. 的首席执行官。Jim 是嵌入式软件和硬件设计、开发和测试方面的专家。他还擅长嵌入式系统网络安全评估和渗透测试。他拥有学士学位爱荷华州立大学航空航天工程学士学位和硕士学位。佐治亚理工学院电气和计算机工程学士学位。 Jim 是加利福尼亚州的注册专业电气工程师、认证信息系统安全专家 (CISSP)、认证道德黑客 (CEH) 和认证渗透测试员 (CPT)。 相关内容:

- 使用 FPGA 进行嵌入式设计:硬件资源

- 使用 FPGA 进行嵌入式设计:实现语言

- 使用 FPGA 进行嵌入式设计:开发过程

- 开源工具有助于简化 FPGA 编程

- 在 FPGA 或 ASIC 中实现浮点算法

- 利用 FPGA 进行深度学习

- 软件工具将 GPU 代码迁移到 FPGA 以用于 AI 应用

有关 Embedded 的更多信息,请订阅 Embedded 的每周电子邮件通讯。

嵌入式