什么是控制单元:组件及其设计

控制单元是计算机中中央处理单元 (CPU) 的主要组件,可在处理器/计算机执行程序期间指导操作。控制单元的主要功能是从计算机的内存中获取和执行指令。它接收来自用户的输入指令/信息,并将其转换为控制信号,然后提供给 CPU 以供进一步执行。它作为约翰诺依曼开发的冯诺依曼架构的一部分包含在内。它负责提供时序信号和控制信号,并指导 CPU 执行程序。在现代计算机中,它作为 CPU 的内部部分包含在内。本文描述了有关控制单元的完整信息。

什么是控制单元?

接收来自用户的输入信号/信息/指令并转换为控制信号以在CPU中执行的组件。它控制和指导主存储器、算术和逻辑单元 (ALU)、输入和输出设备,还负责发送到计算机 CPU 的指令。它从处理器的主存中取出指令并发送到处理器指令寄存器,该寄存器包含寄存器内容。

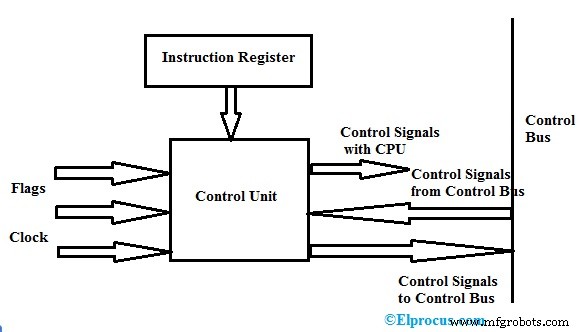

控制单元将输入转换为控制信号,然后发送到处理器并指导程序的执行。必须执行的操作由计算机上的处理器指导。主要是中央处理器(CPU)和图形处理器(GPU)需要一个控制单元作为内部部件。控制单元框图如上所示。

控制单元的组件

该单元的组成部分是指令寄存器、CPU 内的控制信号、进出总线的控制信号、控制总线、输入标志和时钟信号。

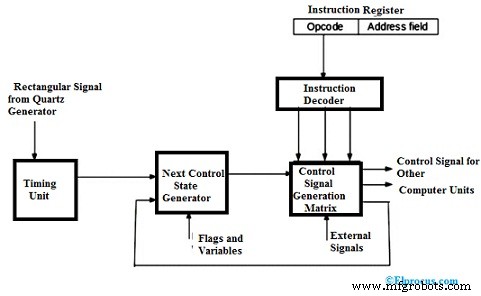

Hardwired控制单元的组成部分是指令寄存器(包含操作码和地址域)、定时单元、控制状态发生器、控制信号产生矩阵和指令译码器。

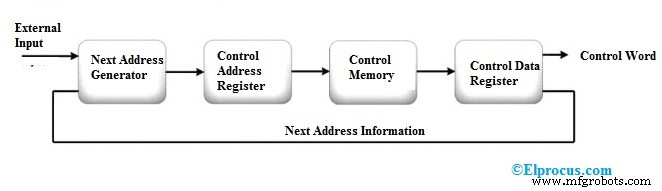

微程序控制单元的组成部分是下一个地址生成器、控制地址寄存器、控制存储器和控制数据寄存器。

功能

控制单元的功能 包括以下内容。

- 它指导处理器和其他设备之间的数据序列流。

- 它可以解释指令并控制处理器中的数据流。

- 它根据接收到的指令或来自指令寄存器的命令生成控制信号序列。

- 它负责控制计算机 CPU 中的 ALU、数据缓冲区和寄存器等执行单元。

- 它具有获取、解码、处理执行和存储结果的能力。

- 它无法处理和存储数据

- 为了传输数据,它与输入和输出设备进行通信并控制计算机的所有单元。

控制单元的设计

可以使用两种类型的控制单元</b>来完成此设计 其中包括以下内容。

- 基于硬线

- 基于微程序(单级和两级)

硬接线控制单元</h4>

硬接线控制单元的基本设计如上所示。在这种类型中,控制信号由特殊的硬件逻辑电路产生,电路结构没有任何变化。在这种情况下,生成的信号不能被修改以在处理器中执行。

操作码的基本数据(指令的操作码被发送到指令解码器进行解码。指令解码器是一组解码器来解码操作码中不同类型的数据。这导致输出信号包含活动信号的值作为输入给矩阵生成器以生成控制信号以供计算机处理器执行程序。

矩阵发生器提供控制单元的状态和从处理器输出的信号(中断信号)。矩阵被构建为可编程逻辑阵列。矩阵发生器产生的控制信号作为下一个发生器矩阵的输入,与包含矩形图案的计时单元的计时信号结合。

为获取新指令,控制单元进入执行新指令的初始阶段。只要计算机的定时信号、输入信号和指令状态不变,控制单元就保持在初始阶段或第一阶段。如果任何生成的信号发生任何变化,都可以引发控制单元的状态变化。

当外部信号或中断发生时,控制单元进入下一状态并执行中断信号的处理。标志和状态用于选择所需的状态来执行指令的执行周期。

在最后状态下,控制单元取出下一条指令并将输出发送到程序计数器,然后到内存地址寄存器,到缓冲寄存器,然后到指令寄存器读取指令。最后,如果最后一条指令(由控制单元取出)为结束指令,则进入处理器工作状态,等待用户指令下一个程序。

微程序控制单元</h4>

在这种类型中,控制存储器用于存储在程序执行期间编码的控制信号。控制信号不会立即生成和解码,因为微程序将地址字段存储在控制存储中。整个过程是一个层次。

微操作是为了执行程序中的微指令。微程序控制单元的框图如上所示。从图中可以看出,微指令的地址是从控制内存地址寄存器中获取的。控制单元的所有信息永久存储在称为ROM的控制存储器中。

来自控制存储器的微指令由控制寄存器保存。由于微指令为控制字形式(包含二进制控制值),需要进行1个或多个微操作才能进行数据处理。

在微指令执行过程中,下一个地址生成器计算出微指令的下一个地址,然后发送到控制地址寄存器读取下一条微指令。

微指令的微操作顺序-program由下一个地址生成器执行,并作为微程序定序器获取序列地址,即从控制存储器中读取。

控制单元的 Verilog 代码

控制单元的 Verilog 代码如下所示。

`包括“prj_definition.v”

模块 CONTROL_UNIT(MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, R_LUERRESTP>, RCLK_DATA_R2

// 输出信号

// 寄存器文件的输出

output [`DATA_INDEX_LIMIT:0] RF_DATA_W;

output [`ADDRESS_INDEX_LIMIT:0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

output RF_READ, RF_WRITE;

// ALU的输出

output [`DATA_INDEX_LIMIT:0] ALU_OP1, ALU_OP2;

output [`ALU_OPRN_INDEX_LIMIT:0] ALU_OPRN;

// 内存输出

output [`ADDRESS_INDEX_LIMIT:0] MEM_ADDR;

output MEM_READ, MEM_WRITE;

// 输入信号

input [`DATA_INDEX_LIMIT:0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT;

input ZERO, CLK, RST;

// 输入信号

输入[`DATA_INDEX_LIMIT:0] MEM_DATA;

// 状态网络

wire [2:0] proc_state;

//保存程序计数器值,存储当前指令,堆栈指针寄存器

reg MEM_READ, MEM_WRITE;

reg MEM_ADDR;

reg ALU_OP1, ALU_OP2;

reg ALU_OPRN;

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

reg RF_DATA_W;

reg [1:0] state, next_state;

PROC_SM state_machine(.STATE(proc_state),.CLK(CLK),.RST(RST));

always @ (posedge CLK)

begin

if (RST)

state <=RST;

else

state <=next_state;

结束

总是@(状态)

开始

MEM_READ =1'b0; MEM_WRITE =1'b0; MEM_ADDR =1'b0;

ALU_OP1 =1'b0; ALU_OP2 =1'b0; ALU_OPRN =1'b0;

RF_ADDR_R1 =1'b0; RF_ADDR_R2 =1’b0; RF_ADDR_W =1’b0; RF_DATA_W =1’b0;

案例(状态)

`PROC_FETCH :begin

next_state =`PROC_DECODE;

MEM_READ =1'b1;

RF_ADDR_R1 =1'b0; RF_ADDR_R2 =1'b0;

RF_ADDR_W =1'b1;

end

`PROC_DECODE :begin

next_state =`PROC_EXE;

MEM_ADDR =1'b1;

ALU_OP1 =1'b1; ALU_OP2 =1'b1; ALU_OPRN =1'b1;

MEM_WRITE =1'b1;

RF_ADDR_R1 =1'b1; RF_ADDR_R2 =1'b1;

end

`PROC_EXE :begin

next_state =`PROC_MEM;

ALU_OP1 =1'b1; ALU_OP2 =1'b1; ALU_OPRN =1'b1;

RF_ADDR_R1 =1'b0;

end

`PROC_MEM:begin

next_state =`PROC_WB;

MEM_READ =1'b1; MEM_WRITE =1'b0;

end

`PROC_WB:begin

next_state =`PROC_FETCH;

MEM_READ =1'b1; MEM_WRITE =1'b0;

end

endcase

结束

结束模块;

module PROC_SM(STATE,CLK,RST);

//输入列表

input CLK, RST;

//输出列表

output [2:0] STATE;

// 输入列表

input CLK, RST;

// 输出列表

output STATE;

reg [2:0] 状态;

reg [1:0] 状态;

reg [1:0] next_state;

reg PC_REG, INST_REG, SP_REF;

`define PROC_FETCH 3'h0

`define PROC_DECODE 3'h1

`define PROC_EXE 3'h2

`define PROC_MEM 3'h3

`define PROC_WB 3'h4

// 状态初始化

initial

begin

state =2'bxx;

next_state =`PROC_FETCH;

end

// 重置信号处理

always @ (posedge RST)

begin

state =`PROC_FETCH;

next_state =`PROC_FETCH;

end

always @ ( posedge CLK)

begin

state =next_state;

end

总是@(state)

begin

if (state ===`PROC_FETCH)

开始

next_state =`PROC_DECODE;

打印指令(INST_REG);

结束

if (state ===`PROC_DECODE)

begin

next_state =`PROC_EXE;

结束

if (state ===`PROC_EXE)

begin

next_state =`PROC_MEM;

打印指令(SP_REF);

结束

if (state ===`PROC_MEM)

begin

next_state =`PROC_WB;

结束

if (state ===`PROC_WB)

begin

next_state =`PROC_FETCH;

打印指令(PC_REG);

end

end

任务打印指令;

输入 [`DATA_INDEX_LIMIT:0] inst;

reg [5:0] 操作码;

reg [4:0] rs;

reg [4:0] rt;

reg [4:0] rd;

reg [ 4:0] 假的; reg [5:0] 函数; reg [15:0] 立即; reg [25:0] 地址;

开始

// 解析指令

// R-type

{操作码,rs,rt,rd,shamt,funct} =inst;

// I-type

{opcode, rs, rt,immediate } =inst;

// J-type

{opcode, address} =inst;

$write(“ @ %6dns -> [0X%08h] ", $time, inst);

case(opcode) // R-Type

6'h00 :begin

case(funct)

6'h20:$write("add r[%02d], r[%02d], r[%02d];", rs, rt, rd);

6'h22:$write("sub r [%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h2c:$write(“mul r[%02d], r[%02d] , r[%02d];”, rs, rt, rd);

6'h24:$write(“and r[%02d], r[%02d], r[%02d];”, rs , rt, rd);

6'h25:$write(“or r[%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h27:$write(“nor r[%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h2a:$write(“slt r [%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h00:$write(“sll r[%02d], %2d, r[ %02d];”, rs, shamt, rd);

6'h02:$write(“srl r[%02d], 0X%02h, r[%02d];”, rs, shamt, rd);

6'h08:$write(“jr r[%02d];”, rs);

默认值:$write(“”);

endcase

end

// I型

6'h08 :$write(“addi r[%02d], r[%02d], 0X%04h;”, rs, rt,immediate);

6'h1d :$write(“muli r[% 02d], r[%02d], 0X%04h;”, rs, rt,immediate);

6'h0c :$write(“andi r[%02d], r[%02d], 0X%04h;", rs, rt, 立即数);

6'h0d :$write("ori r[%02d], r[%02d], 0X%04h;", rs, rt, 立即数);

6'h0f :$write(“lui r[%02d], 0X%04h;”, rt,immediate);

6'h0a :$write(“slti r[%02d], r[% 02d], 0X%04h;", rs, rt, 立即数);

6'h04 :$write("beq r[%02d], r[%02d], 0X%04h;", rs, rt , 立即数);

6'h05 :$write(“bne r[%02d], r[%02d], 0X%04h;”, rs, rt, 立即数);

6'h23 :$write(“lw r[%02d], r[%02d], 0X%04h;”, rs, rt, 立即数);

6'h2b :$write(“sw r[%02d], r [%02d], 0X%04h;”, rs, rt, 立即数);

// J型

6'h02 :$write(“jmp 0X%07h;”, address);

6'h03 :$write(“jal 0X%07h;”, address);

6'h1b :$write (“push;”);

6'h1c :$write(“pop;”);

default:$write(“”);

endcase

$write (“ \n”);

end

endtask

end 模块;

常见问题解答

1)。控制单元的工作是什么?

控制单元的工作是指导数据或指令的流动,以便由计算机的处理器执行。它控制、管理和协调主存储器、ALU、寄存器、输入和输出单元。它获取指令并生成用于执行的控制信号。

2)。什么是控制内存?

控制存储器通常为RAM或ROM,用于存储控制寄存器的地址和数据。

3)。什么是威尔克斯控制单元?

硬连线控制单元的时序和组合电路被 Wilkes 控制单元所取代。它使用一个存储单元来存储微程序的指令序列。

4)。什么是硬连线控制单元?

硬连线控制单元通过在每个时钟脉冲中从一种状态变为另一种状态来生成控制信号,电路中没有任何物理变化。控制信号的产生依赖于指令寄存器、解码器和中断信号。

5)。什么是控制内存?

控制单元的信息或数据临时或永久地存储在控制存储器中。

控制存储器有两种类型。它们是随机存取存储器(RAM)和只读存储器(ROM)。

因此,这完全是关于控制单元的定义、组件、设计、图表、功能和类型。这里有一个问题,“控制地址寄存器的目的是什么?”

嵌入式