低成本交叉处理器支持端点推断

英国布里斯托尔——XMOS 已将其 Xcore 处理器内核用于机器学习,为 AIoT 应用创建了一个跨界处理器。 Xcore.ai 的售价为 1 美元。

Xcore.ai是基于公司专有核心设计的第三代产品,专为终端设备中的实时AI推理和决策而设计,还可以处理信号处理、控制和通信功能。

这款第三代芯片的新功能是用于机器学习应用程序的矢量流水线功能。它是同类中唯一支持二值化(1 位)神经网络的跨界处理器,这些网络对于端点应用中的超低功耗 AI 越来越重要,因为它们在性能和内存密度方面提供了数量级的改进适度降低准确性(Xcore.ai 还支持 32 位、16 位和 8 位数字)。

Xcore.ai 加入了一类新的具有 AI 功能的芯片系统,用于端点应用,即跨界处理器(图片:XMOS)

Xcore.ai 加入了具有 AI 功能的新兴端点处理器类别,即交叉处理器。该术语由恩智浦创造,描述了一类重要的新型设备,它具有应用处理器的性能,以及微控制器的易用性、低功耗和实时操作。

“如果您与客户谈论‘微控制器’,他们会想到价格为 75 美分或更低,性能相对较低,大约为 100 MIPS 的 Cortex-M0、M3 或 M4 设备。那么“SoC”可能是带有四核 A53 内核的东西,以千兆赫兹运行。中间的东西有很大的差距,比如语音处理器,这是一个特别困难的数学问题,需要数千 MIPS。 XMOS 首席执行官马克·利佩特 (Mark Lippett) 在接受 EETimes 专访时表示,因此与一个非常重要且非常重要的应用领域之间存在着巨大的差距,它值得拥有一个名字。

语音界面

该公司之前宣布的第二代产品 XVF3510 于 2019 年 7 月作为语音接口的 ASIC 推出,但芯片内部也基于该公司专有的 Xcore 设计,随附固件。基于 XVF3510 的远场语音解决方案参考设计符合亚马逊 Alexa 语音服务的要求。

鉴于 XMOS 在语音领域的历史,Xcore.ai 芯片最初将定位于需要 AI 进行关键字检测或字典功能的语音接口应用也就不足为奇了。

“让我们绝对清楚,语音是端点最重要的 AI 工作负载,并且可能在未来相当长一段时间内仍然如此。但是为了让语音界面变得更好,你会发现设备将变得更加多模态,”Lippett 说,他描述了一种趋势,即使用不同类型的传感器使应用程序更具上下文感知能力,无论是检测人的存在还是检测位置他们来自。

Mark Lippett(图片:XMOS)

“不仅可以通过聆听音频,还可以通过做更多的事情来改善用户体验,”他说。

人工智能在物联网设备中的许多应用取决于隐私、安全和安全的组合,需要在端点进行处理。 Lippett 描述了使用语音和雷达来关闭烤箱的电器的安全功能,例如,如果厨房里只有孩子。

因此,Xcore.ai 将提供用于创建语音接口的库进入市场,但利佩特表示,它有闲置容量供客户构建自己的系统。相机输入包含MIPI接口。

Xcore 架构

Xcore.ai 芯片可提供高达 3200 MIPS、51.2 GMACC 和 1600 MFLOPS。它具有1 MB的嵌入式SRAM和一个用于扩展的低功耗DDR接口。

与提供与 Xcore.ai 大致相同的集成水平、以相似的工作频率运行的 Cortex-M7 设备相比,XMOS 自己的数据表明其 AI 处理性能提高了 32 倍,DSP 性能提高了 15 倍。

“在端点世界中,它必须是性价比,没有其他的谈论一个没有意义,”利佩特说。 “我们在价格上非常激进,我们可以将这部分 [in volume] 降到 1 美元。从广义上讲,我们的成本大约是 [可比 Cortex-M7 设备] 的一半,而且在性能方面我们正在把它吹走。”

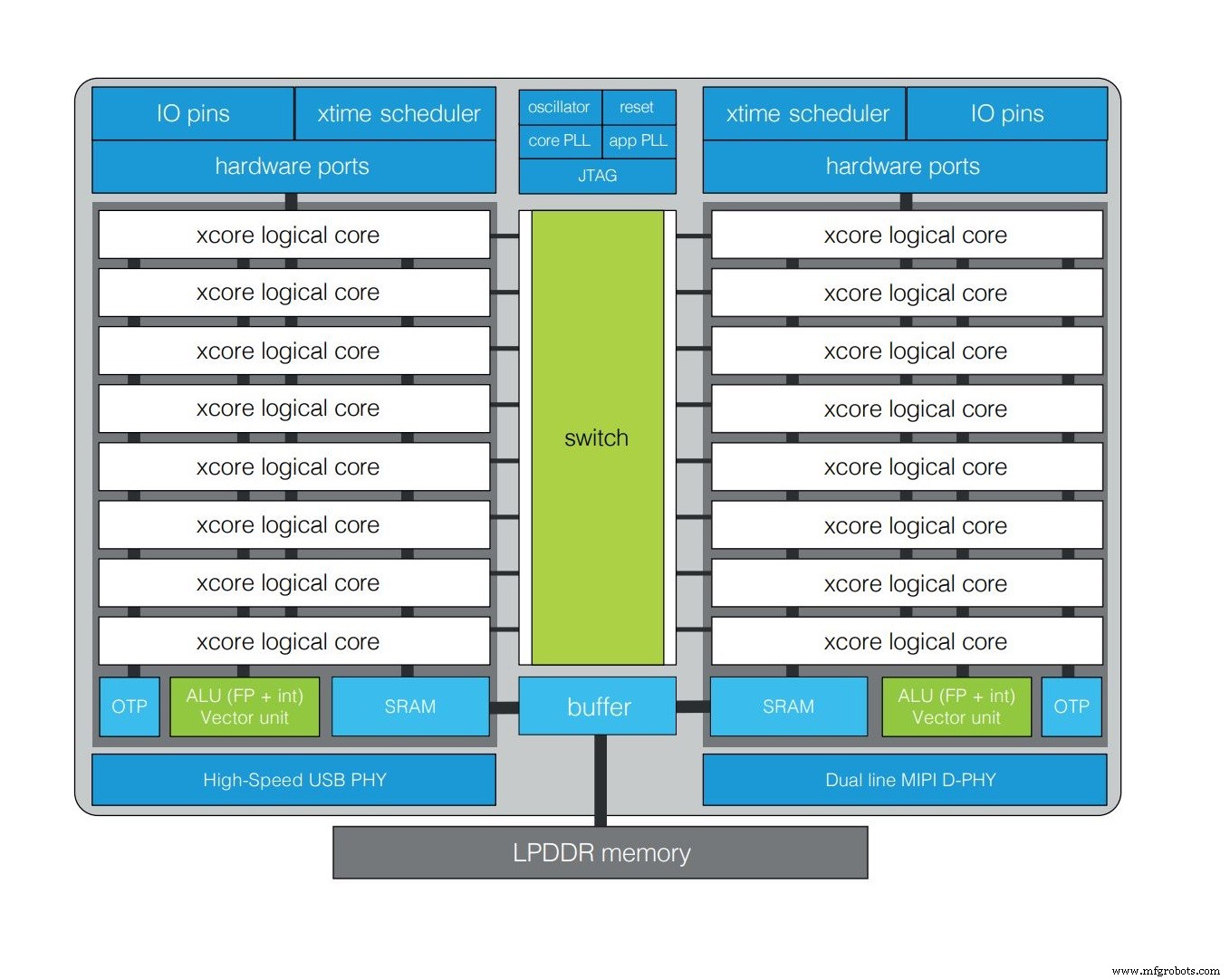

Xcore 基于以磁贴排列的逻辑核心和内存,

ALU 和向量单元(图片:XMOS)

Xcore.ai 基于 XMOS 专有的 Xcore 架构。 Xcore 本身建立在称为逻辑核心的构建块上,可用于 I/O、DSP、控制功能或 AI 加速。每个磁贴上有八个逻辑内核,每个 Xcore.ai 芯片中有两个磁贴,设计人员可以选择为每个功能分配多少个内核。每个 tile 还包含内存、ALU 和逻辑内核共享访问的向量单元。

“至关重要的是,他们以一种非常可预测的方式 [共享访问权限],”利佩特说。 “这就是 Xcore 的特别之处。最初,我们希望为软件工程师提供 I/O 灵活性,如果您错过最后期限,硬件就不是很宽容。所以 Xcore 是多核的,不是因为我们想分出工作负载并很快地做事——我们可以做到——但实际上它是多核的,因为我们想为应用程序的特定部分提供自己的资源,这样当它是需要的,它已经准备好了。它是自下而上设计的,旨在提供这种计时精度。”

将不同的功能(I/O、DSP、控制、AI)映射到固件中的逻辑内核,可以创建完全用软件编写的“虚拟 SoC”。在下面的示例中,一个内核正在执行通常在硬件中完成的任务,例如 I 2 S, I 2 C 和 LED 驱动器以及一些内核正在处理神经网络,而其他内核正在执行通常在软件中完成的任务。在软件中定义所有这些更快,以满足物联网设备的瞬态需求。 Lippett 说,开发成本也更低,这使公司能够创建即使在较小的细分市场中也很经济的解决方案。

映射到 Xcore.ai 设备的示例应用程序(图片:XMOS)

“我们看到市场发展的方式是,市场需要更多样化的功能,公司需要更快地做出反应,”利佩特说。 “如果不构建一个非常通用的平台,可能 [最终] 对任何细分市场都不够好,就很难在物联网上押下两年的赌注。 [使用 Xcore.ai],可以更轻松地以更少的资本支出更快地将设备推向市场,并有效地在较小的市场上进行较小的赌注,并使这些市场变得经济。”

XMOS 将如何与进入这一跨界处理器领域的大型微控制器制造商竞争?

“不是通过构建基于 ARM 的 SoC!因为他们做得非常好,”利佩特说。 “与这些人竞争的唯一方法是拥有建筑优势。这与 Xcore 在性能和灵活性方面的内在能力有关。”

嵌入式