CXL 2.0 /PCIe 5.0 解决方案解锁异构计算和数据瓶颈

Fabless 半导体初创公司 Astera Labs 宣布了一种新的专门构建的 CXL 2.0 和 PCIe 5.0 连接解决方案,以解锁异构计算架构并解决数据中心中对延迟敏感的工作负载。该公司表示,这些新解决方案旨在解决以数据为中心的应用程序中的系统范围性能瓶颈。

数据的激增和专业工作负载的主流化——如人工智能 (AI) 和机器学习 (ML)——需要专用加速器与同一主板上或同一机架内的通用 CPU 并行工作,同时共享公共内存空间。 CXL 2.0 互连是实现此类缓存一致性系统拓扑的关键。

Astera Labs 新产品组合中的第一款产品是用于低延迟 CXL.io 连接的 Aries Compute Express Link (CXL 2.0) 智能重定时器产品组合(PT5161LX、PT5081LX),目前正在积极向战略客户提供样品。该公司首席执行官 Jitendra Mohan 表示:“随着我们扩展到 CXL 生态系统,Astera Labs 正在迈出又一大步,提供专门构建的解决方案,以解锁复杂的异构计算和可组合的分解系统拓扑结构。”

CXL 2.0 规范由 CXL 联盟于 2020 年 11 月发布。CXL 是一种开放的行业标准互连,使用主机处理器和加速器、内存缓冲区和智能设备等设备之间的高带宽、低延迟连接提供一致性和内存语义。输入/输出设备。 CXL 2.0 规范增加了对扇出切换的支持,以连接更多设备;内存池以提高内存利用效率并按需提供内存容量;并支持持久内存。所有这一切都是通过支持与 CXL 1.1 和 1.0 的完全向后兼容性来保护行业投资的。

CXL 联盟主席 Barry McAuliffe 表示:“作为 CXL 联盟的早期成员,Astera Labs 为 CXL 标准的进步贡献了其连接专业知识。很高兴看到其首个 CXL 芯片实现上市以支持快速增长的 CXL 生态系统。”

与英特尔合作的全新 PCIe 5.0 解决方案

Astera Labs 还宣布在其 Aries 智能重定时器产品组合中推出一种新的低延迟模式,用于与英特尔至强可扩展处理器的 PCIe 连接。这一发展是与英特尔公司密切合作的结果,旨在进一步将 PCIe 链接的延迟降低到 10 纳秒以下,并提高以数据为中心的工作负载的性能。 Astera Labs 声称它是第一家展示强大的 PCIe 5.0 与代号为“Sapphire Rapids”的英特尔至强可扩展处理器的互操作性的供应商。

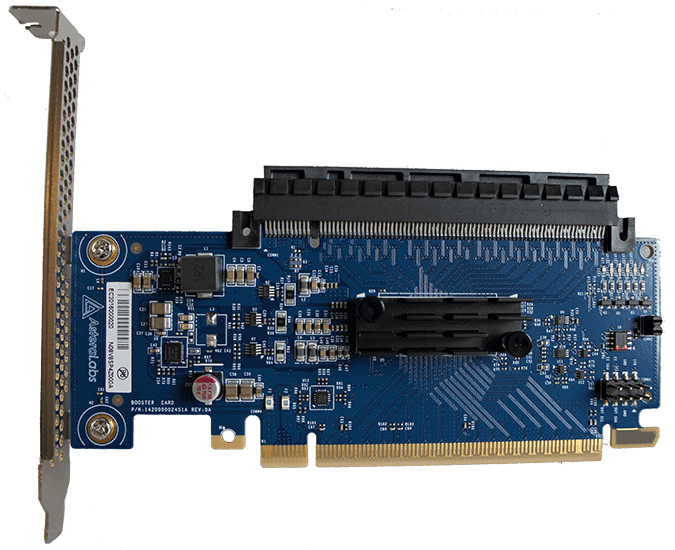

同时推出的还有一款用于 PCIe/CXL 应用的新型即插即用智能重定时器插件卡,称为 Equinox。同样与英特尔合作开发的卡和相关的专用固件将使用英特尔最新的至强可扩展处理器简化支持 PCIe 5.0 的系统的开发。这代表 Astera Labs 向提供易于使用的即插即用板以快速实施复杂的系统拓扑结构的转变。

“PCIe Gen5 和 CXL 是当今和未来异构计算工作负载和数据中心架构的基础技术,”英特尔公司副总裁兼数据中心工程和架构总经理 Zane Ball 说。 “英特尔正在与 Astera Labs 等生态系统领导者合作,以显着降低即将推出的代号为‘Sapphire Rapids’的英特尔至强可扩展平台和其他平台上的 PCIe 和 CXL 互连延迟。”

相关内容:

- 通过 USB-C 重新定时 USB4

- 使用多代 PCIe 构建高性能互连

- Xilinx 旨在通过“可组合”硬件实现数据中心卸载

- 边缘超级计算将如何改变巨大的数据洪流

嵌入式

- 云计算中的法律问题及其解决方案

- DATA MODUL:ISE 上展示的面向客户的数字标牌解决方案

- Microchip:时钟缓冲器符合 DB2000Q/QL 标准以及 PCIe Gen 4 和 5 低抖动规范

- 宇瞻:PCIe NVMe Gen3 SSD,工业级存储的下一个合乎逻辑的步骤

- Swissbit:用于保护数据和设备的基于硬件的安全解决方案

- TECHWAY:Kintex-7 FPGA PCIe 平台通过 12 个 HSS 链接提高数据速率性能

- 陆军基于状态维护的策略和解决方案

- 为 EHS 调整 IIoT 和数据分析解决方案的好处

- 利用物联网网络解决方案抗击城市地区的洪水

- 物联网如何改变供应链:第 2 部分,未来解决方案

- Electronic Design 正在利用支持 AI 的解决方案提供一流的服务

- 通过性能监控释放物联网的价值