D 锁存器

触发器在时钟的上升沿或下降沿在其输入端捕获数据。需要注意的重要一点是,在时钟沿之后直到下一个时钟沿发生的任何数据都不会反映在输出中。一个闩锁 另一方面,不会在时钟边缘捕获,而是只要使能引脚被置位,输出就会跟随输入。

设计

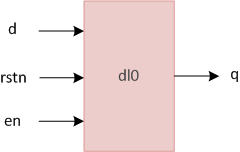

在此示例中,我们将构建一个具有三个输入和一个输出的锁存器。输入 d 代表可以是0或1的数据,rstn 代表低电平有效复位和en 代表使能,用于使输入数据锁存到输出。复位为低电平有效意味着当该输入变为 0 时设计元素将被复位,换句话说,当其值为低时复位有效。输出q的值 由输入 d 决定 , zh 和 rstn .

<无脚本>

module d_latch ( input d, // 1-bit input pin for data

input en, // 1-bit input pin for enabling the latch

input rstn, // 1-bit input pin for active-low reset

output reg q); // 1-bit output pin for data output

// This always block is "always" triggered whenever en/rstn/d changes

// If reset is asserted then output will be zero

// Else as long as enable is high, output q follows input d

always @ (en or rstn or d)

if (!rstn)

q <= 0;

else

if (en)

q <= d;

endmodule

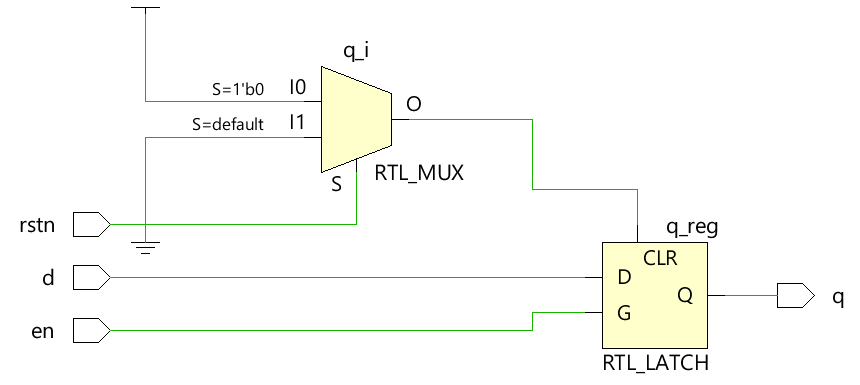

请注意,always 的敏感度列表 块包含更新输出所需的所有信号。每当敏感度列表中的任何信号更改其值时,都会触发此块。还有q 只有当 en 时才会得到 d 的值 很高,因此是一个积极的 闩锁。

示意图

<无脚本>

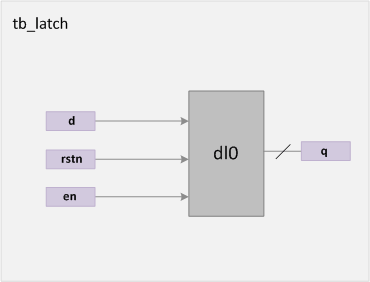

测试台

<无脚本>

module tb_latch;

// Declare variables that can be used to drive values to the design

reg d;

reg en;

reg rstn;

reg [2:0] delay;

reg [1:0] delay2;

integer i;

// Instantiate design and connect design ports with TB signals

d_latch dl0 ( .d (d),

.en (en),

.rstn (rstn),

.q (q));

// This initial block forms the stimulus to test the design

initial begin

$monitor ("[%0t] en=%0b d=%0b q=%0b", $time, en, d, q);

// 1. Initialize testbench variables

d <= 0;

en <= 0;

rstn <= 0;

// 2. Release reset

#10 rstn <= 1;

// 3. Randomly change d and enable

for (i = 0; i < 5; i=i+1) begin

delay = $random;

delay2 = $random;

#(delay2) en <= ~en;

#(delay) d <= i;

end

end

endmodule

为了让我们的测试台以更随机的方式断言和取消断言信号,我们声明了一个 reg 名为延迟的变量 大小为 3 位,因此它可以取 0 到 7 之间的任何值。然后 延迟 变量用于延迟d的赋值 和 zh 在每个循环中获得不同的模式。

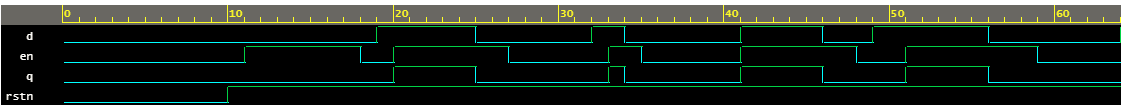

输出

模拟日志ncsim> run [0] en=0 d=0 q=0 [11] en=1 d=0 q=0 [18] en=0 d=0 q=0 [19] en=0 d=1 q=0 [20] en=1 d=1 q=1 [25] en=1 d=0 q=0 [27] en=0 d=0 q=0 [32] en=0 d=1 q=0 [33] en=1 d=1 q=1 [34] en=1 d=0 q=0 ncsim: *W,RNQUIE: Simulation is complete.

点击图片放大。

<无脚本>

Verilog