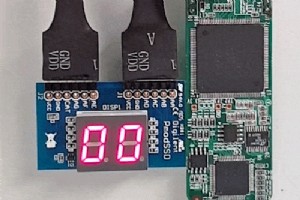

在本文中,我将介绍一个可以在 Pmod SSD 上显示两位数的 VHDL 模块:来自 Digilent 的七段显示器。双 7 段显示器与 Pmod 接口兼容,这意味着您无需任何焊接即可使用它。它适合 Pmod 连接器,这是许多 FPGA 开发板的标准配置。 为了测试 VHDL 实现,我使用了 Lattice iCEstick,这是一款带有 Pmod 连接器的低成本 FPGA 开发板。除了 iCEstick 之外,您还需要一根 2×6 针转双 6 针 Pmod 分路器电缆,将 iCEstick 上的并行 Pmod 连接器转换为 7 段显示器所需的串联版本插头。最后,我建议使用 USB Type

* 本文包含 UpCloud VPS 的广告链接 持续交付和持续集成是敏捷的软件开发方法,可以缩短代码更改和部署之间的周期时间。通过使用自动化来验证代码更改并构建发布文件,团队可以变得更加高效。 软件公司长期以来一直实行持续开发,但您也可以将这些方法用于您的 FPGA 项目。本教程将教您如何使用 Jenkins、Xilinx Vivado 和 Git / GitHub 源代码控制管理 (SCM) 系统在虚拟专用服务器 (VPS) 上设置自动化服务器。 什么是詹金斯? Jenkins 自动化服务器是一个用 Java 编写的免费开源程序。它在 Windows 或 Linux 上运行。我们将

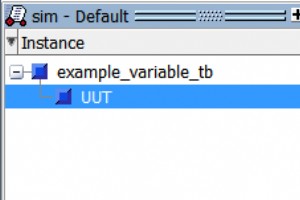

如何查看仿真波形上的 VHDL 变量 Modelsim 有一种方法可以在仿真过程中查看 VHDL 变量,但是这并不容易做到。在 Modelsim 中,对象 窗口从不显示变量。 Modelsim 对象窗口,无变量 可以通过首先显示进程来启用变量。这是通过右键单击要查看其变量的设计来完成的。向下转到显示 ,并检查进程 正在展示。 如何查看设计中的流程 完成后,您的设计将在其下方显示流程名称(这就是为什么最好标记流程的原因之一)。 流程可见 现在您需要查看本地人 。变量是局部变量,因为它不存在于创建它的进程之外。它对于一个进程来说是本地的。这是在视图中完成的 Modelsi

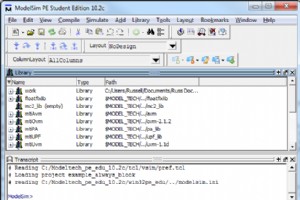

教程 - 使用 Modelsim 进行仿真,适合初学者。 Modelsim 是由 Mentor Graphics 创建的程序,用于模拟 VHDL 和 Verilog 设计。它是商业和教育领域使用最广泛的模拟程序。本教程首先解释为什么仿真很重要,然后展示如何免费获取 Modelsim Student Edition 供个人使用。 仿真是设计 FPGA 和 ASIC 的关键步骤。模拟允许设计者刺激他或她的设计并查看他们编写的代码如何对刺激做出反应。出色的模拟将演练设计的所有可能状态,以确保所有输入场景都得到适当处理。您是否在某处忘记了 if 语句?您是否记得分配所有可能的案例陈述?当您不对设计

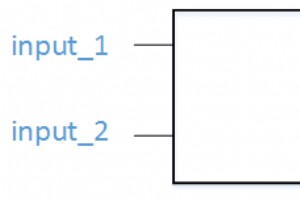

教程 - VHDL 简介 VHDL 是一个可怕的缩写。它代表V HSIC H 硬件D 描述L 语言。首字母缩略词里面有首字母缩略词,太棒了! VHSIC 代表 V 非常H 哎呀S 撒尿I 集成C 电路。因此,VHDL扩展为V 超高速集成电路H 硬件D 描述L 语言。唷,这真是太拗口了。 VHDL 是教育和企业用来设计 FPGA 和 ASIC 的两种语言之一。如果您不熟悉这些迷人的电路,您可能首先会从 FPGA 和 ASIC 简介中受益。 VHDL 和 Verilog 是数字设计人员用来描述电路的两种语言,它们在设计上与 C 和 Java 等传统软件语言不同。 对于下面的示例,我们将创建一个

总之,VHDL是一种用于设计数字电路的计算机语言。 我使用术语“计算机语言”来区分 VHDL 与其他更常见的编程语言,如 Java 或 C++。但是 VHDL 是一种编程语言吗?是的。它是一种编程语言,在创建计算机程序时毫无用处! VHDL 是一种事件驱动的并行编程语言。虽然它不适合创建可由计算机上的 CPU 运行的程序,但它非常适合创建实际的 CPU。它是一种硬件描述语言,这意味着它可以用于设计数字逻辑。 在此处访问基本 VHDL 教程系列! 考虑上面的插图。 CPU芯片内部有很多很多主要是数字电子电路(中间)。这些数字电路可以使用示意图(右)来显示。在创建集成电路芯

尽管 VHDL 和 FPGA 工具通常非常昂贵,但如果您是学生,则可以轻松免费访问最先进的软件。有几个模拟器、编辑器和 IDE 可用于使用 VHDL。本文将向您展示如何安装 VHDL 工程师最常用的两个程序。 VHDL 模拟器 Siemens EDA(前身为 Mentor Graphics)的 ModelSim 是目前最常见的 VHDL 仿真器,在您的第一个 VHDL 工作中,您可能必须使用 ModelSim 或程序的 QuestaSim 风格。使您的代码尽可能可移植是一种很好的设计实践,本博客中的代码也不例外。如果您可以访问另一个 VHDL 模拟器,请继续使用它;它应该类似地工作。 VH

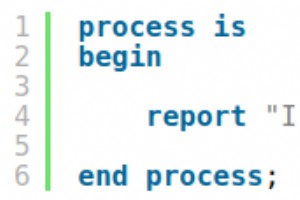

在学习一门新的编程语言时,我总是喜欢从学习如何打印开始。当你掌握输出“Hello World!”时,你就知道你已经让环境工作了。它还向您展示了该语言的基本框架,即产生任何输出所需的最少代码。 你可能会想:但 VHDL 是一种硬件描述语言,它怎么能输出任何文本呢?你需要一个连接到 FPGA 或其他东西的屏幕,以及介于两者之间的各种逻辑,这一点都不简单。虽然这一切都是真的,但让我们暂时忘掉 FPGA 和 ASIC,把注意力集中在 VHDL 语言上。 这篇博文是基本 VHDL 教程系列的一部分。 VHDL可以被认为是一种并行编程语言,因此我们可以使用这种程序员的方法来学习它。由于我们使用该语

在前面的教程中,我们了解到可以将进程视为程序线程。我们还了解到 wait; 语句导致程序无限期暂停。但是有没有办法让程序等待任何其他时间值而不是永远? 如果我们删除 wait; 完全并尝试编译程序,编译器会抱怨无限循环。编译器所指的循环是进程循环 . VHDL 中的进程线程永远不会终止,它会在 begin 之间不断循环 和 end process; 陈述。必须有一个 wait 在进程循环内的某处声明。 这篇博文是基本 VHDL 教程系列的一部分。 而 wait; 将导致程序永远暂停,wait for 语句可用于将程序延迟任意时间。 wait for 的语法 语句为:wait for

在上一个教程中,我们学习了如何使用 wait for 来延迟时间 陈述。我们还了解了流程循环。我们现在知道,如果我们让它,进程“线程”将永远在进程中循环。 但是,如果我们只想在流程开始时做一次事情怎么办?然后在最后循环一些其他代码? VHDL 中最简单的循环可以使用 loop 创建 声明。 这篇博文是基本 VHDL 教程系列的一部分。 简单循环的语法是: loopend loop; 这样的循环将无限期地继续,或者直到 exit; 遇到。 exit 语句可用于跳出任何循环。 运动 这个视频教程教你如何创建一个简单的循环,以及如何打破它: 我们在本教程中创建的最终代码: ent

在上一个教程中,我们学习了使用 loop 创建无限循环 陈述。我们还学习了如何使用 exit 跳出循环 陈述。但是,如果我们希望循环迭代一定次数怎么办? For-Loop 是完成此任务的最简单方法。 For-Loop 允许您迭代固定范围的整数或枚举项。属于当前迭代的项目将通过隐式声明的常量在循环内可用。 这篇博文是基本 VHDL 教程系列的一部分。 For-Loop的语法是: for <c> in <r> loopend loop; <c> 是在循环内可用的常量的任意名称。 <r> 是循环将迭代的整数范围或枚举值。整数范围可以递增也可

在之前的教程中,我们学习了如何使用 For 循环遍历整数范围。但是,如果我们想要对循环进行更详细的控制而不仅仅是一个固定的整数范围呢?我们可以为此使用 While-Loop。 只要它测试的表达式计算结果为 true,While 循环就会继续迭代封闭的代码 .因此,While-Loop 适用于事先不知道具体需要多少次迭代的情况。 这篇博文是基本 VHDL 教程系列的一部分。 While-Loop 的语法是: while <condition> loopend loop; <condition> 是一个布尔值 true 或 false .它也可以是计算结果为 tr

至此,您已经完成了 Basic VHDL Tutorial 系列的第一部分。恭喜!您距离成为真正的 VHDL 高手只有几个小时和几个小时的时间。但是你已经完成了第一步,这是现在最重要的部分! 在我们继续之前,您应该通过这个测验来测试您的技能: 这个过程有什么问题? 它包含没有等待语句 缺少分号在“过程是”之后 流程没有输入 正确的!错误的! - “i”的值将被打印多少次? 无限数次数 零 一次 正确的!错误的! - 这个过程会打印多少次“哈哈!”? 总是 10次 总是 11次 取决于我们模拟了多长时间 正确的!错误的!

在之前的教程中,我们学习了如何在进程中声明变量。变量有利于在流程中创建算法,但外部世界无法访问它们。如果变量的范围仅在单个进程内,它如何与任何其他逻辑交互?解决方案是信号 . 信号在 architecture <architecture_name> of <entity_name> is 之间声明 行和 begin VHDL 文件中的语句。这被称为架构的声明部分。 这篇博文是基本 VHDL 教程系列的一部分。 声明信号的语法是:signal <name> : <type>; 可以选择使用初始值声明信号:signal <name&

在上一教程中,我们了解了信号和变量之间的主要区别。我们了解到,信号比变量具有更广泛的范围,变量只能在一个进程中访问。那么我们如何使用信号在多个进程之间进行通信呢? 我们已经学会使用wait; 无限等待,wait for 等待特定的时间。 VHDL中还有两种等待语句。 这篇博文是基本 VHDL 教程系列的一部分。 Wait On 语句将暂停进程,直到指定信号之一发生变化:wait on <signal_name1>, <signal_name2> ...; Wait Until 语句将暂停,直到某个事件导致条件变为真:wait until <condit

在之前的教程中,我们使用了带有 Wait Until 语句的条件表达式。该表达式确保仅当两个计数器信号相等时才触发该过程。但是如果我们希望进程中的程序根据不同的输入采取不同的动作呢? If-Then-Elsif-Else 语句可用于在我们的程序中创建分支。根据变量的值或表达式的结果,程序可以采用不同的路径。 这篇博文是基本 VHDL 教程系列的一部分。 基本语法是: if <condition> then elsif <condition> then else end if; elsif 和 else 是可选的,elsif 可以多次使用。 <cond

您应该始终使用敏感度列表 触发生产模块中的流程。敏感度列表是一个进程的参数,它列出了该进程对其敏感的所有信号。如果任何一个信号发生变化,进程就会被唤醒,并执行其中的代码。 我们已经学会使用 wait on 和 wait until 用于在信号更改时唤醒进程的语句。但是,说实话,这不是我编写大部分流程的方式。 这篇博文是基本 VHDL 教程系列的一部分。 编写 VHDL 代码时,编写方式取决于代码是否仅打算在模拟器中运行。如果我正在编写模拟代码,就像我们在本教程系列中所做的那样,我总是 使用 wait 用于控制进程的语句。如果我正在编写我打算创建物理实现的代码,我从不 使用 wait 声

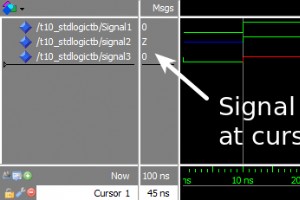

VHDL 中最常用的类型是 std_logic .将此类型视为单个位,即由单个物理线路承载的数字信息。 std_logic 比 integer 让我们对设计中的资源进行更细粒度的控制 type,我们在之前的教程中一直在使用。 通常,我们希望数字接口中的线具有值 1 或 0 .这两个值是位(二进制数字)可以具有的唯一值。但实际上,物理数字信号可以处于多种状态,std_logic type 可以很好地模拟。因此它是VHDL中最常用的类型。 这篇博文是基本 VHDL 教程系列的一部分。 std_logic type 可以有以下值: ‘1’ 逻辑1 ‘0’ 逻辑 0 ‘Z’ 高阻抗

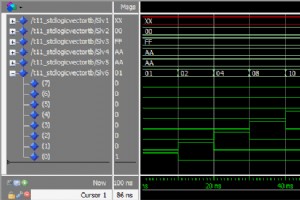

std_logic_vector type 可用于在 VHDL 中创建信号总线。 std_logic 是VHDL中最常用的类型,std_logic_vector 是它的数组版本。 而 std_logic 非常适合对单根导线可以承载的值进行建模,但对于实现进出组件的导线集合并不是很实用。 std_logic_vector 是复合类型,这意味着它是子元素的集合。 std_logic_vector 的信号或变量 type 可以包含任意数量的 std_logic 元素。 这篇博文是基本 VHDL 教程系列的一部分。 声明 std_logic_vector 的语法 信号是:signal <

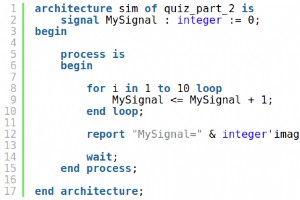

完成基本 VHDL 教程系列中的教程 6-11 后,通过此 VHDL 测验测试您的编码技能! 如果您阅读了博客文章、观看了视频并进行了练习,那么您应该有资格回答测验中的大部分问题。测验是故意使一些具有挑战性的。如果您不知道答案,请尝试使用您的推理能力找出最有可能的答案。 阅读每个答案之后的解释,里面有一些微学习。 这段代码会打印出什么? MySignal=-2147483648 MySignal=0 MySignal=10 正确的!错误的! - 这段代码会打印出什么? MySignal=0 MySignal=1 MySignal=10 正确

VHDL