Verilog 端口

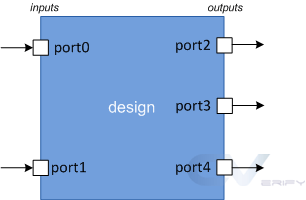

端口是一组信号,它们充当特定模块的输入和输出,并且是与其通信的主要方式。将模块视为放置在 PCB 上的制造芯片,很明显,与芯片通信的唯一方法是通过其引脚。端口就像引脚,被设计用来发送和接收来自外界的信号。

<无脚本>

端口类型

| 端口 | 说明 |

|---|---|

| 输入 | 设计模块只能使用其input从外部接收值 港口 |

| 输出 | 设计模块只能使用其output向外部发送值 港口 |

| 输入输出 | 设计模块可以使用其inout发送或接收值 港口 |

默认情况下,端口被视为 wire 类型的网络 .

语法

声明为 inout 的端口 既可以作为输入也可以作为输出。

input [net_type] [range] list_of_names; // Input port

inout [net_type] [range] list_of_names; // Input & Output port

output [net_type] [range] list_of_names; // Output port driven by a wire

output [var_type] [range] list_of_names; // Output port driven by a variable

示例

在下面显示的代码中,有三个input 端口,一个 output 端口和一个 inout 港口。

module my_design ( input wire clk,

input en,

input rw,

inout [15:0] data,

output int );

// Design behavior as Verilog code

endmodule

使用相同的 name 是非法的 用于多个端口。

input aport; // First declaration - valid

input aport; // Error - already declared

output aport; // Error - already declared

签名端口

signed 属性可以附加到端口声明或 net/reg 声明或两者。隐式网络默认为 unsigned .

module ( input a,

b,

output c);

// ports a, b, and c are by default unsigned

endmodule

如果 net/reg 声明中的任何一个具有 signed 属性,则另一个也应视为已签名。

module ( input signed a, b,

output c);

wire a, b; // a, b are signed from port declaration

reg signed c; // c is signed from reg declaration

endmodule

端口变化

Verilog 1995

Verilog经过多次修改,1995年的原始IEEE版本有以下端口声明方式。在这里,模块声明必须首先在括号中列出端口的名称,然后在模块主体中列出这些端口的方向。

module test (a, b, c);

input [7:0] a; // inputs "a" and "b" are wires

input [7:0] b;

output [7:0] c; // output "c" by default is a wire

// Still, you can declare them again as wires to avoid confusion

wire [7:0] a;

wire [7:0] b;

wire [7:0] c;

endmodule

module test (a, b, c);

input [7:0] a, b;

output [7:0] c; // By default c is of type wire

// port "c" is changed to a reg type

reg [7:0] c;

endmodule

Verilog 2001 起

ANSI-C 风格的端口命名是在 2001 年引入的,允许在端口列表中指定类型。

module test ( input [7:0] a,

b, // "b" is considered an 8-bit input

output [7:0] c);

// Design content

endmodule

module test ( input wire [7:0] a,

input wire [7:0] b,

output reg [7:0] c);

// Design content

endmodule

如果端口声明包括网络或变量类型,则认为该端口已完全声明。在 net 或变量类型声明中重新声明相同的端口是非法的。

module test ( input [7:0] a, // a, e are implicitly declared of type wire

output reg [7:0] e );

wire signed [7:0] a; // illegal - declaration of a is already complete -> simulator dependent

wire [7:0] e; // illegal - declaration of e is already complete

// Rest of the design code

endmodule

如果端口声明不包括网络或变量类型,则端口可以再次在网络或变量类型声明中声明。

module test ( input [7:0] a,

output [7:0] e);

reg [7:0] e; // Okay - net_type was not declared before

// Rest of the design code

endmodule

Verilog