Verilog 初始块

一组 Verilog 语句通常在模拟中按顺序执行。这些语句放在 procedural 中 堵塞。主要有两种类型的程序 Verilog 中的块 - 初始 并且总是

语法

initial

[single statement]

initial begin

[multiple statements]

end

初始块用于什么?

一个initial 块不可合成,因此无法转换为带有数字元素的硬件原理图。因此,初始块除了用于模拟之外没有多大用途。这些模块主要用于初始化变量和驱动具有特定值的设计端口。

初始块何时开始和结束?

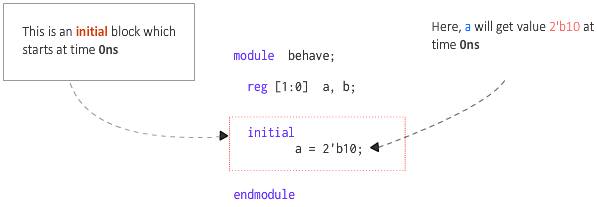

一个 initial 块在时间 0 单元的模拟开始时启动。在整个模拟过程中,该块将只执行一次。 initial 的执行 一旦块中的所有语句都执行完,块就结束了。

上图有一个module 称为行为,它有两个称为 a 和 b 的内部信号。 initial 块只有一个语句,因此没有必要将语句放在 begin 中 和 end .当初始块在时间 0 单位开始时,此语句将值 2'b10 分配给 a。

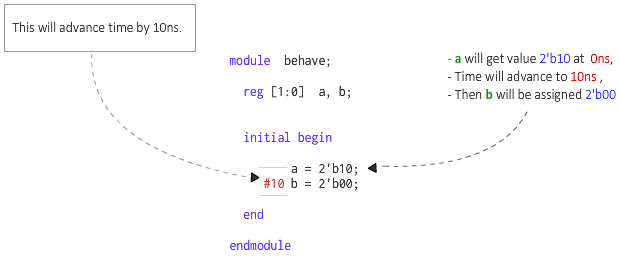

如果有延迟元素会发生什么?

下面显示的代码有一个附加语句,它为信号 b 分配一些值。然而,这只发生在前一条语句执行后 10 个时间单位之后。这意味着a首先被赋予给定的值,然后在10个时间单位之后,b被赋予0。

<无脚本>

一个模块中允许有多少个初始块?

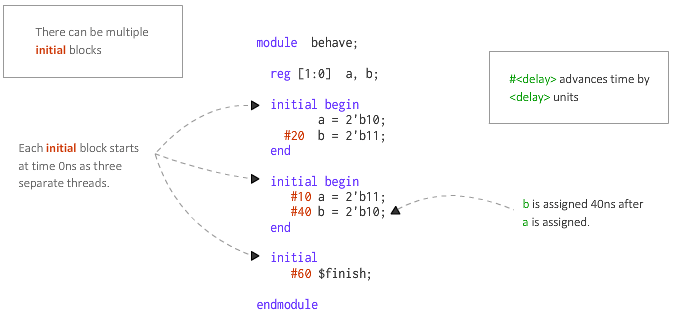

initial的数量没有限制 可以在模块中定义的块。

下面显示的代码有三个 initial 所有这些块都同时启动并并行运行。但是,根据每个初始块内的语句和延迟,完成该块所需的时间可能会有所不同。

在这个例子中,第一个块有 20 个单位的延迟,而第二个块有 50 个单位 (10 + 40) 的总延迟,最后一个块有 60 个单位的延迟。因此模拟需要 60 个时间单位才能完成,因为在 60 个时间单位之前至少有一个初始块仍在运行。

$finish 是一个 Verilog 系统任务,它告诉模拟器终止当前的模拟。

如果最后一个块有 30 个时间单位的延迟,如下所示,模拟将在 30 个时间单位结束,从而杀死所有其他 initial 当时处于活动状态的块。

initial begin

#30 $finish;

end

查看下面显示的 Flash 示例,了解 initial 如何 块在模拟中执行。

单击此处查看带有模拟示例的幻灯片!

Verilog