确保基于多核的关键嵌入式系统中的软件时序行为

安全到达某个地方不仅仅取决于良好的刹车、工作的尾灯以及方向盘后反应灵敏的人。越来越多地,让您的汽车在道路上行驶和飞机在空中飞行的组件不仅是人类的,甚至只是机械的。它们是在复杂的异构多核处理器上运行的复杂嵌入式软件,控制从飞行管理系统到动力转向的一切,并执行以微秒为单位的严格计时期限。

挑战就在这里。多核系统中软件的时序行为不仅受其上运行的软件及其输入的影响,还受运行在其他核上的其他软件的影响。

开发关键的嵌入式系统需要付出巨大的努力和投资(数百万欧元/美元和多年的工程努力)。从软件开发过程的最早阶段开始,安全就必须成为架构和设计的核心。尤其是,系统设计人员必须了解其软件的时序行为,以确保其能够在安全的时间范围内执行。

解决多核时序分析 (MTA) 难题

尽管多核处理器的惊人计算能力(理论上)应该使嵌入式系统更加强大和高效,但在一个内核上执行的软件会减慢在其他内核上运行的软件的执行速度。在这种情况下,由于与在其他内核上运行的任务共享的总线、内存、缓存、设备、FPGA 和 GPU 等共享资源的争用引起的干扰,软件可能需要更长的时间来执行。

您如何量化这种干扰的影响?您如何分析、测试并提供具体证据证明您的安全关键软件在多核平台上运行时始终可以在其时间期限内执行?

巴塞罗那超级计算中心 (BSC)、Rapita Systems Ltd (RPT)、Raytheon Technologies (RTRC) 和 Marelli Europe (MAR) 的专家多年来一直在研究这些问题的答案。 BSC 和 Rapita 一直在开发一种解决方案,该解决方案将很快在航空航天和汽车行业推出。专业的工具和自动化,结合基于需求、以安全为中心的方法是解决难题的关键。

这项工作构成了 MASTECS 项目的基础,该项目是由欧盟委员会资助并于 2019 年 12 月启动的多学科研究和开发项目。 MASTECS 项目将完善技术并支持其用于航空电子设备和汽车系统的认证。 MASTECS 项目的一个关键部分是通过 RTRC 和 MAR 部署的案例研究在两个行业中展示该方法。

最先进的工具

支持时序分析的市售工具对简单(单核)电子产品很有效,但无法扩展以满足新颖的多核特定认证要求和建议。

- 静态时序分析解决方案 [1] 面临复杂性壁垒,既不能有效地为日益复杂的硬件建模,也不能有效地处理异常复杂的软件功能的结构和句法特征。

- 基于测量的解决方案在单核分析市场已经达到了很高的渗透率(Rapita Systems 的 RVS 工具集是最成功的工具集之一)。然而,这样的工具仍然无法完全承受多核引入带来的挑战。他们通常专注于由综合功能测试策略确定的测量场景,但缺乏基于硬件专业知识的方法,该方法有助于为在多核中运行的任务获得可靠的时间界限,并提供必要的支持证据和足够的可追溯性水平。

据我们所知,市场上没有可用的商业工具,除了在 MASTECS 中成熟的工具,该工具能够分析多核平台上的软件时序,重点关注适用的安全标准和新兴的认证要求。

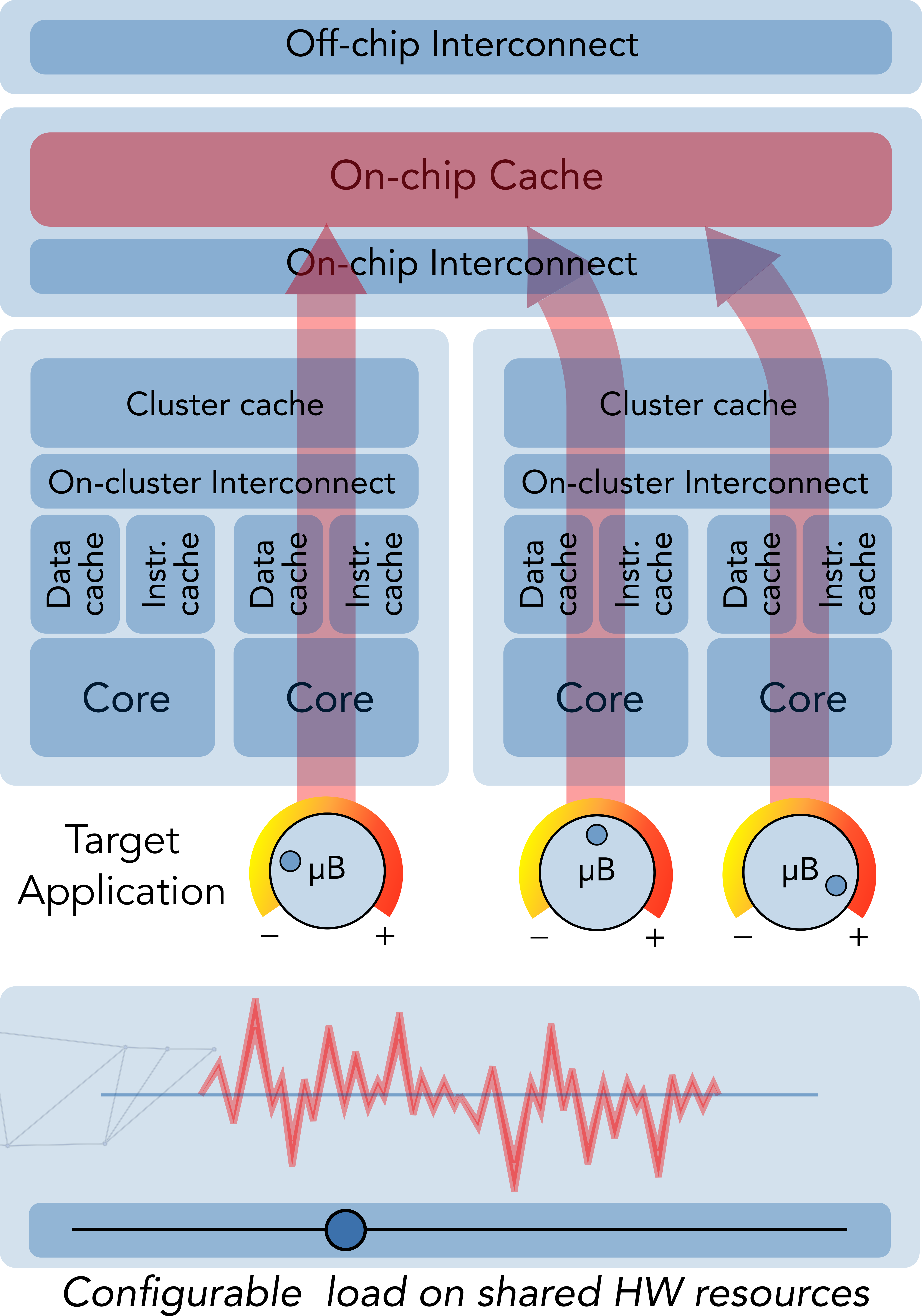

在行动中的干扰分析和控制

理解干扰的关键是一种结构化的测试方法,使用硬件和软件专家来生成有关多核时序行为的证据。 BSC 的一项专门技术(称为多核微基准技术或 MμBT,由 Rapita 商业化为 RapiDaemons)让系统设计人员通过创建额外的干扰场景来对基于多核的应用程序的不同部分进行压力测试,从而分析和量化干扰的影响。多核处理器。

微基准测试是 MuBT 的核心,是精心设计的代码段,它们在硬件和软件之间的最低接口上运行,以强调特定的共享资源。微基准测试暴露了干扰信道对软件时序的影响。为此,可以部署微基准测试以对特定应用程序造成可配置和可量化的压力。微基准测试专门设计用于展示单一、明确定义的行为,对特定硬件资源具有预期影响,同时尽可能防止在其他干扰信道上产生争用。微基准测试的主要功能包括:

- 他们对特定的共享资源施加了可量化的压力。

- 他们的行为可以通过事件监视器进行验证。

- 它们捕获与时间相关的特定要求,例如,您为控制争用而采取的缓解措施是否有效。

点击查看大图

图 1:微基准在干扰分析中的使用。 (来源:作者)

已经开发了广泛的微基准以具有特定的作用,包括匹配所需的干扰水平、最大化对资源的干扰,或者只是对争用(“受害者”)非常敏感。

在分析干扰影响时,任务争用模型 (TCM) 支持 MμBT 的使用,该模型提供争用延迟任务可能遭受的早期估计。 Rapita 开发的软件自动化和测试工具 RapiTest 和 RapiTime 用于编写测试并在嵌入式目标上运行它们。

设计方法

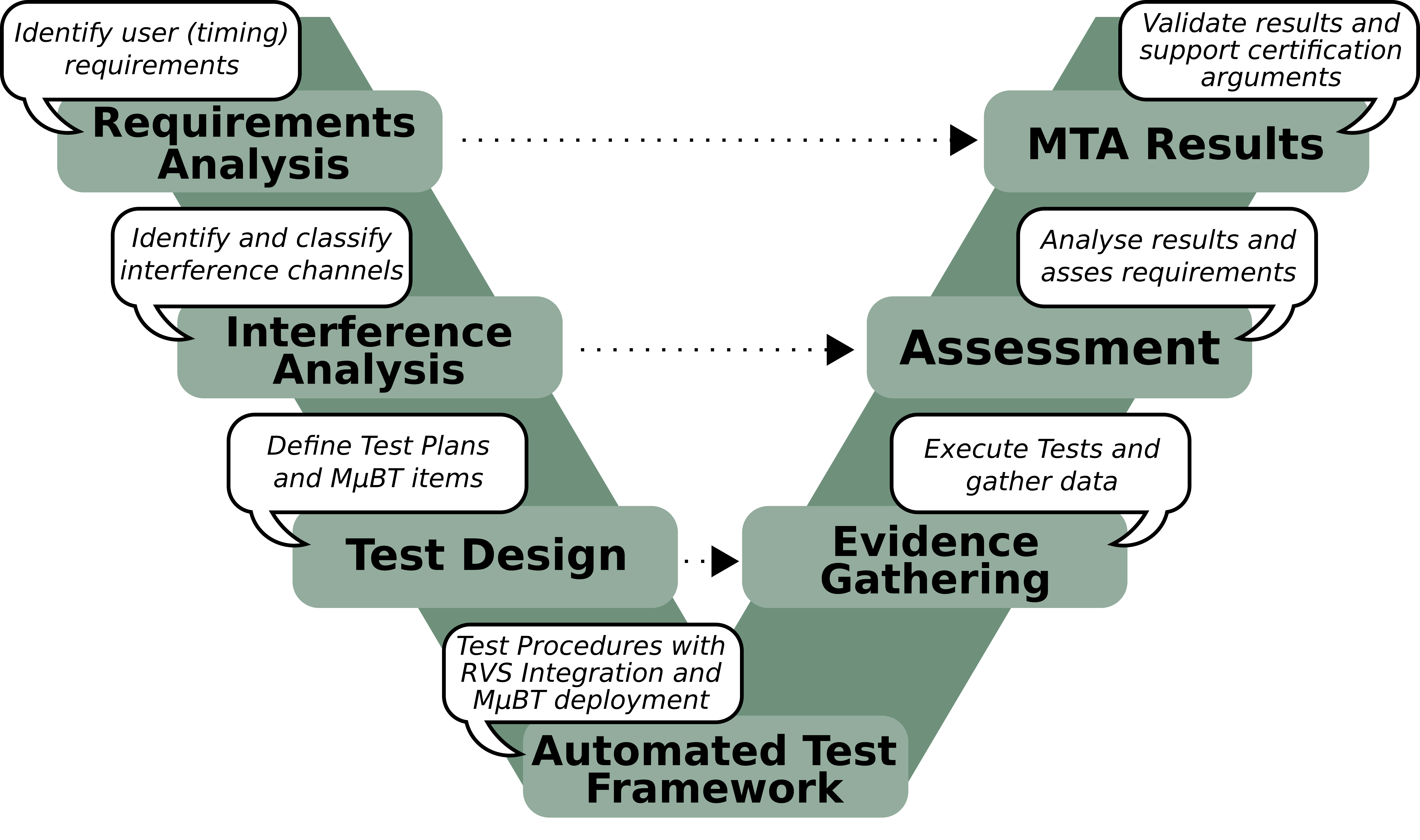

通过遵循标准软件“V”开发流程(图 2)中的七步测试设计流程,工程师可以更全面地了解干扰的影响。

- 多核处理器关键配置设置、干扰通道和事件监视器分析。 硬件专家帮助确定关键配置设置,以设置框架,在该框架中还可以识别干扰信道以及缓解措施。硬件事件监视器的标识也有助于为所有后续步骤提供验证方法。

- 确定时间要求。 帮助最终用户确定他们对系统的特定需求、时间要求、风险和安全问题。例如,验证任何硬件隔离方法的性能以最大程度地减少干扰。

- 测试用例设计。 开发特定的测试用例(测试描述)以验证支持用户要求的一组假设,包括定义在干扰信道分析中提供证据所需的 MμBT 项目。这涉及隔离执行(无干扰)、针对微基准执行以评估应用在不同可量化压力情景下的执行时间和硬件对干扰的敏感性。

- 测试程序的实施。 目前,在 MASTECS 中需要自动执行手动流程,此步骤构建测试程序,包括测试框架、微基准和测量探针以记录/跟踪结果。

- 证据收集(测试)。 测试程序在平台上执行以收集测试证据。目前涉及一些手动工作,这将在 MASTECS 中自动化,使用 RapiTest 自动化框架来执行这些测试并将它们链接回验证要求。

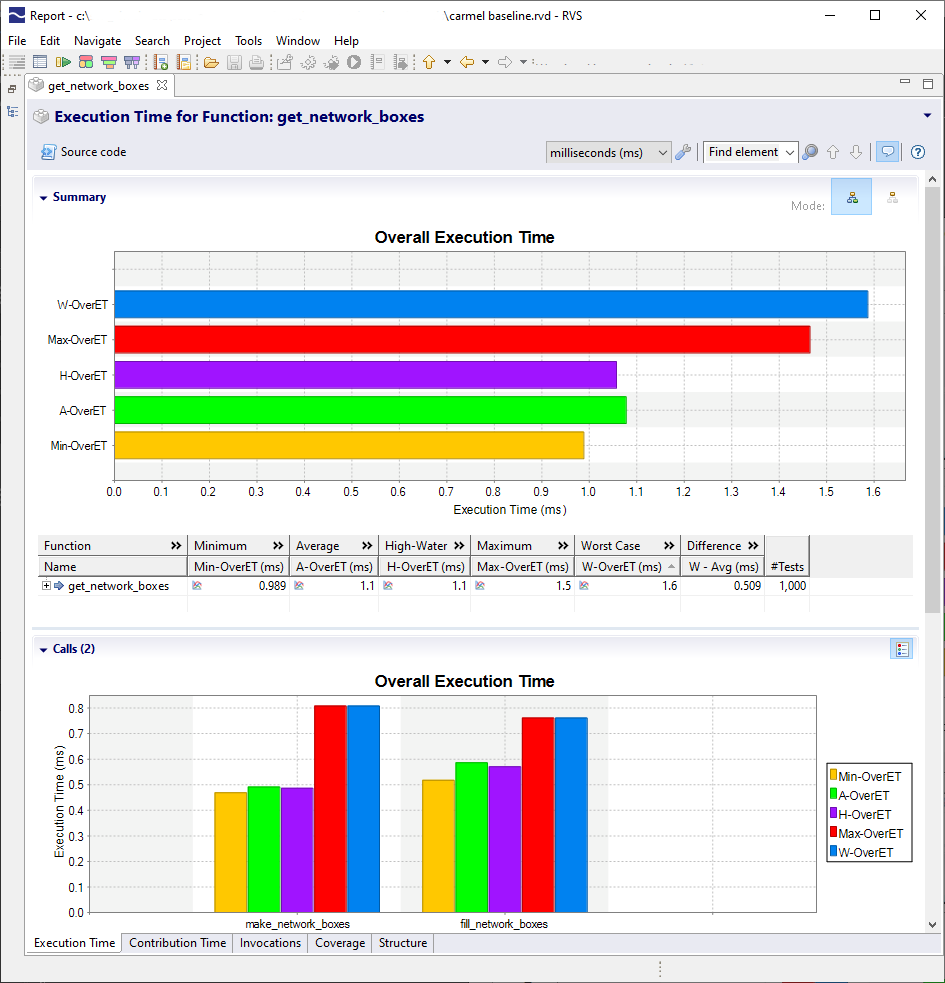

- 结果分析。 技术专家对测试结果的审查,以检查测试结果如何验证(或以其他方式)验证要求。例如,图 3 显示了 RapiTime 对程序不同功能报告的执行时间的屏幕截图。

- 验证结果并生成文档。 最终审查要求、生成文件和确认结果以支持系统的安全论证。客户可以直接使用全套报告和分析工件来认证在多核上运行的软件。

点击查看大图

图 2:V 模型软件开发过程中的 MTA 步骤。 (来源:作者)

硬件专业知识和时序分析过程

注入硬件(多核)专业知识是所提议的 MTA 方法在现代复杂多核上取得成功的关键特征。在早期的软件开发阶段:

- 硬件专家确定多核配置(航空电子术语中的关键配置设置),因为它们在确定软件功能和计时行为方面发挥着关键作用,并且在很大程度上影响彼此生成的争用任务的数量。例如,当前的处理器实现了隔离和隔离机制,如果部署得当,可以大大减少争用。

- 多核专家在识别可能出现任务争用的资源(在航空电子设备中称为干扰信道)方面发挥着关键作用。硬件专家能够浏览数千页的处理器技术参考手册,并针对芯片供应商手册中可能缺失的信息制定适当的问题,这对于推动适当的 MTA 流程至关重要。

- 一旦识别出干扰通道,硬件专家就会识别出可用于跟踪任务在这些干扰通道上生成的活动的事件监视器,作为限制任务可能遭受的争用的代理指标。还必须验证这些事件监视器的正确性 [2],为此设计了一组专门的微基准。

- 最后,硬件专家与时序分析专家携手合作,从用户需求中得出高级和低级需求以及具体测试,以验证支持用户需求的假设。每个测试都会实例化一个或多个由硬件专家设计的微基准程序,以将所需的负载水平置于目标(一组)干扰通道上。

在后期设计阶段:

- 硬件专家参与分析测试结果,以评估他们是确认还是拒绝假设。

- 硬件专家还有助于根据上一步中获得的结果建立新的假设和相应的测试,以防万一。

点击查看大图

图 3:分析结果 (RapiTime)。 (来源:作者)

大局

7 步测试设计过程只是图 2 前面所示的更广泛的多核验证方法的一部分。该方法将作为 MASTECS 项目的一部分继续成熟,旨在实现全面的可追溯性,从综合证据和结果返回到相应的要求和设计。该方法旨在满足 CAST-32A 中定义的目标,CAST-32A 是航空航天认证机构发布的关键指导文件。它还特别符合 ISO 26262,这是汽车行业的安全标准,提倡不受干扰。

CAST-32A 由认证机构软件团队 (CAST) 于 2016 年发布,确定了影响在多核处理器上执行的机载软件系统的安全性、性能和完整性的因素。如果您想在航空电子系统中使用多核硬件,这是首选文档。它提供了旨在指导安全多核航空电子系统生产的目标,包括与识别和限制干扰信道影响相关的目标。在此处查看 CAST-32A 立场文件。 EASA 和 FAA 正致力于将多核通用 CRI 改编为通用 AMC/AC 材料 (AMC 20-193)。预计“今年晚些时候”出版[3]。

专业知识无法自动化

干扰效应很复杂。要解开它们的奥秘,您需要了解多核架构组件以及软件中的调度和资源分配系统的专家。硬件和软件专家之间的合作将成为 MASTECS 项目的核心特征,因为它会持续到未来。但是,虽然协作在软件工具和自动化方面取得了巨大进步,但重要的是要记住,您无法将验证过程的每一步都自动化——尤其是在涉及多核时序分析时。

您需要详细了解系统的经验丰富的工程师。例如,在早期阶段,多核专家可以识别决定软件功能和时序行为的处理器配置(也称为硬件关键配置设置),以及潜在的干扰通道。在分析测试结果时,经验丰富的人类专家重新审视和评估对平台的原始假设,并利用他们的知识进入新的测试周期,没有什么比这更重要的了。

参考文献

[1] 莱因哈德·威廉。对混合临界性的混合感受。最坏情况执行时间分析研讨会,2018.

[2] Enrico Mezzetti、Leonidas Kosmidis、Jaume Abella、Francisco J. Cazorla。用于可靠定时 V&V 的汽车芯片中的高完整性性能监控单元。 IEEE Micro 38(1):56-65 (2018).

[3] https://www.aviationtoday.com/2020/02/28/easa-and-faa-to-issue-further-guidance-on-multicore-certification-this-year/

嵌入式