基于 RISC-V 的开源 GPU

一群爱好者正在提出一套新的图形指令,专为 3D 图形和媒体处理而设计。这些新指令建立在 RISC-V 基本向量指令集之上。他们将本着核心 RISC-V 指令集架构 (ISA) 的精神,添加对特定于图形的新数据类型的支持,作为分层扩展。支持向量、先验数学、像素和纹理以及 Z/Frame 缓冲区操作。它可以是一个融合的 CPU-GPU ISA。该小组将其称为 RV64X,因为指令长度为 64 位(32 位不足以支持强大的 ISA)。

为什么是现在?

世界上有很多 GPU 可供选择,为什么会这样?该小组表示,因为商业 GPU 在满足诸如双相 3D 截锥体裁剪、自适应 HPC(任意位深度 FFT)、硬件 SLAM 等特殊需求方面效率较低。他们相信协作提供了灵活的标准,减少了原本需要的 10 到 20 人年的工作量,并有助于交叉验证以避免错误。

该团队表示,他们的动机和目标是由创建具有自定义可编程性和可扩展性的小型、节省面积的设计的愿望驱动的。它应该提供低成本的 IP 所有权和开发,而不是与商业产品竞争。它可以在 FPGA 和 ASIC 目标中实现,并且是免费和开源的。最初的设计将针对低功耗微控制器。它将与 Khronos Vulkan 兼容,并随着时间的推移支持其他 API(OpenGL、DirectX 等)。

最终的硬件将是带有 GPU 功能单元的 RISC-V 内核。对于程序员来说,它看起来就像一个硬件,带有编码为标量指令的 64 位长指令。编程模型是明显的 SIMD,即编译器从带前缀的标量操作码生成 SIMD。它将包括变量问题、谓词 SIMD 后端、向量前端、精确异常、分支阴影和很多 更多的。该团队表示,将不需要 RPC/IPC 调用机制将 3D API 调用发送到/从未使用的 CPU 内存空间到 GPU 内存空间,反之亦然。它将以 16 位定点(FPGA 的理想选择)和 32 位浮点(ASIC 或 FPGA)的形式提供。

该设计将采用 Vblock 格式(来自 Libre GPU 的成果):

- 有点像 VLIW(只是不是真的)

- 指令块以寄存器标记为前缀,为块内的标量指令提供额外的上下文

- 子块包括:向量长度、混合、向量/宽度覆盖和预测。

- 所有这些都被添加到标量操作码中

- 没有向量操作码(也不需要任何)

- 在向量上下文中,它是这样的:如果一个寄存器被标量操作码使用,并且该寄存器被列在向量上下文中,那么向量模式被激活

- 激活会导致硬件级 for 循环发出多个连续的标量操作(而不是一个)。

- 实现者可以自由地以他们想要的任何方式实现循环:SIMD、多问题、单次执行。

该设计将使用标量(8 位、16 位、24 位和 32 位固定和浮点数)以及超越数(sincos、atan、pow、exp、log、rcp、rsq、sqrt 等)。矢量 (RV32-V) 将支持 2-4 个元素(8 位、16 位或 32 位/元素)矢量操作,以及用于点、像素、纹素(本质上是特殊矢量)的通用 3D 图形渲染管道的专用指令)

- XYZW 点(64 位和 128 位固定和浮动)

- RGBA 像素(8 位、16 位、24 位和 32 位像素)

- UVW 纹素(每个组件 8 位、16 位)

- 灯光和材料(Ia、ka、Id、kd、Is、ks...)

矩阵将是 2 × 2、3 × 3 和 4 × 4 矩阵将被支持作为本机数据类型以及内存结构以支持它们的属性向量,并且本质上将在 4 × 4 矩阵中表示。

融合 CPU-GPU ISA 的优势之一是能够在微代码中实现标准图形管道,提供对自定义着色器的支持并实现光线跟踪扩展。它还支持用于人工智能和机器学习的 8 位整数数据类型的数值模拟向量。

可以实现自定义光栅化器,例如样条线、SubDiv 曲面和面片。

该设计将足够灵活,可以实现自定义流水线阶段、自定义几何体/像素/帧缓冲阶段、自定义曲面细分器和自定义实例化操作。

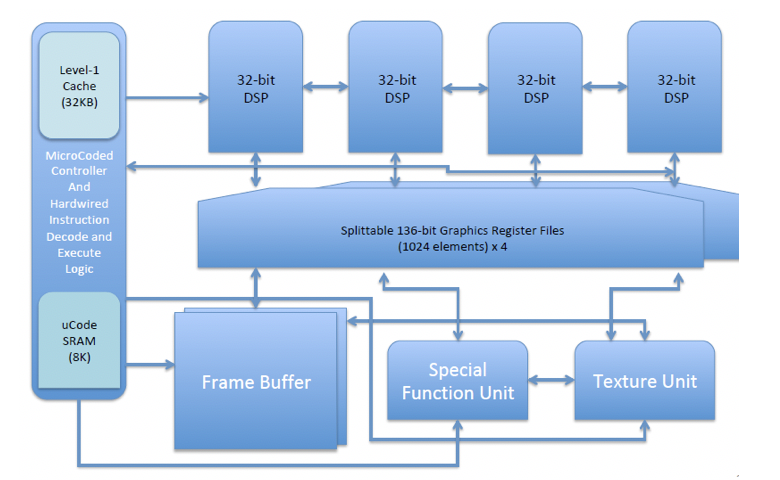

RV64X 框图

RV64X 参考实现将包括:

- 指令/数据 SRAM 缓存 (32KB)

- 微码SRAM(8KB)

- 双功能指令解码器

- 硬连线实现 RV32V 和 X

- 用于自定义 ISA 的微编码指令解码器

- 四向量 ALU(32 位/ALU——固定/浮点)

- 136 位寄存器文件(1K 个元素)

- 特殊功能单元

- 纹理单元

- 可配置的本地帧缓冲区

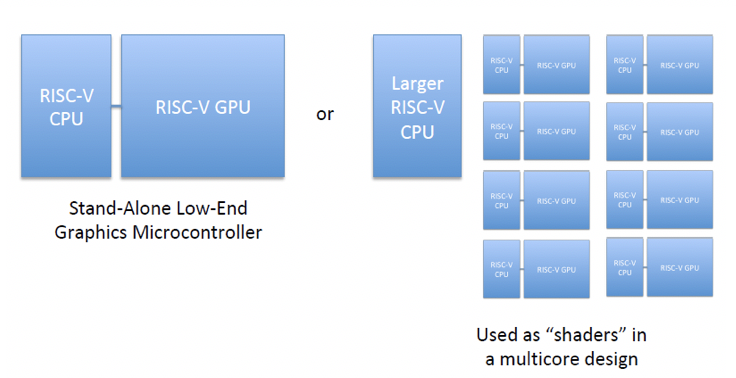

该设计旨在如下所示可扩展。

RV64X 的可扩展设计

RV64X 设计有几个新颖的想法,包括融合统一的 CPU-GPU ISA、用于自定义数据类型的可配置寄存器以及用于应用程序定义的自定义硬件扩展的基于用户定义的 SRAM 微代码:

- 自定义光栅化阶段

- 光线追踪

- 机器学习

- 计算机视觉

相同的设计既可用作独立的图形微控制器或可扩展的着色器单元,数据格式也支持 FPGA 原生或 ASIC 实现。

为什么需要开放图形?

开发人员认为大多数图形处理器覆盖高端,如游戏、高频交易、计算机视觉和机器学习。他们认为,生态系统缺乏可扩展的图形核心,无法用于更主流的应用程序,例如信息亭、广告牌、赌场游戏、玩具、机器人、电器、可穿戴设备、工业人机界面、信息娱乐和汽车仪表组。同时,必须使用专业的编程语言为OpenGL、OpenCL、CUDA、DirectCompute和DirectX编写GPU内核。

RISC-V 的图形扩展将解决可扩展性和多语言负担,从而实现更高水平的用例创新。

后续步骤

这是一个非常早期的规范,仍在开发中,可能会根据利益相关者和行业的意见进行更改。该团队将建立一个讨论论坛。近期目标是使用指令集模拟器构建示例实现,即使用开源 IP 的 FPGA 实现和设计为开源项目的定制 IP。正在设计演示和基准测试。有兴趣参与的开发者应与 Atif Zafar 签约。

至于 Libre-RISC 3D GPU,该组织的目标是设计混合 CPU、VPU 和 GPU。正如广泛报道的那样,它不是“专用的专属 GPU”。存在创建独立 GPU 产品的选项。他们的主要目标是设计一个完整的一体式处理器 SoC,恰好包含一个 Libre 许可的 VPU 和 GPU。

我们怎么看?

GPU 供应商的数量正在增加。我们现在有十多个。

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V GraphicsArmIntelThink-SiliconDMP景佳MicroVeriSilcionImagination Technologies未被列为免费、灵活、小型 GPU 潜在用户的应用程序包括加密货币和挖矿。

如果 RISC-V 社区的目标是模仿 Arm 和 Imagination 等 IP 供应商,那么我们可以期待看到 DSP、ISP 和 DP 设计。至少有一个 Open DSP 提案;也许它可以带入RISC-V社区。

在任何硬件实现出现之前至少需要两年时间。采用这种设计的最合乎逻辑的候选者之一是 Xilinx,它现在在其 Zynq 设计中使用 Arm 的 Mali。我们也希望看到中国有几个实现。

>> 本文最初发表于我们的姊妹网站 EE Times。

乔恩·佩迪 图形行业的先驱,是 Jon Peddie Research 的总裁。

乔恩·佩迪 图形行业的先驱,是 Jon Peddie Research 的总裁。 有关 Embedded 的更多信息,请订阅 Embedded 的每周电子邮件通讯。

嵌入式