背面照明变得更快

高速成像的速度超过每秒 100 万帧,是一种宝贵的研究工具,能够捕捉科学和工程应用中最短暂的事件。然而,要达到这个速度是附带条件的。大多数高速相机旨在实现最大千兆像素/秒 (Gpx/sec) 吞吐量,这是在帧速率与分辨率之间进行权衡。例如,25 Gpx/sec 的相机在 1280 × 800 像素的分辨率下可以达到每秒 25,700 帧 (fps),在 1280 × 720 的较小分辨率下可以达到 28,500 的更高帧速率。两种组合的吞吐量几乎相同.非常高的帧速率(例如 100 万帧/秒)伴随着非常小的分辨率,使得观看主题更具挑战性。

随着帧速率的增加,像素的曝光时间会减少。在 25,700 fps 时,每帧的最大曝光时间为 39 微秒 (µs),而在 100 万 fps 时,最大曝光时间仅为 733 纳秒 (ns)。短曝光时间需要高水平的照明来补偿像素接收光的短时间。事实上,许多高速应用都缺乏光线,这意味着在高帧速率下的曝光时间非常短,可用照明无法为相机的成像传感器提供足够的光线以产生理想的图像,甚至可能不切实际在某些应用中。

高速摄像机操作员已经善于平衡对速度和分辨率的需求与对充足照明的需求。他们能够捕捉到推动科学理解和工程分析前沿的壮观图像,但随着用户突破高速成像的界限,权衡变得更加困难。

最近,取得了一项技术突破,可以缓解速度-分辨率-灵敏度的限制。已经开发出一种新的高速图像传感器,该传感器采用背面照明 (BSI) 来增加可以捕获光子的像素表面积。因为它在捕捉光线方面更有效,所以 BSI 传感器更适合需要高帧速率的应用。在这款相机中,与前几代高速 CMOS 成像传感器相比,吞吐量(最大帧速率乘以最大帧分辨率)增加了三倍。新传感器于 2021 年 3 月在新款 Phantom TMX 相机中首次亮相,其中最快的相机可以在 1280 × 800 像素的全分辨率下拍摄 76,000 fps。

将 BSI 引入高速应用

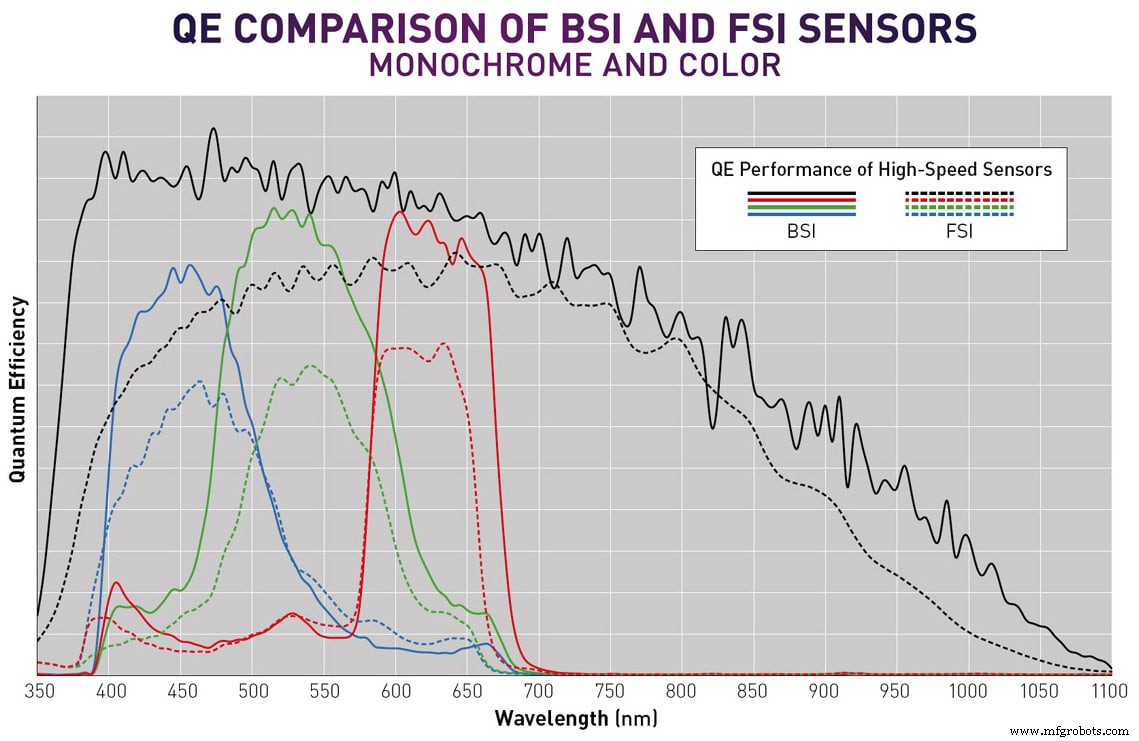

到目前为止,高速相机中使用的 CMOS 传感器一直基于前照式 (FSI) 架构,其中位于像素光电二极管上方的传感器金属电路面向光源。这种金属电路可以防止一些入射光到达像素,进而影响填充因子并降低传感器的灵敏度。

BSI 传感器设计有一个厚载晶片,附着在金属叠层的顶部。这种布置允许体硅被减薄和翻转,以暴露面向光源的二极管和它们后面的金属表面。高速 BSI 传感器有两个显着优势:通过为光提供直接到达光接收表面的路径(见图 1)提高填充因子,以及通过在传感器的金属中添加更多金属来提高处理速度表面。

-

改进的填充因子: 这种捕获入射光的有效性以传感器的填充因子或能够捕获光子的像素表面积的百分比来表示。由于其金属电路阻挡或反射部分光线,高速成像中使用的典型 FSI 传感器将具有 50% 到 60% 之间的填充因子,部分由当前典型 FSI 传感器中的微透镜补偿。通过将电路移开,这种新型 BSI 传感器的填充因子接近 100%。

-

提高处理速度: 像素阵列的基本速度受阻容(RC)时间常数的限制,添加金属可降低电阻并提高速度。在 FSI 传感器中,传感器正面的金属量受到限制,以允许光线到达光电二极管。这种约束会导致处理速度的开销。随着帧速率的增加和分辨率的降低,由于开销损失,相机无法提供最大 Gpx/sec 吞吐量。 BSI 传感器没有这种限制,可以显着增加金属电路,从而大大减少甚至消除开销。这种能力使 BSI 传感器即使在非常高的帧速率/低分辨率组合下也能保持其最大 Gpx/sec 吞吐量。

BSI 传感器已在各种手机和标准数码相机中使用了 10 多年。在改善这些以消费者为中心的相机的低光性能和动态范围方面,它们提供了经过验证的优势。为什么将这些传感器带入高速成像需要这么长时间?一言以蔽之,大小。

高速相机中使用的传感器和像素比标准相机大得多,以最大限度地减少速度-分辨率-灵敏度的权衡。例如,虽然手机摄像头的像素可能每边小于 2 µm,但这种新型图像传感器上的像素通常超过 6 µm,每边最多 28 µm。

BSI 传感器的制造过程本质上比同类 FSI 传感器更困难,并且需要额外的制造步骤。其中包括晶圆背面减薄步骤,以去除体硅,使光电二极管更靠近光源。晶圆背面还有额外的处理步骤,用于对表面进行退火并为正面提供电接触。高速图像传感器的尺寸只会加剧制造难度。半导体经济的现实也使得该技术难以从高产量的标准相机转移到产量相对较低的高速成像传感器。完善制造工艺和实现实际良率需要时间。

BSI 图像传感器值得等待。它为以下方面设定了新标准:

-

速度。 使用该传感器的第一台相机以 76,000 fps 的速度以 1 兆像素 (1280 × 800) 的全分辨率捕获图像,在降低分辨率和合并的情况下,它可以达到一个数量级以上的速度。例如,相机最高速度为 175 万 fps,分辨率为 1280 × 32 和 640 × 64 像素合并。从历史上看,帧速率超过 100 万帧的分辨率对于几乎所有科学用途来说都太低了,但 1280 × 32 代表了在广泛应用中真正可用的分辨率。

-

曝光时间。 新传感器通过出口控制 FAST 选项支持最快 95 ns 的最短曝光时间。快速的曝光时间可以在没有运动模糊的情况下捕捉更快的事件,这可能是在细胞计数和燃烧分析等广泛应用中获得高质量图像的限制因素。

-

像素大小。 为了在光线不足的条件下工作,高速相机历来使用非常大的像素尺寸作为捕捉尽可能多光子的手段。例如,我们现有的 FSI 超高速传感器的像素大小为每边 28 µm,面积为 784 µm 2 .新的 BSI 高速图像传感器每侧像素为 18.5 µm,但其捕捉光线的能力使其灵敏度大约是早期具有 28 µm 像素的 FSI 传感器的三倍。较小的像素还提高了采样频率 (Nyquist),允许传感器在混叠之前解析更高的 lp/mm 空间频率。这种能力增强了成像系统在流式细胞术、粒子图像测速(PIV)、数字图像相关(DIC)和其他受传感器分辨率限制的高速应用中的性能。

BSI 之外

与新图像传感器设计相关的性能突破主要依赖于其 BSI 架构,但设计还不止于此。新传感器还具有许多设计功能,可提高 BSI 单独无法实现的性能,尤其是与高速读取大量成像数据和提高吞吐量的能力有关。

解决模数转换难题。 在 CMOS 图像传感器上嵌入模数转换器 (ADC) 是标准做法,但 BSI 传感器的速度需要大量增加 ADC 的数量。虽然现代 CMOS 图像传感器通常具有 1,000 到 10,000 个嵌入式 ADC,但新的 BSI 高速传感器具有 40,000 个 ADC,每个 ADC 转换每 523 ns 并生成大量数据以从传感器卸载。为了完成这项任务,它集成了 160 个运行速度超过 5 Gbps 的高速串行输出。这种技术在 CPU 和 FPGA 上很常见,但在高速成像传感器上却是新的。

新传感器上的 ADC 密度确实带来了电源管理和电气串扰挑战,我们在设计和集成生产合作伙伴 Forza Silicon 的帮助下解决了这些挑战。虽然模拟通常用于预测传感器性能,但这种传感器需要模拟计算数周才能提供预测。

Forza 在简化模拟和分析实际结果与预测结果以进行快速设计修改方面拥有丰富的经验。对于 BSI 传感器,早期设计的测试显示,在正常成像和分箱模式下,ADC 串扰水平高于我们的仿真工具所预测的水平,从而导致图像中出现明显的伪影。 Forza 工程师发现串扰表现出可预测的模式,并开发了有助于完全消除串扰的建模技术,从而减轻了成像伪影。

分箱以获得最大吞吐量。 该传感器支持 2 × 2 分箱,以更快的速度最大化吞吐量。虽然在高速传感器中并不常见,但我们已经在之前的两个相机中实现了分箱。它有助于减轻传感器列 ADC 架构的限制,实现比简单减小 y 尺寸更快的速度。这种方法与 CCD 相机中应用的 binning 略有不同,后者主要用于提高灵敏度。在这种情况下,它是用来提高速度的。

BSI 差异

BSI 并不是一项新技术,它已在标准相机和手机相机中取得了巨大成功。通过将其应用于高速成像,已经创建了一种传感器,可以在光线不足的条件下突破速度的界限。

本文由首席科学家 Radu Corlan 和 Vision Research 研发部副总裁 Kevin Gann(新泽西州韦恩)撰写;以及 Forza Silicon(加利福尼亚州帕萨迪纳)的工程副总裁 Loc Truong。欲了解更多信息,请联系 Mr. Gann,此电子邮件地址已受到防止垃圾邮件机器人的保护。您需要启用 JavaScript 才能查看它。或访问这里 .

传感器