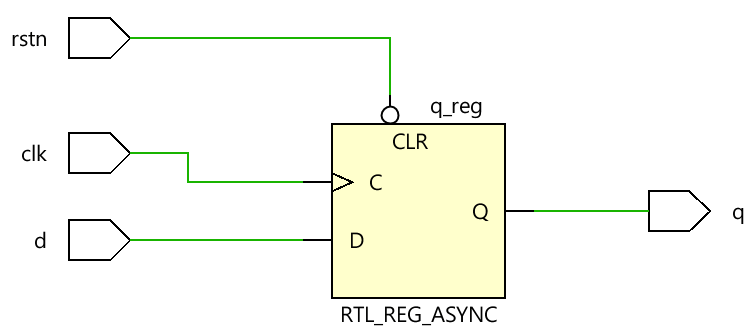

D 触发器异步复位

A D 触发器 是跟随输入引脚 d 的顺序元素 在时钟的给定边沿。

设计#1:异步低电平有效复位

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk or negedge rstn)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

硬件示意图

<无脚本>

测试台

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

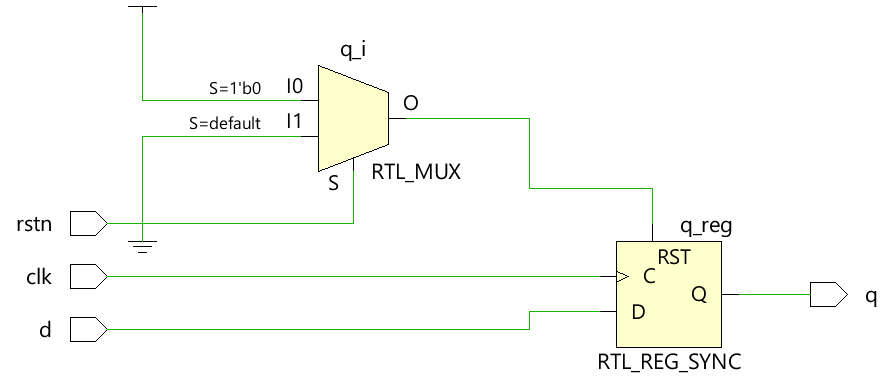

设计#1:同步低电平有效复位

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

硬件示意图

<无脚本>

测试台

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

Verilog