Flash ADC

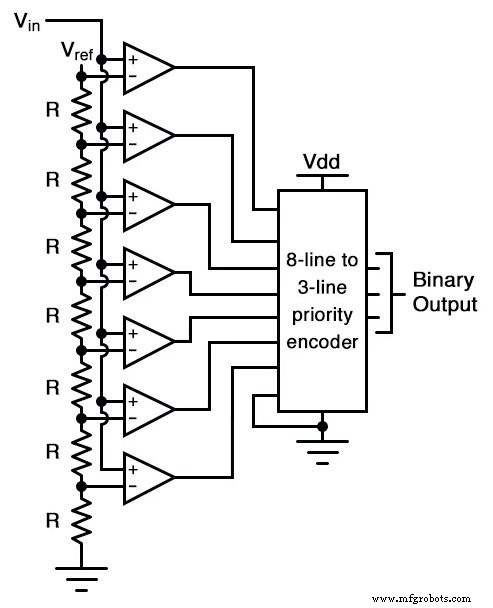

也称为并行 A/D转换器,这个电路最容易理解。它由一系列比较器组成,每个比较器将输入信号与唯一的参考电压进行比较。比较器输出连接到优先编码器电路的输入,然后产生二进制输出。下图显示了一个 3 位闪存 ADC 电路:

Vref 是由精密稳压器提供的稳定参考电压,作为转换器电路的一部分,示意图中未显示。当模拟输入电压超过每个比较器的参考电压时,比较器输出将依次饱和至高电平状态。优先级编码器根据最高阶有效输入生成一个二进制数,忽略所有其他有效输入。

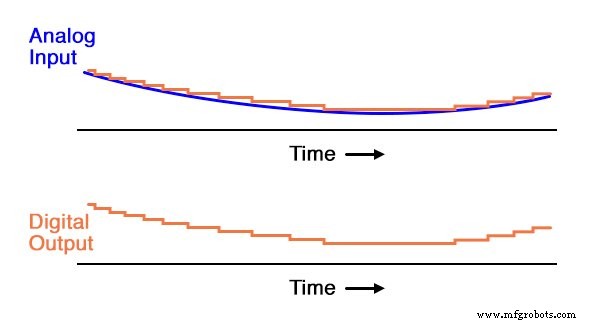

操作时,闪存 ADC 会产生如下所示的输出:

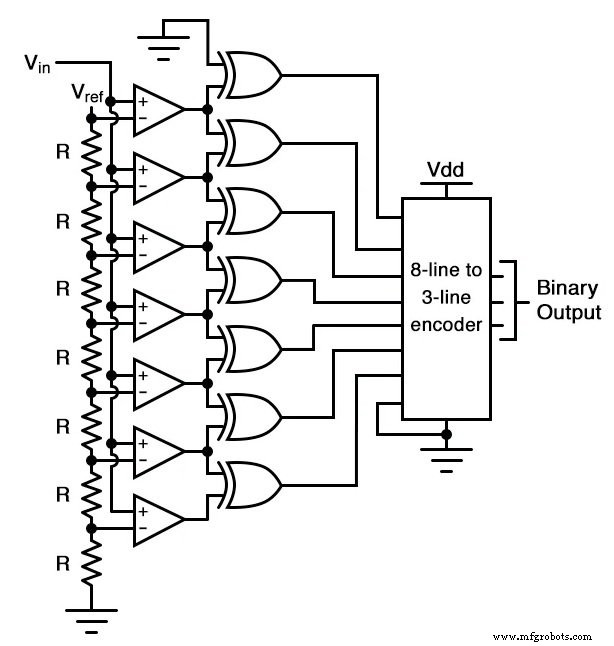

对于此特定应用程序,不需要具有所有固有复杂性的常规优先级编码器。由于顺序比较器输出状态的性质(每个比较器从最低到最高依次饱和“高”),可以通过一组异或门实现相同的“最高阶输入选择”效果,允许使用更简单的非优先编码器:

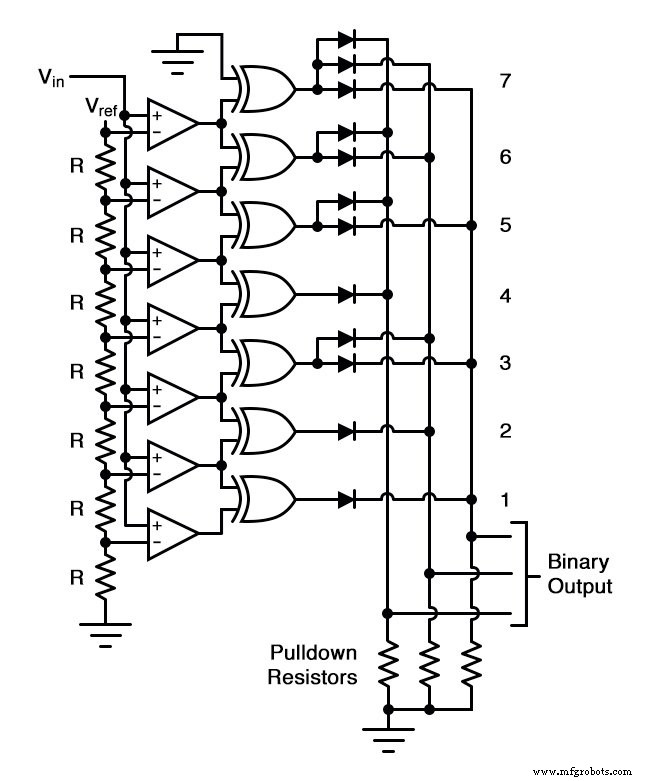

而且,当然,编码器电路本身可以由二极管矩阵制成,这证明了这种转换器设计的构造是多么简单:

闪存转换器不仅在操作理论方面最简单,而且在速度方面也是最高效的 ADC 技术,仅在比较器和栅极传播延迟方面受到限制。不幸的是,对于任何给定数量的输出位,它是组件密集度最高的。

这个三位闪存 ADC 需要七个比较器。四位版本需要 15 个比较器。每增加一个输出位,所需比较器的数量就会增加一倍。

考虑到 8 位通常被认为是任何实际 ADC 所需的最低要求(需要 255 个比较器!),闪存方法很快就显示出它的弱点。 Flash 转换器的另一个优点是它能够产生非线性输出,这一点经常被忽视。

使用参考分压器网络中的等值电阻器,每个连续的二进制计数代表相同数量的模拟信号增加,提供成比例的响应。然而,对于特殊应用,分压器网络中的电阻值可能不相等。

这为 ADC 提供了对模拟输入信号的自定义非线性响应。其他任何 ADC 设计都无法通过更改少量组件值来实现这种信号调节行为。

相关工作表:

- 模数转换工作表

工业技术