低噪声放大器FR设计你需要知道的7个技巧

令人兴奋的全新 RF 前端 高性能射频 (RF) 收发器的设计确保了最佳的说服技术。一般来说,如果你打算只通过增加晶体管宽度或电源电压来改进它,就会产生设计问题。您可能需要更大尺寸的 PCB,并且功耗会更高。在本文中,我们将介绍低噪声放大器的设计结构技巧 (LNA) 用于射频接收器/收发器。

我们将帮助您生产通过低功耗运行提供最佳性能的 LNA PCB。

设计具有低噪声系数的低噪声放大器电路

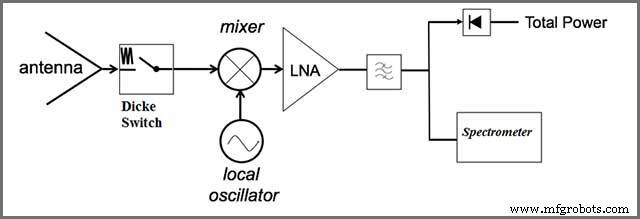

如果您想出创新的低噪声放大器原理图来降低其功耗和电压消耗,将会有所帮助。低噪声放大器放大天线的信号功率,同时确保噪声较小。它将提供足够的增益来克服下一级的噪声。

通常,LNA 原理图具有输入和输出阻抗匹配块,它们之间有一个放大块。您应该确保检查 RF 前端的增益限制,然后相应地最小化噪声系数。例如,可以限制在 2.4 GHz 射频下最大可实现增益为 20 dB。

我们建议您设计一个带有电感的线性噪声放大器。它们是反应性的,因此它们不会在您的 PCB 中产生任何噪音。 LC谐振总是能提高LNA的噪声性能和增益是事实。

计算噪声系数和增益性能指标

所以,我们刚刚告诉您要保持 PCB 的低噪声系数。但是你怎么能确定它很低呢?您将需要得出一个公式,然后进行分析。通常,您将获得噪声系数并获得性能指标来检查您的 LNA PCB 活动。

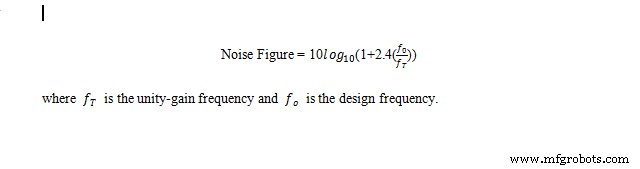

通常,您可以通过推导包括负载阻抗和晶体管有效跨导的公式来计算任何 LNA 电路的增益。对于噪声系数,可以使用以下通用公式进行分析:

使用多层低噪声放大器PCB。

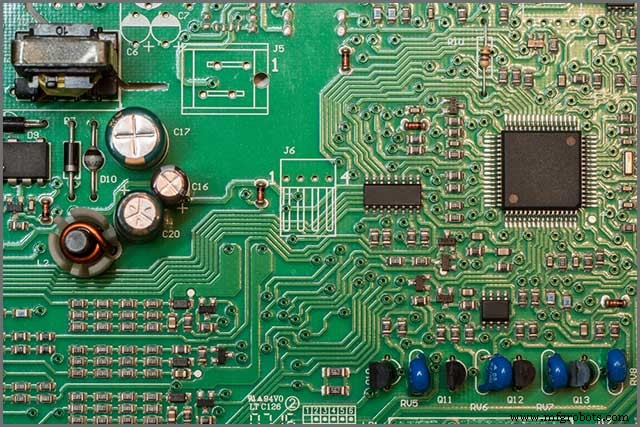

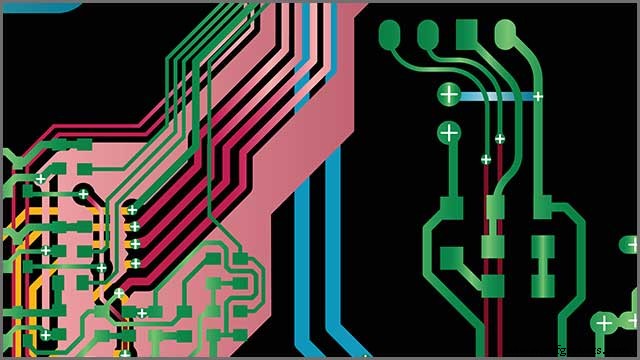

需要注意的是,低噪声放大器 PCB 将在射频下工作。因此,如果您要设计一个 4 层 PCB 布局,它将保持一个恒定的接地层。它将进一步允许在两个主要接地平面层之间对直流电源区域进行分布式射频去耦。

低噪声放大器电路原理图的 PCB 布局需要一个公共射频参考点。它是来自输入或输出端口的所有射频信号的射频接地点。通过添加一个共同点,您将确保所有点都处于相同的电位。

在 4 层 PCB 设计中,您可以设置一个电源层、两个接地层和一个电路走线层。此外,如果您充分设计了铜迹线的形状和宽度,将会有所帮助。它会降低低噪声放大器电路中的分布电感、电容和电阻。

4 层 PCB 还可以让您获得可控尺寸的微带线。微带线是射频范围 PCB 上的高导电金属流道。您可以联系 PCB 制造商计算介电常数、铜重量、材料数据、核心厚度和标准层堆叠等参数。使用此信息,您可以轻松地将微带线与所需的阻抗值匹配。最后,如果您设计完整的偏置走线以降低路径电阻,将会有所帮助。

在低噪声放大器 PCB 中使用表面贴装器件

表面贴装技术是一种将电子元件直接安装在印刷电路板上的方法。如果您使用表面贴装器件,您将获得更短的铜迹线和更小的噪声放大器 PCB 尺寸。并且,在射频电路中,它会降低寄生电阻和电容。

此外,如果您保持表面贴装组件和接地之间的连接短路,这将有所帮助。就是降低阻抗。您也可以通过在接地平面上设计两个或三个平行过孔来实现这一点。

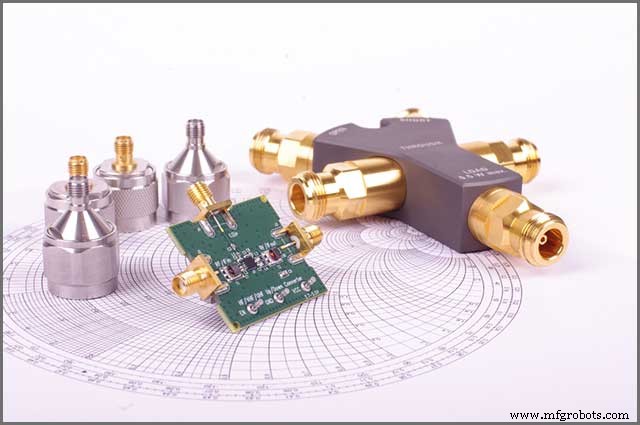

另一个关键点是定义低噪声放大器电路的测试温度范围。您的表面贴装元件必须能够在此温度范围内工作。此外,您可以将香蕉插孔用于偏置电压、接地和电源连接。为了获得射频连接,您可以在低噪声放大器 PCB 中使用 SMA 连接器。除了体积小,它们还提供宽频率范围和高可靠性。

低噪声放大器——为低噪声放大器电路选择合适的PCB材料

可接受的 PCB 材料有助于设计低噪声放大器。它将减轻放大器限制(例如噪声系数和增益)的热量水平。总而言之,PCB 的选择可以对您的 LNA 设计的最终性能水平做出重大贡献。

如果您考虑将各种 PCB 材料特性作为低噪声放大器的设计候选,将会有所帮助。这些参数包括损耗因数(Df)、介电常数(DK或εr)、热导率、Dk温度系数和基板厚度公差。

例如,您应该在整个材料中严格调节 PCB 材料的 Dk,以实现刚性阻抗匹配。如果您经常使用它来保持较低的放大器噪声系数,将会有所帮助。此外,介电常数(Tc Dk)温度系数也会影响这些噪声系数和阻抗匹配网络。

低噪声放大器——根据高频信号的要求设计您的PCB

永远记住,您正在处理小型噪声放大器电路中的高频信号。 PCB 将在射频范围内工作,因此您必须进行相应的设计。正如我们已经讨论过的,有必要使用多层板来减少干扰。四层板的噪音比同材质的双层板小20分贝。然而,与此同时,人们也担心生产会更加复杂。成本会更高,而且您需要专业知识来设计 PCB 布局。

低噪声放大器电路中的射频信号在布线时不得形成环路。如果无法避免,则可以确保将其保持在尽可能小。您还应该注意串扰,它可能在平行信号线附近发展。串扰是射频信号中由于附近电磁场的干扰而产生的不良噪声信号。

有不同的方法可以避免串扰。您可以尝试将一层中的平行线垂直连接到不同的层。此外,您应该在低噪声放大器设计中使用较少数量的过孔。它将提高速度并减少数据错误。最后,请保持引脚之间的电线较短。避免因射频信号引线较长而与元器件耦合。

实现低噪声放大器的刚性阻抗匹配电路

如果您尝试为低噪声放大器获得刚性阻抗匹配电路,这将有所帮助。它考虑了最佳噪声性能、过滤并提供输入和输出稳定性。电阻、带状线、电容、电感等无源元件构成匹配电路。

PCB 材料公差(例如铜厚度和导体宽度公差)会影响该电路。如果有任何与电路制造有关的问题,它也会影响您的阻抗匹配电路。这些公差的大小取决于 LNA 系统的具体设计。

例如,铜厚公差对耦合结构的影响更大,比如共面电路。

另一方面,关注基板的电路导体宽度和厚度的影响。对于导体宽度的增加,较细的通道比较厚的通道显示出更显着的阻抗调整。

DK 容差是 PCB 的另一个参数,它可能会影响 LNA 设计中所需的阻抗匹配网络。

总结

因此,您可以遵循这些技巧来正确设计低噪声放大器电路。您需要正确的阻抗匹配网络、PCB 材料、PCB 层、偏置电路、噪声系数和增益。您可以根据射频信号要求设计低噪声放大器 PCB,从而确保设计质量。

如果您需要正确的 PCB 服务提供商。值得庆幸的是,有各种PCB制造服务,您可以联系我们,我们可以提供技术、材料和优质服务。现在就联系我们吧。

工业技术