Verilog 硬件描述语言入门

在本文中,我们将研究一个 Verilog 模块的基本结构,看一些使用 Verilog “wire”数据类型及其向量形式,并简要介绍 VHDL 和 Verilog 之间的一些差异。

在本文中,我们将研究一个 Verilog 模块的基本结构,看一些使用 Verilog “wire”数据类型及其向量形式的例子,并简要介绍 VHDL 和 Verilog 之间的一些区别。

Verilog 和 VHDL 是两种常用来描述数字电路的语言。 AAC 有一系列技术文章讨论 VHDL 的基本概念。本文是我们关于 Verilog 的系列文章的起点。

我需要 Verilog 和 VHDL 吗?

在开始我们的讨论之前,让我们先解决一个明显的问题:我们真的需要同时了解这两种语言吗?

Verilog 和 VHDL 都是强大的工具,可用于设计复杂的数字电路。尽管这两种 HDL 之间存在一些差异,但您可以自由选择其中一种来掌握和使用。但是,我相信在某个时候,您至少会从对这两种语言的基本了解中受益。有时,作为设计师,我们需要一个示例代码段来了解项目编码。我们在网上冲浪了几个小时,终于找到了我们需要的东西,但这对我们来说毫无意义——它是用我们完全不熟悉的 HDL 编写的。如果对语言没有基本的了解,我们可能无法完全理解其中的技术。

Verilog 演进

Verilog 由 Gateway Design Automation 于 1984 年初设计(大约在美国国防部发起 VHDL 三年后)。在国防部的支持下,VHDL 于 1987 年成为 IEEE 标准。Verilog 直到 1995 年才出现。今天,VHDL 和 Verilog 都是流行的 HDL,FPGA 设计工具通常支持这两种语言。

“Verilog”这个词是“验证”和“逻辑”这两个词的混合体,因为该语言最初被建议用作模拟和验证工具。让我们开始了解 Verilog 的概念和语法。

示例 1

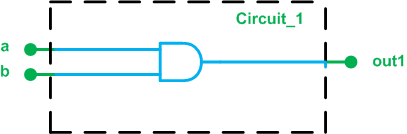

作为第一个例子,让我们为图 1 所示的电路编写 Verilog 代码。

图 1. 电路_1

有两个输入和一个输出。端口都是一位宽。该电路的功能是对两个输入进行“与”运算,并将结果放在 out1 端口上。

Circuit_1 模块的一种可能的 Verilog 描述是:

第 1 行和第 8 行

这两行使用关键字“module”和“endmodule”来指定中间的行(第 2 行到第 7 行)都描述了一个名为“Circuit_1”的电路。这个名字是任意的,让我们以后可以参考这个电路。

第 2 行到第 6 行

这些线指定了“Circuit_1”与其周围环境的接口。输入和输出端口使用关键字“输入”和“输出”进行描述。这些关键字后跟另一个关键字“wire”,然后是端口名称(参见图 1)。关键字“wire”指定什么? “Wire”是一种 Verilog 数据类型,表示设计中的物理连线。我们将在以后的文章中更详细地讨论 Verilog 数据类型,但现在,我们知道在我们的模块中将有 3 条线,称为 a、b 和 out1,并且由于这些是在端口声明中指定的,因此它们对应于模块接口。

第 7 行

该行使用按位 AND 运算符,即 &来描述电路的功能。关键字“assign”将 a&b 放在输出端口 out1 上。这种类型的赋值称为连续赋值。之所以这样称呼,是因为每当右侧的操作数发生变化时,赋值总是处于活动状态,a&b 被评估并分配给 out1。我们可以将连续分配设想为一个组合电路,其输出根据其输入不断更新。在我们的例子中,这个组合电路是一个简单的与门。 Verilog HDL 中还有程序分配,将在以后的文章中讨论。

现在,我们可以使用 Xilinx ISE 等软件包来验证上述代码。您可以在此处 (PDF) 找到该软件的基于 Verilog 的教程。

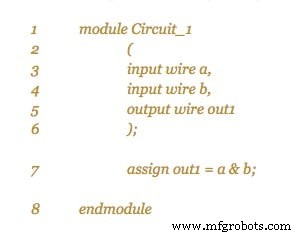

将示例 1 与 VHDL 代码进行比较

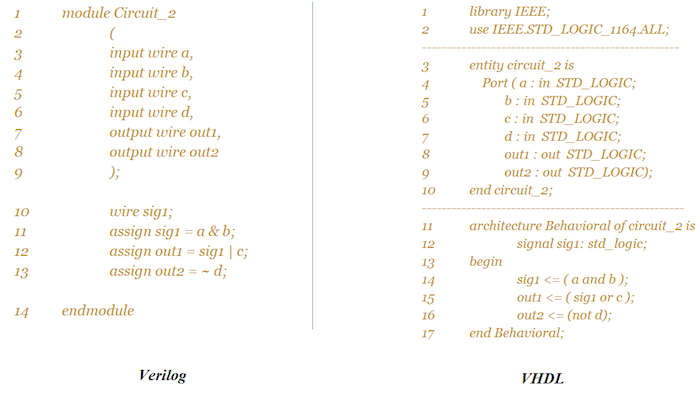

下面的图 2 显示了 Circuit_1 模块的 Verilog 和 VHDL 描述。

图 2。 Circuit_1 的 Verilog 和 VHDL 描述的比较。

如您所见,在使用 VHDL 进行编码时,我们必须包含一些库。这些库给出了数据类型和运算符的定义。考虑到这些库的添加和 VHDL 的一般格式,我们观察到 VHDL 代码更加冗长。然而,这种冗长并非没有优势。例如,VHDL 的库管理功能在建模更高级别的系统时会很有帮助。在以后的文章中,我们偶尔会讨论这两种 HDL 的优缺点。

Verilog 有一个四值系统

大多数 Verilog 数据类型中使用了四个基本值。清单 1 中定义的连线可以采用以下值之一:

- 0:逻辑低或错误条件

- 1:对于逻辑高或真条件

- z:为高阻态(可用于描述三态缓冲器的输出)

- x:用于无关紧要或未知的值(当输入未初始化或两个或多个冲突的输出连接在一起时)。

VHDL std_logic 数据类型可以采用九种不同的值,但其常用值是“0”、“1”、“Z”和“-”(“-”表示不关心)。

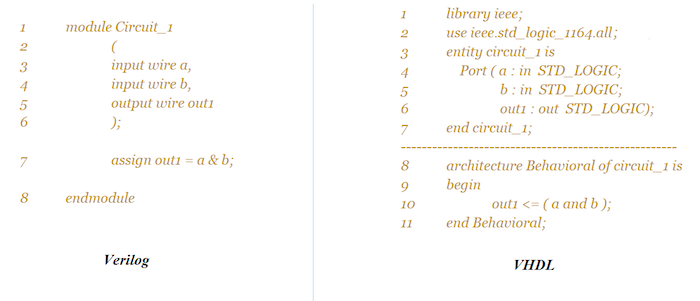

示例 2

再举一个例子,让我们为图 3 所示的电路(我们将其标记为 Circuit_2)编写 Verilog 代码。

图 3。 电路_2

下面的 Verilog 代码描述了这个电路:

上述代码中使用的元素与示例 1 中的元素类似,不同之处在于代码的第 10 行定义了内部信号。关键字“wire”用于指定此连接的数据类型。如上所述,“连线”数据类型将转换为设计中的物理连线。

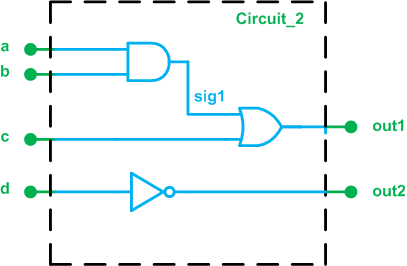

上面的代码还使用了一些新的 Verilog 按位运算符:~ 表示 NOT 和 |用于 OR 操作。另一个有用的按位运算符是 ^ 用于 XOR 运算。图 4 显示了 Circuit_2 模块的 Verilog 和 VHDL 描述。这样的比较可以帮助您了解这两种语言之间的异同。

图 4。 Circuit_2 的 Verilog 和 VHDL 描述的比较。

示例 3

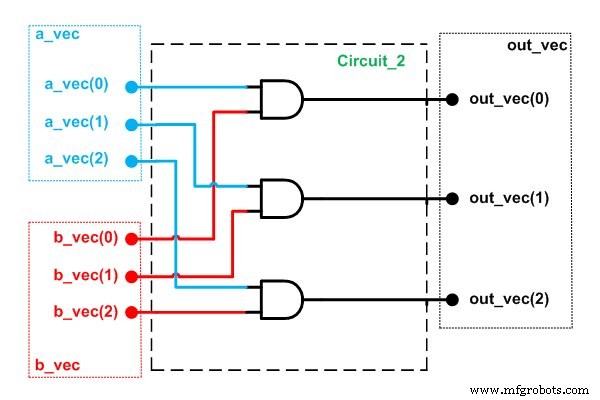

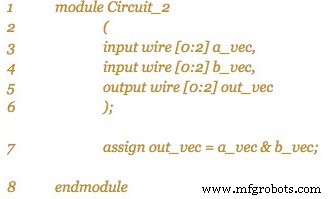

对于我们的第三个也是最后一个示例,我们将提供图 5 中所示原理图的 Verilog 代码。

图 5. 示例3的示意图。

如您所见,蓝色输入端口和红色输入端口之间存在一定的关系:相应的输入与 AND 运算符组合在一起。结果分配给一个输出端口。在这种情况下,我们可以将信号分组并将它们视为一个向量。这使得代码紧凑且可读。

使用 Verilog 中的向量概念,我们可以轻松扩展清单 1 中的代码来描述上述电路(参见下面清单 3 中的代码)。

请注意,向量的索引范围可以是升序(上面使用的 [0:2])或降序([2:0])。虽然上面使用了升序格式,但使用降序格式通常不太容易出错。这是因为降序样式符合我们的看法,即二进制数的最左边位置具有最高索引。请注意,VHDL 中也使用了向量。

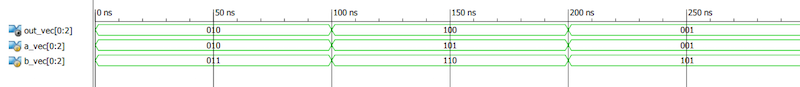

下面的图 6 显示了清单 3 中代码的 ISE 模拟。

图 6. 例 3 代码的 ISE 仿真。

在本文中,我们讨论了同时学习 VHDL 和 Verilog 是一个好主意,我们研究了一个 Verilog 模块的基本结构,我们熟悉了 Verilog “线”数据类型及其向量形式。我们还简要介绍了 VHDL 和 Verilog 之间的一些差异。 Verilog 系列的下一篇文章将讨论在 Verilog 中设计组合电路。

嵌入式