7nm 及以后的材料创新关键

作为我们位于纽约州奥尔巴尼的半导体研究团队,继续将 CMOS 技术扩展到未来节点——10nm、7nm 及以上——决定电流流动的晶体管沟道电阻以及我们如何连接它,继续在以下方面发挥越来越重要的作用芯片的整体性能。因此,为了确保给定未来半导体技术性能的竞争力,降低晶体管沟道电阻的沟道材料创新是一个关键的研究领域。这就是我们探索硅锗 (SiGe) 的原因——实现去年 7 纳米芯片公告中概述的功率性能优势所需的元素。

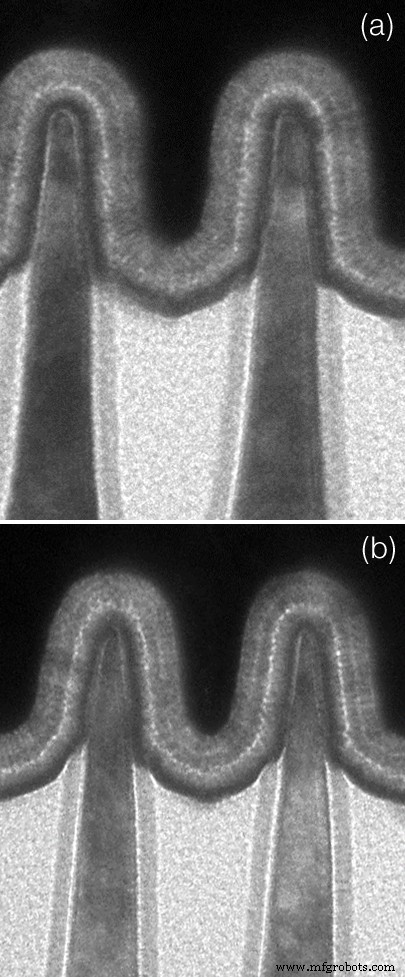

对称硅FinFET (a) 和 SiGe FinFET (b) 在 10nm 下由 IBM Research 在纽约州奥尔巴尼市纽约州立大学理工学院纳米技术中心制作的剖面图。这说明SiGe Fin可以提供比Si Fin优越的电性能。

今天的基于 14 纳米节点 FinFET* 的芯片仅使用硅通道(硅在超出此规模后不稳定)。另一方面,基于 SiGe 的 FinFET 技术已经通过 10nm 技术基本规则(行业标准)展示了性能增强,为可行的 CMOS 技术选项提供了优雅的解决方案。其中一种优雅的 SiGe FinFET 解决方案是允许在同一芯片上同时支持低功耗和高性能设备 - 不会降低一种设备的性能或可变性。

与 Si FinFET 相比,SiGe FinFET 技术还提供了卓越的电气可靠性。这导致在芯片寿命期间比 Si FinFET 提高了芯片级性能稳定性。这意味着相同的流程集成流程适用于超级计算机设计以及移动设计。

SiGe 通过改变电流通过晶体管沟道的方式,突破了芯片缩放的界限。事实证明,通过将较大的锗原子添加到由较小的硅原子组成的晶体中,晶体会产生晶格失配,从而在晶体管沟道中产生应变。这种应变使得在较低电压下通过通道移动更多电流成为可能。因此,通过使用 SiGe 作为沟道材料,我们可以绘制出更小尺寸的路线图,同时保持功率和性能之间的平衡。

面向未来节点的 SiGe:解决生产 10nm 和 7nm 芯片的挑战

整个集成流程中的应变保持以及缺陷控制是在 10 纳米节点及以下节点生产 SiGe FinFET 的两个主要技术挑战。在激活掺杂剂和稳定晶体管完整性的热退火过程中,晶体管通道可能会失去应变;或在形成从鳍片顶部到鳍片底部的均匀结的源/漏凹槽工艺期间;甚至需要较短长度的鳍片 的特定设计中的鳍片图案。

缺陷控制在 CMOS 技术的大规模生产中也很关键。由于 SiGe 通道与其硅晶片衬底之间的晶格失配,在整个晶片上保持所需的可制造性缺陷水平具有挑战性。但凭借我们先进的外延(晶体)生长管理、创新的 Fin 模块工艺集成和源极/漏极工程,我们开发了解决方案以确保整个集成流程中的通道应变,同时在我们的 10nm 和 7nm 测试中保持低缺陷率节点。

通过这项基于 10 纳米技术基本规则的全面 SiGe FinFET 技术可行性研究,我们现在正与芯片设计人员和芯片制造商合作,大规模生产 SiGe FinFET 技术。我预计我们的 SiGe FinFET 技术将在下一代 CMOS 技术节点中取代硅 FinFET,用于计算用途,从超级计算机到移动设备。它们还可以用于“超越摩尔”的应用,即云和认知计算,其中非常需要低电源和低功耗,例如云和认知计算中的应用。

进一步阅读

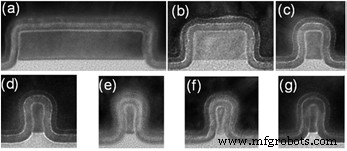

横断面Fin 和栅叠层的 Fin 宽度范围从 87nm (a) 到 3nm (g),以提高 SiGe Fin 的 Ge 含量。

在今年的 IEEE VLSI(超大规模集成)技术研讨会上,我们的团队展示了许多以使用具有 10nm 基本规则的 SiGe 为中心的新型器件、材料和集成创新,并作为解决缩放问题的途径以及我们去年制造的 7nm 测试节点的性能挑战。

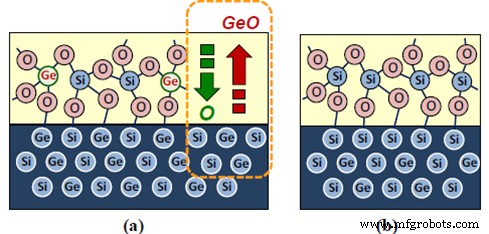

我们的演讲涵盖了缺陷控制的关键技术特征和基本流程创新;适用于SiGe FIN的栅极堆叠和界面层的创新;以及 SiGe FinFET 平台上的高级接触技术,在 VLSI 会议上的研究论文 T2.2 中进行了报道。 T4.3研究论文提出了创造性的选择性氧化锗清除工艺,以构建坚固的SiGe沟道界面层。

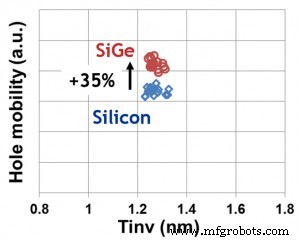

清晰的移动性SiGe Fin优于Si Fin,带来芯片级性能提升。

我们由 Pouya Hashemi 博士领导的研究专注于 SiGe FinFET 技术在未来更高性能节点上的可扩展性,也在 VLSI 上进行了展示。在 T9.3 研究论文中,我们报告了通过更高的 Ge 含量和更小的 Fin 宽度以及进一步的栅堆叠缩放来实现更高性能的可行性。 VLSI 研讨会参与者可以在 VLSI 网站上找到这些技术论文。您也可以加入他们的 Linkedin Group 以获取更多信息。

T2.2:具有用于 10 纳米及以上的高迁移率 SiGe 通道的 FINFET 技术

T4.3:用于高迁移率 Si/Si1-xGex CMOS 应用的 Si1-xGex 通道界面层的选择性 GeOx 清除

T9.3:具有高空穴迁移率和出色 SS 和可靠性的高 K/金属栅极高 Ge 含量应变 SiGe FinFET 替代品,在激进的 EOT ~7Å 和尺寸缩小至亚 4nm 鳍片宽度时

T7.2:用于先进技术的 Ti 和 NiPt/Ti 内衬硅化物触点

示意图本发明的选择性GeOx清除工艺(a)和具有SiGe沟道的无GeOx界面层(b)。

*-FinFET 指的是一种晶体管架构,将晶体管通道抬高,使其看起来像鳍)

Dechao Guo 是 IBM Research 的研究人员、主要发明者和高级设备设计与集成经理。

纳米材料