IBM 在 SPIE:超越 7nm 芯片的七项进步

当我们在 2015 年与我们的 GLOBALFOUNDRIES 和三星合作伙伴宣布业界首款功能性 7 纳米节点 (7nm) 测试芯片时,我们知道芯片达到“制造成熟度”的过程——或许最早在明年,会很快。随着这一努力在半导体行业加速推进,IBM 继续通过专注于 7nm 以外的下一个节点的挑战来突破边界。

我们的 IBM 团队将在本周的 2017 年国际光学与光子学会 (SPIE) 高级光刻会议上发表七篇论文专注于7nm节点以外的技术探索和使能。它从极紫外 (EUV) 光刻开始。

我们的 IBM 团队将在本周的 2017 年国际光学与光子学会 (SPIE) 高级光刻会议上发表七篇论文专注于7nm节点以外的技术探索和使能。它从极紫外 (EUV) 光刻开始。

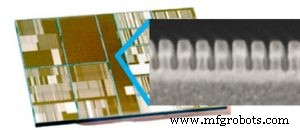

使用 7nm 芯片,我们现在正在创建与晶体管尺寸甚至晶体管之间的布线相关的设计,这些设计真正处于原子水平。为了在没有过于复杂的图案化方案的情况下实现这种缩放,EUV 是关键。在单次曝光中,EUV 可以创建以前的半导体图案化工艺无法获得的高分辨率图案。然而,实现 EUV 图案化需要专门的设备、工艺和专业知识,所有这些都可以在位于纽约州奥尔巴尼和纽约州约克敦高地的 IBM 研究实验室中找到。在 SPIE 上展示的这七项与 EUV 掩模(用于将电路设计印刷到硅晶片上的模板)和图案化材料(光激活“抗蚀剂”或抗蚀刻材料)相关的进步都可以被视为实现 7nm 技术的关键及以后:

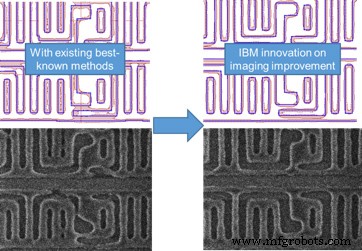

在7nm以上节点的设计意图优化:DTCO和EUVL随机缓解技术的交集 , Michael Crouse 表明,尽管他的演讲题目很大,但布线设计的微小变化可以极大地改善印刷条件。在图 1 中,他表明如果正确完成掩模形状的优化,可以在 7nm 节点及以上所需的最小尺寸上打印无破损的连续线。

图1 :使用 EUV 光刻演示的二维金属布线的对比度优化改进。通过右侧所示的改进类型,可以更稳健地打印比 7nm 节点小 20-30{ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887} 的特征,并且可以更稳健地印刷物理/电气可变性。

在 EUV 光刻中替代掩模堆叠的研究中, Martin Burkhardt 模拟了目前未用于 EUV 掩模的新材料的性能。通过考虑整个元素周期表,他能够说明提供更好对比度的 EUV 掩模在我们的掌握之中。实际上,使用其中一些材料制造掩模将允许在硅晶片上获得更高保真度的图案,而无需进一步改变 EUV 技术,从而使该行业能够轻松扩展到 7nm 以上。

EUV光刻线边缘和线宽粗糙度综合分析 , Ravi Bonam 说明了如何清楚地表征布线中的小缺陷和摆动,并在此过程中显示哪些条件会产生最直的特征,这对于提高 EUV 图案化工艺的可制造性以及芯片的性能和良率至关重要。

EUV 抗蚀剂-无机硬掩模相互作用的基础 , Dario Goldfarb 希望通过改善这些薄膜之间界面的物理和化学相互作用来改进图案材料薄膜堆栈(从图案到晶片的转移点),这些薄膜通常不喜欢相互粘连。他利用这种理解来创建特定的化学相互作用以将这些材料结合在一起(如图 2 所示),这对于确保这些微小的 EUV 图案形状能够保持足够长的时间以将其图案转移到下面的基板中至关重要。

图2 :以前无法在无机硅硬掩模上形成图案的 EUV 抗蚀剂现在可以在针对抗蚀剂/硬掩模组合量身定制的表面定制后清晰地形成图案。

与 Dario Goldfarb 的演讲主题相似,Indira Seshadri 演示了使用聚合物刷作为粘合促进层的超薄 EUV 图案化堆栈 ,通过使用类似聚合物的材料在微小的 EUV 图案特征和下面的基板之间架起桥梁,这些非常高分辨率的图案可以蚀刻到下面的基板中并保持预期的设计形状,这是确保在这些长度下可生产芯片的关键秤。

有这么多新的薄膜解决方案在起作用,在研究阶段早期识别和改进可制造工艺的能力是关键。在题为降低复合 EUV 图案化薄膜堆栈中的缺陷密度的演讲中 , Luciana Meli 展示了系统案例研究,使用混合可用的缺陷检测技术,展示了实现 7 纳米及以上 EUV 可制造性所需的低缺陷率所需的工艺和材料改进。

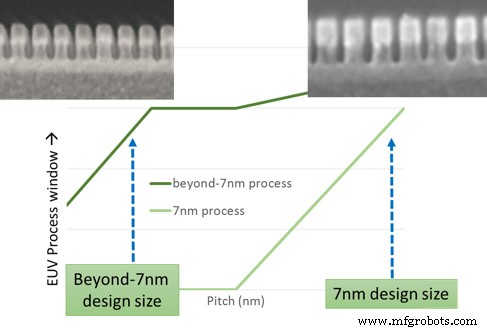

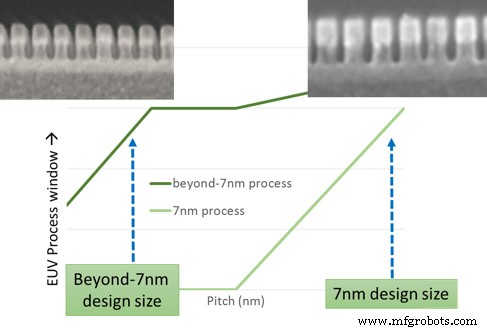

Anuja De Silva 将把许多成像和材料改进的概念结合在一起,发表题为EUV 光刻的单曝光图案化开发的演讲 ,展示了超过 7nm 节点所需的 30nm 及以下尺寸的布线电路的成功图案化。实现这一目标的能力代表了与 7nm 节点最初可用的能力相比的巨大飞跃(见图 3),并且实际上可以改进 7nm 节点本身,尽管她将强调仍然存在的挑战,以实现在7nm以上技术所需的尺寸。

一个 7nm 芯片在大约指甲大小的空间内有 200 亿个晶体管。它们将进入系统和设备,扩展功能和摩尔定律,以完成数据分析、认知计算以及下一代移动应用程序中要求更高的任务。今年在 SPIE 上展示的工作推动行业更接近于图案化解决方案,这些解决方案不仅使 7nm 工艺在单次曝光 EUV 下更加稳健,而且还能够进一步扩展以在未来几年实现更多的功率/性能优势。

图3 :在图案化工艺的多个方面进行创新,使 IBM 能够提供整体的图案化工艺能力,提供 7 纳米节点以外所需的特征尺寸。

在 2017 SPIE 上的其他 IBM 演示

超过 7nm 节点的设计意图优化:DTCO 和 EUVL 随机缓解技术的交集 、迈克尔·克劳斯、妮可·索尔尼尔、德伦·邓恩

EUV 光刻中交替掩模堆叠的研究 , 马丁·伯克哈特

使用非相干内核分解 TCC 以更快地计算光刻图像, 艾伦·罗森布鲁斯

通过 PEALD 沉积开发含钛硬掩模, 阿努贾·德席尔瓦

用于逻辑和内存应用的 DSA 模式选项, 刘查理

使用 EUV 测试车在亚 60nm 处进行 DSA 收缩工艺和 CD 整流效果的电学研究, 程驰

在高级节点中实现真正的叠加, 乔成高

全有机高χ嵌段共聚物取向控制的无面漆策略, 丹·桑德斯

相关基本规则系统(设计弧)的识别和可靠性敏感性分析, 埃里克·伊士曼

用于设计技术协同优化的高级快速 3D DSA 模型开发和校准, 赖卡菲

RIE 气体对平版印刷薄膜的意外影响, 马丁·格洛德

使用混合计量和机器学习进行电气测试预测, 玛丽·布雷顿

通过光子波导应用的 RIE 优化降低 Si 和 SiN 中的 LER, 内森·马查克

相变存储器应用的定向自组装图案化策略, R.布鲁斯

用于多通道环栅 (GAA) 器件工艺集成的材料表征, 拉惹穆廷提

EUV光刻线边缘和线宽粗糙度综合分析, 拉维·波南

纳米材料