异步计数器

在上一节中,我们看到了使用一个 J-K 触发器的电路,该触发器以两位二进制序列向后计数,从 11 到 10 到 01 到 00。

因为希望有一个可以向前计数的电路 而不仅仅是向后,值得再次检查正向计数序列并寻找更多可能指示如何构建此类电路的模式。

由于我们知道二进制计数序列遵循八度(因子 2)分频模式,并且为“切换”模式设置的 JK 触发器多谐振荡器能够执行这种类型的分频,我们可以设想一个电路由几个JK触发器组成,级联产生四位输出。

我们面临的主要问题是确定如何 将这些触发器连接在一起,以便它们在正确的时间触发以产生正确的二进制序列。

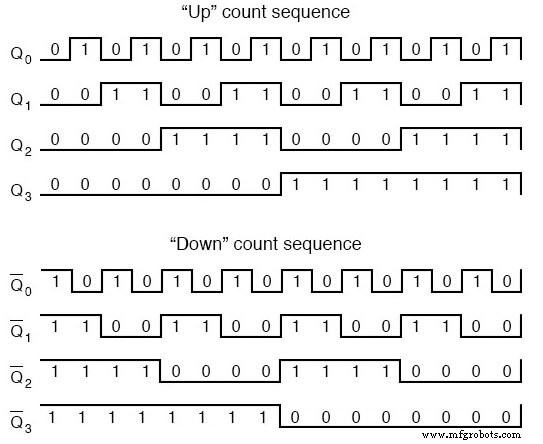

检查以下二进制计数序列,注意在 0 和 1 之间的位“切换”之前的模式:

请注意,这个四位序列中的每个位在其之前的位(具有较低重要性的位或位置权重)在特定方向上切换时切换:从 1 到 0。

小箭头表示序列中位切换的那些点,箭头指向前一位从“高”(1) 状态转换为“低”(0) 状态:

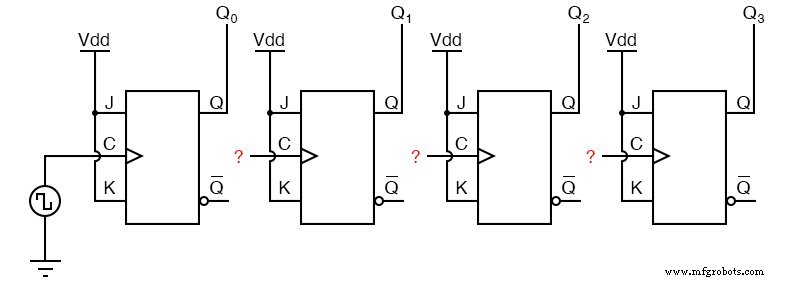

从以始终处于“切换”模式的方式连接的四个 JK 触发器开始,我们需要确定如何以这种方式连接时钟输入,以便每个后续位在其之前的位从 1 转换时触发到 0。

每个触发器的 Q 输出将作为最终四位计数的相应二进制位:

如果我们使用负沿触发的触发器(时钟输入上的气泡符号),我们可以简单地将每个触发器的时钟输入连接到它之前触发器的 Q 输出,这样当之前的位它从 1 变为 0,该信号的“下降沿”将“计时”下一个触发器以切换下一位:

四位“向上”计数器

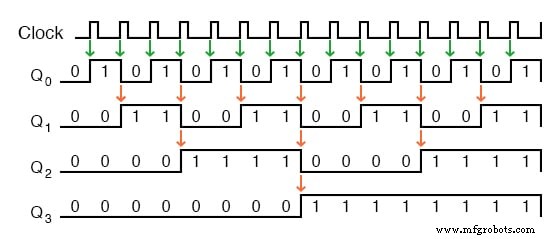

当由来自振荡器的重复脉冲源“计时”时,该电路将产生以下输出波形:

第一个触发器(带有 Q0 输出的触发器)有一个正沿触发时钟输入,因此它在时钟信号的每个上升沿触发。

注意本例中时钟信号的占空比小于 50%。

我以这种方式展示了信号,目的是展示时钟信号如何不需要对称即可在我们的四位二进制序列中获得可靠、“干净”的输出位。

在本章所示的第一个触发器电路中,我使用时钟信号本身作为输出位之一。

然而,这在计数器设计中是一种不好的做法,因为它需要使用占空比为 50% 的方波信号(“高”时间 =“低”时间)以获得一个计数序列,其中每一步暂停相同的时间。

然而,对于每个输出位使用一个 J-K 触发器,我们就不必拥有对称的时钟信号,实际上允许使用任何种类的高/低波形来递增计数序列。

如脉冲图中所有其他箭头所示,每个后续输出位都通过前一位从“高”(1) 转换为“低”(0) 的动作触发。

这是生成“向上”计数序列所必需的模式。

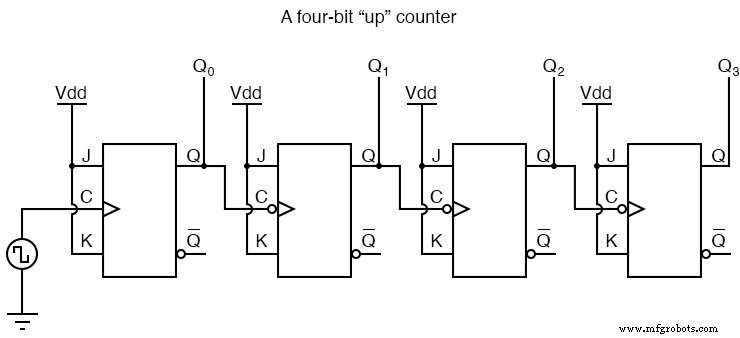

使用正沿触发触发器生成“向上”序列的一个不太明显的解决方案是使用前一个触发器的 Q' 输出而不是 Q 输出为每个触发器“计时”。

由于 Q' 输出总是与 JK 触发器上的 Q 输出完全相反的状态(这种类型的触发器没有无效状态),Q 输出上的高到低转换将伴随Q' 输出的低到高转换。

换句话说,每次触发器的 Q 输出从 1 转换为 0 时,同一个触发器的 Q' 输出将从 0 转换为 1,提供我们需要切换的正向时钟脉冲在正确的时刻正沿触发触发器:

替代的四位“向上”计数器

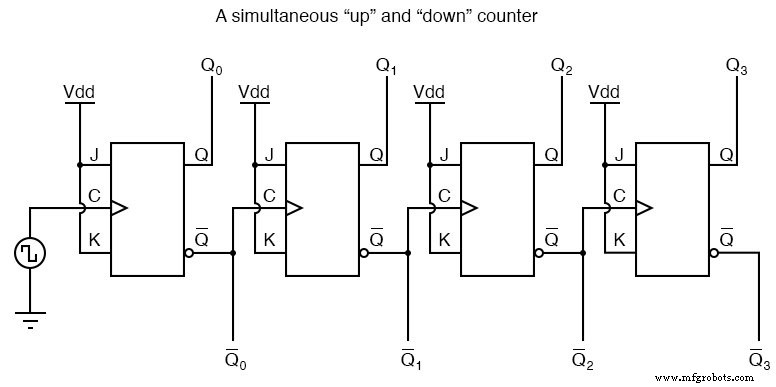

我们可以扩展这两个计数器电路中任何一个的功能的一种方法是将 Q' 输出视为另一组四位二进制位。

如果我们检查这种电路的脉冲图,我们会看到 Q' 输出产生向下 - 计数序列,而 Q 输出生成一个 up -计数顺序:

同时“向上”和“向下”计数器

不幸的是,迄今为止显示的所有计数器电路都有一个共同的问题:纹波

在某些类型的二进制加法器和数据转换电路中可以看到这种影响,这是由于级联门之间的累积传播延迟造成的。

当触发器的 Q 输出从 1 转换为 0 时,它命令下一个触发器切换。

如果下一个触发器切换是从 1 到 0 的转换,它会命令它后面的触发器也切换,依此类推。

然而,由于在切换命令(时钟脉冲)和实际切换响应(Q 和 Q' 输出改变状态)之间总是存在一些小量的传播延迟,因此任何后续要切换的触发器将切换一段时间 之后 第一个触发器已触发。

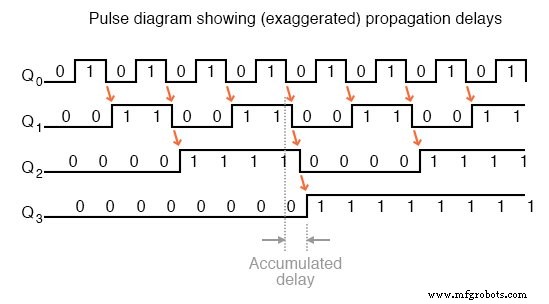

因此,当多个位在二进制计数序列中切换时,它们不会完全同时切换:

异步计数器电路的缺点:传播延迟

如您所见,随着给定时钟脉冲切换的位越多,从 LSB 到 MSB 的累积延迟时间就越严重。

当时钟脉冲出现在这样的转换点时(例如,从 0111 到 1000 的转换),输出位将按顺序从 LSB 到 MSB“波动”,因为每个后续位都切换并命令下一位切换,在每个位切换之间有少量的传播延迟。

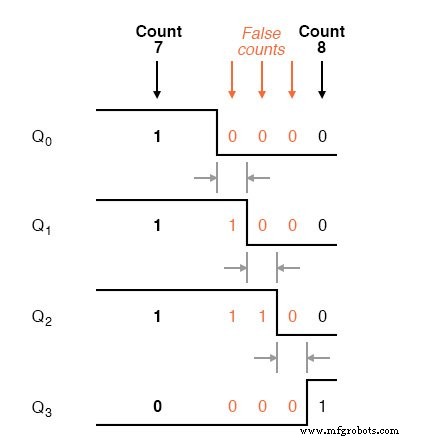

如果我们在从 0111 过渡到 1000 的过程中近距离观察这个效果,我们可以看到会有false 在“涟漪”效应发生的短时间内产生的输出计数:

计数器电路不是从“0111”输出干净地转换到“1000”输出,而是很快地从 0111 到 0110 到 0100 到 0000 到 1000,或从 7 到 6 到 4 到 0 然后到 8. 这种行为使计数器电路获得纹波计数器的名称 , 或 异步计数器 .

选通信号计数器电路

在许多应用中,这种影响是可以容忍的,因为纹波发生得非常非常快(这里夸大了延迟的宽度,以帮助理解这种影响)。

例如,如果我们只想用计数器的输出驱动一组发光二极管 (LED),那么这种短暂的纹波就根本没有意义。

然而,如果我们希望使用这个计数器来驱动多路复用器的“选择”输入,在微处理器(计算机)电路中索引一个内存指针,或者执行一些其他任务,其中错误输出可能导致虚假错误,这是不可接受的.

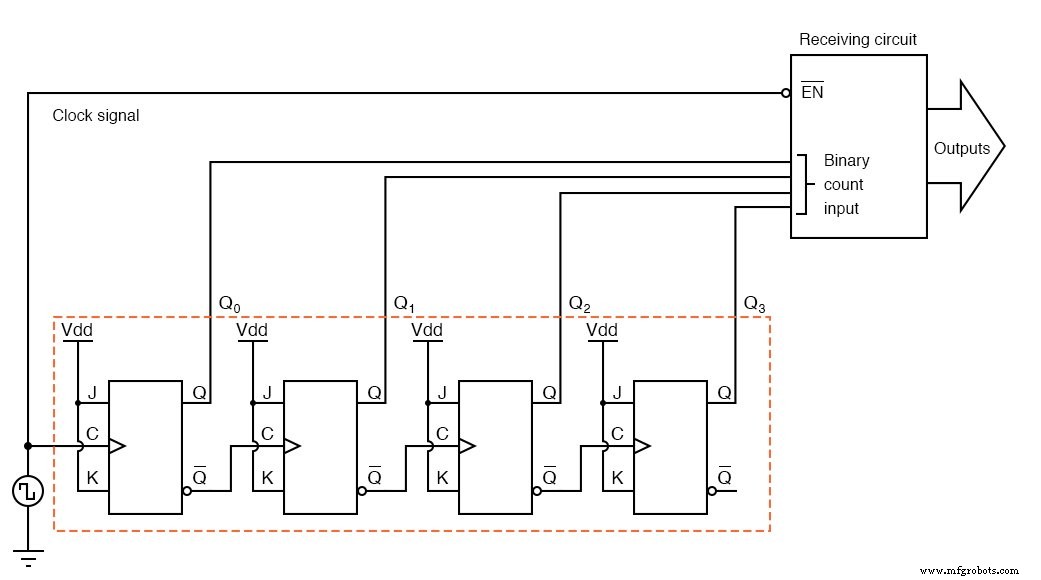

有一种方法可以在对错误产生的纹波输出敏感的应用中使用这种类型的计数器电路,它涉及一种称为选通的原理 .

大多数解码器和多路复用器电路都配备了至少一个称为“启用”的输入。

只有当使能输入被激活时,这种电路的输出才会被激活。

我们可以将此启用输入用于 strobe 电路接收纹波计数器的输出,以便在计数器输出可能出现纹波的短暂时间段内禁用(从而不响应计数器输出),并且仅在自上一个时钟脉冲后经过足够长的时间后才启用所有的涟漪都将停止。

大多数情况下,选通信号可以是驱动计数器电路的同一个时钟脉冲:

使用低电平有效的使能输入,只有当时钟信号为“低”时,接收电路才会响应四位计数器电路的二进制计数。

一旦时钟脉冲变为“高”,接收电路就停止响应计数器电路的输出。

由于计数器电路是上升沿触发(由第一 触发器时钟输入),所有计数动作都发生在时钟信号从低到高的转换时,这意味着接收电路将在计数器电路的四个输出位发生任何翻转之前被禁用。

接收电路在时钟信号回到低电平之前不会被使能,这应该是之后足够长的时间 所有波纹都不再是“安全的”,以允许新计数对接收电路产生影响。

这里的关键参数是时钟信号的“高”时间:它必须至少与计数器电路的最大预期纹波周期一样长。

否则,时钟信号将过早地使能接收电路,而一些纹波仍在发生。

异步计数器电路的缺点:限速

异步或纹波计数器电路的另一个缺点是速度有限。

虽然所有门电路在最大信号频率方面都受到限制,但异步计数器电路的设计通过增加传播延迟使这个问题更加复杂。

因此,即使在接收电路中使用选通,异步计数器电路也不能以高于允许最大可能累积传播延迟在下一个脉冲之前消逝的频率更高的频率计时。

这个问题的解决方案是一个完全避免纹波的计数器电路。

这样的计数器电路将无需在任何使用计数器输出作为输入的数字电路中设计“选通”功能,并且还可以享受比其异步等效电路更高的运行速度。

这种计数器电路的设计是下一节的主题。

评论:

- “向上”计数器可以通过将正沿触发 J-K 触发器的时钟输入连接到前面触发器的 Q' 输出来实现。另一种方法是使用负沿触发触发器,将时钟输入连接到前面触发器的 Q 输出。在任何一种情况下,所有触发器的 J 和 K 输入都连接到 Vcc 或 Vdd,以便始终为“高”。

- 由级联 J-K 触发器制成的计数器电路,其中每个时钟输入接收来自前一个触发器输出的脉冲,总是表现出波纹效应 ,其中在计数序列的某些步骤之间生成错误的输出计数。这些类型的计数器电路称为异步计数器 , 或 波纹计数器 .

- 频闪 是一种应用于接收异步(纹波)计数器输出的电路的技术,因此纹波时间期间产生的错误计数不会产生不良影响。本质上,启用 这种电路的输入连接到计数器的时钟脉冲,这样它只有在计数器输出没有变化时才启用,在出现纹波的计数器输出变化期间将被禁用。

相关工作表:

- 波纹计数器工作表

工业技术