耗尽型 IGFET

绝缘栅场效应晶体管是单极器件,就像 JFET 一样:也就是说,受控电流不必穿过 PN 结。晶体管内部有一个 PN 结,但它的唯一目的是提供非导电耗尽区,用于限制通过沟道的电流。

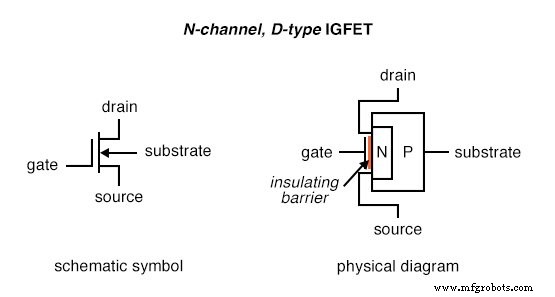

示意图符号和物理图

这是“耗尽”型 N 沟道 IGFET 的示意图:

请注意源极和漏极引线如何连接到 N 沟道的任一端,以及栅极引线如何连接到通过薄绝缘屏障与沟道隔开的金属板上。该屏障有时由二氧化硅(沙子中的主要化合物)制成,它是一种非常好的绝缘体。由于这种金属(栅极)-氧化物(势垒)-半导体(沟道)结构,IGFET 有时被称为 MOSFET。不过,还有其他类型的 IGFET 结构,因此“IGFET”是这类晶体管的更好描述。

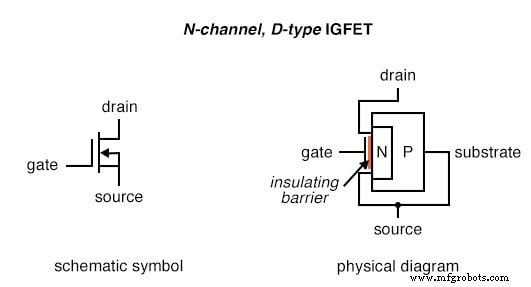

还要注意 IGFET 有四个连接。在实践中,基板引线直接连接到源极引线,使两者在电气上共用。通常,这种连接是在内部与 IGFET 进行的,消除了单独的衬底连接,从而产生了原理图符号略有不同的三端器件:

由于源极和衬底彼此共用,IGFET 的 N 层和 P 层最终通过外线直接相互连接。这种连接可防止在 PN 结上施加任何电压。结果,在两种材料之间存在耗尽区,但它永远不会膨胀或塌陷。 JFET的工作是基于PN结耗尽区的扩大,但在IGFET这里是不可能发生的,所以IGFET的工作必须基于不同的效果。

确实如此,因为当在栅极和源极之间施加控制电压时,由于耗尽区靠近或远离栅极,沟道的电导率发生变化。换句话说,沟道的有效宽度与 JFET 一样发生变化,但沟道宽度的这种变化是由于耗尽区位移而不是耗尽区扩大造成的。

N 沟道 IGFET

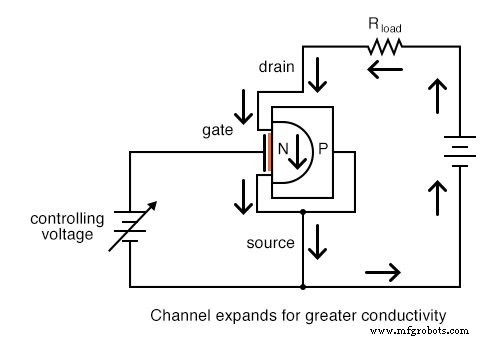

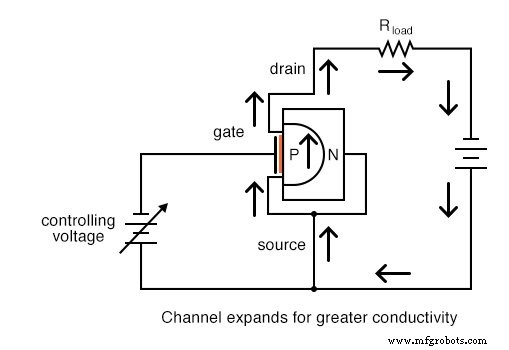

在 N 沟道 IGFET 中,在栅极施加正 (+) 和向源极施加负 (-) 的控制电压具有排斥 PN 结的耗尽区、扩展 N 型沟道和增加导电性的作用:

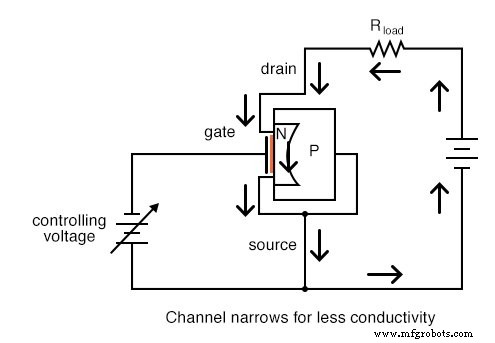

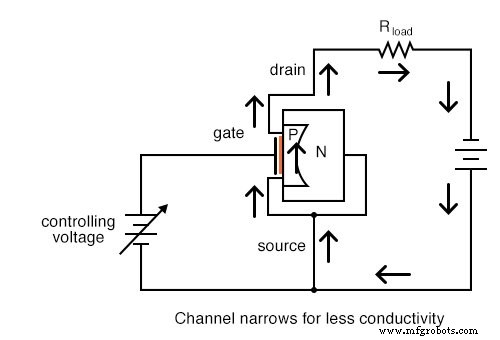

反转控制电压的极性会产生相反的效果,吸引耗尽区并使沟道变窄,从而降低沟道电导率:

绝缘栅允许控制任何极性的电压,而不会像 JFET 那样存在正向偏置结的危险。这种类型的 IGFET 虽然称为“耗尽型”,但实际上具有耗尽(通道变窄)或增强(通道扩展)通道的能力。输入电压极性决定了通道会受到何种影响。

了解哪种极性具有哪种效果并不像看起来那么困难。关键是要考虑沟道中使用的半导体掺杂类型(N 沟道还是 P 沟道?),然后将该掺杂类型与通过源极引线连接到沟道的输入电压源侧相关联。如果 IGFET 是 N 沟道,并且输入电压的连接使得正极 (+) 侧在栅极上,而负极 (-) 侧在源极上,则随着额外电子在栅极上积聚,沟道将增强介电势垒的通道侧。想一想,“负 (-) 与 N 型相关,从而用正确类型的电荷载流子(电子)增强通道并使其更具导电性。”相反,如果输入电压以另一种方式连接到 N 沟道 IGFET,因此负极 (-) 连接到栅极,而正极 (+) 连接到源极,自由电子将从沟道中“抢夺”为栅极沟道电容器充电,从而耗尽多数电荷载流子的沟道并使其导电性降低。

P 沟道 IGFET

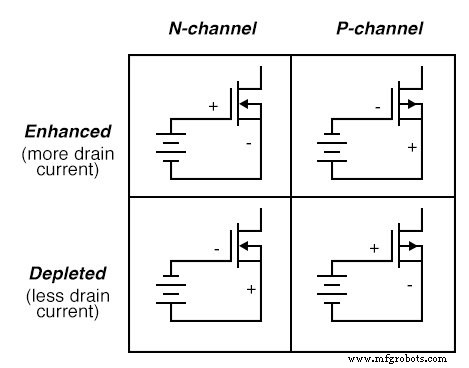

对于 P 沟道 IGFET,输入电压极性和沟道效应遵循相同的规则。也就是说,它需要与 N 沟道 IGFET 相反的极性才能耗尽或增强:

用标准 IGFET 符号说明正确的偏置极性:

当栅极和源极之间施加零电压时,IGFET 将在源极和漏极之间传导电流,但不会像通过适当的栅极电压增强电流那样大。这将耗尽型或简单的 D 型 IGFET 置于晶体管世界中的一个类别中。双极结型晶体管是常关型器件:没有基极电流,它们阻止任何电流通过集电极。结型场效应晶体管是常开器件:在施加零栅极到源极电压的情况下,它们允许最大漏极电流(实际上,您可以通过在栅极和源,但在实践中绝不应该这样做,以免损坏其脆弱的 PN 结)。然而,D 型 IGFET 通常是半导通器件:没有栅源电压,它们的导通电平介于截止和完全饱和之间。此外,它们可以承受任何极性的栅极-源极电压,PN 结不受绝缘屏障的损坏,尤其是源极和衬底之间的直接连接,防止了结上的任何电压差。

具有讽刺意味的是,D 型 IGFET 的导电行为与三极管/四极管/五极管种类的电子管惊人地相似。这些设备是压控电流调节器,同样允许电流通过它们并施加零控制电压。一种极性(栅极负极和阴极正极)的控制电压会降低通过管的导电性,而另一种极性(栅极正极和阴极负极)的电压会增强导电性。我觉得奇怪的是,后来发明的一个晶体管设计表现出与第一个有源(电子)设备相同的基本特性。

D型IGFET的SPICE仿真

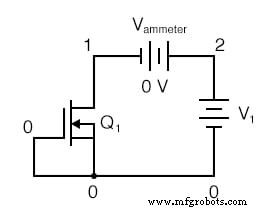

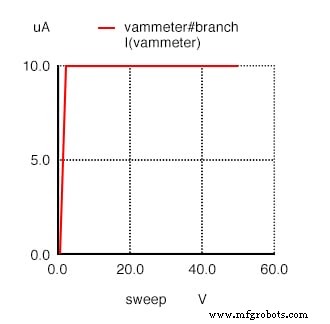

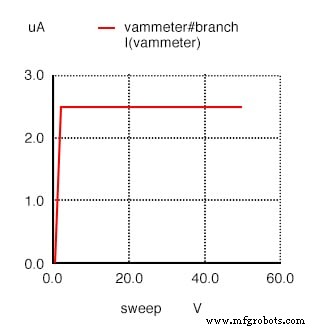

一些 SPICE 分析将证明 D 型 IGFET 的电流调节行为。首先,在零输入电压(栅极与源极短路)和电源电压范围为 0 至 50 伏的情况下进行测试。图形显示漏极电流:

n 通道 igfet 特性曲线 m1 1 0 0 0 mod1 电流表 2 1 dc 0 v1 2 0 .model mod1 nmos vto=-1 .dc v1 0 50 2 .plot dc i(vammeter) .end

正如任何晶体管所预期的那样,受控电流在很宽的电源电压范围内保持稳定在规定值。在这种情况下,该调节点为 10 µA (1.000E-05 Amps)。现在让我们看看当我们向栅极施加负电压(参考源极)并在 0 到 50 伏的相同范围内扫描电源时会发生什么:

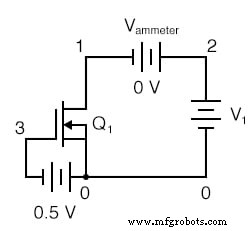

n 通道 igfet 特性曲线 m1 1 3 0 0 mod1 vin 0 3 dc 0.5 vammeter 2 1 dc 0 v1 2 0 .model mod1 nmos vto=-1 .dc v1 0 50 2 .plot dc i(vammeter) .end

毫不奇怪,漏极电流现在调节在 2.5 µA 的较低值(从零输入电压的 10 µA 降低)。现在让我们施加另一个极性的输入电压,以增强 IGFET:

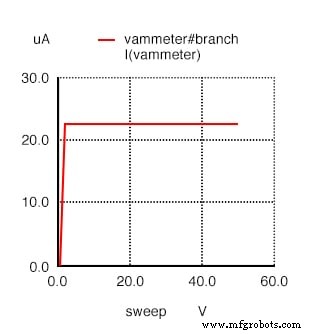

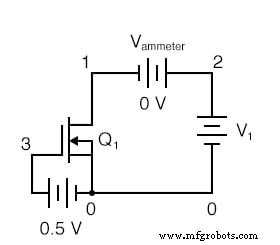

n 通道 igfet 特性曲线 m1 1 3 0 0 mod1 vin 3 0 dc 0.5 vammeter 2 1 dc 0 v1 2 0 .model mod1 nmos vto=-1 .dc v1 0 50 2 .plot dc i(vammeter) .end

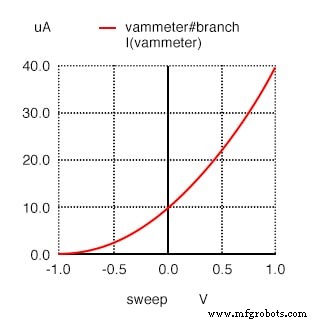

随着晶体管由小控制电压增强,漏极电流现在增加了 22.5 µA (2.250E-05 Amps)。从这三组电压和电流图可以明显看出,漏电流与栅源电压的关系是非线性的,就像 JFET 一样。在 1/2 伏的耗尽电压下,漏极电流为 2.5 µA;输入 0 伏时,漏极电流高达 10 µA;使用 1/2 伏的增强电压,电流为 22.5 µA。为了更好地理解这种非线性,我们可以使用 SPICE 绘制输入电压值范围内的漏极电流,从负(耗尽)数字扫描到正(增强)数字,将 V1 的电源电压保持在一个常数值:

n 通道 igfet m1 1 3 0 0 mod1 vin 3 0 vammeter 2 1 dc 0 v1 2 0 dc 24 .model mod1 nmos vto=-1 .dc vin -1 1 0.1 .plot dc i(vammeter) .end

正如 JFET 一样,IGFET 的这种固有非线性有可能导致放大器电路失真,因为输入信号不会在输出端以 100% 的准确度再现。还要注意,在耗尽方向上大约 1 伏的栅源电压能够夹断沟道,因此实际上没有漏电流。 D 型 IGFET 与 JFET 一样,具有一定的夹断电压额定值。此额定值因晶体管的精确独特性而异,并且可能与我们此处的模拟不同。

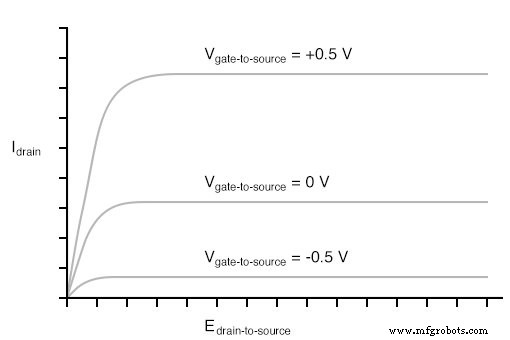

IGFET的特性曲线

绘制一组 IGFET 的特性曲线,我们看到一个与 JFET 不同的模式:

相关工作表:

- 绝缘栅场效应晶体管工作表

工业技术