Ripple Carry Adder:你需要知道的一切

逻辑电路可以依靠纹波进位加法器将 n 位值加在一起。因此,这种数字电路实现在许多应用中提供了有用的特性。但是,由于计算过程缓慢,它也表现出延迟的性能。这通常涉及等待每个全加器级将位波动到下一个全加器级。这样的过程不断重复,直到结束,提供结果。

理解波纹进位加法器似乎有点令人困惑。考虑到这一点,我们将本文放在一起,以帮助您获得有关此主题的更多知识。那么让我们开始吧!

什么是瑞波进位加法器?

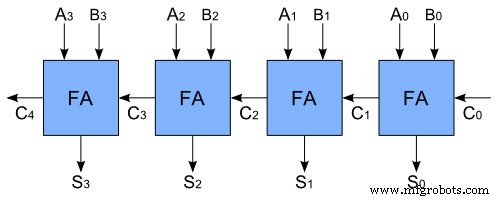

纹波进位加法器用作将两个二进制 n 位数相加并提供结果的数字电路。它的结构由几个全加器组成,每个全加器都以级联方式连接。这样,一个全加器的进位输出连接到下一个全加器输入。

4 位纹波携带加法器的示意图。

来源:维基共享资源

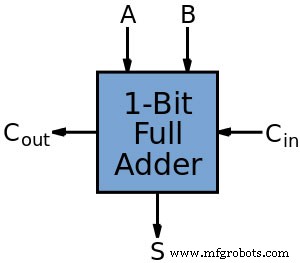

全加器代表一个逻辑电路,旨在将三个输入相加,同时生成两个输出。更具体地说,两个输入用作 A 和 B,而第三个表示一个进位位。 (C-IN) 同时,一个输出代表一个进位位(C-OUT),另一个代表一个和位(S)。最终,一个全加器电路可以连接到八个输入以形成一个字节宽的加法器。这将一个进位从一个加法器级联到下一个加法器。将两个半加器电路连接在一起将形成一个全加器。

一个完整的加法器逻辑图

来源:维基共享资源

瑞波进位加法器工作原理

每个进位通过一个全加器阶段生成,然后通过其输入进入下一个全加器。整个过程继续进行,直到到达最终的全加器。结果,每个进位输出位都会波动到下一个全加器级。总体而言,最关键的操作是将每个输入位序列相加,例如4位加法器、8位加法器、16位加法器等。

由于逻辑电路的传播延迟,求和位和进位位保持无效,直到进位阶段发生。由于输入和输出之间经过的时间量,通常会发生传播延迟。例如,当非门输入设置为 0 时,输出将配置为 1,等等。传播延迟定义了在输出设置为零和输入配置为 1 之间经过的时间。此外,进位传播延迟定义了接收进位信号和执行进位信号之间经过的时间。

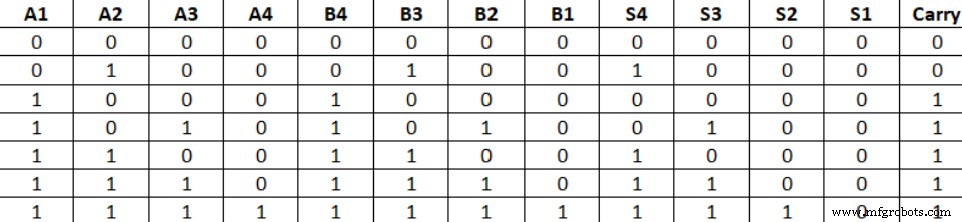

瑞波进位加法器真值表

如下所示的真值表确定了纹波进位加法器中所有输入的每个输出值。

波纹带有加法器真值表。

纹波进位加法器 VHDL 代码和 Verilog 代码

要实现波纹进位加法器,您将需要 VHDL 代码和 Verilog 代码。提供了两个示例。第一个涉及两位纹波进位加法器。同时,另一个示例生成了一个波纹进位加法器,它收集每个输入宽度作为参数。

波纹进位加法器应用程序

时钟包含纹波进位加法器

- 对两个 N 位值执行加法

- 数字信号处理和微处理器

- 计时器

- 计算器

- 时钟

Ripple Carries Adder 的优缺点

优势

纹波进位加法器很便宜。

来源:维基共享资源

- 通过 n 位加法提供准确的结果

- 简单的设计和开发流程

- 物美价廉

缺点

延迟对其整体功能造成不便

- 它一次只允许一个全加器运行

- 进位延迟导致它运行缓慢

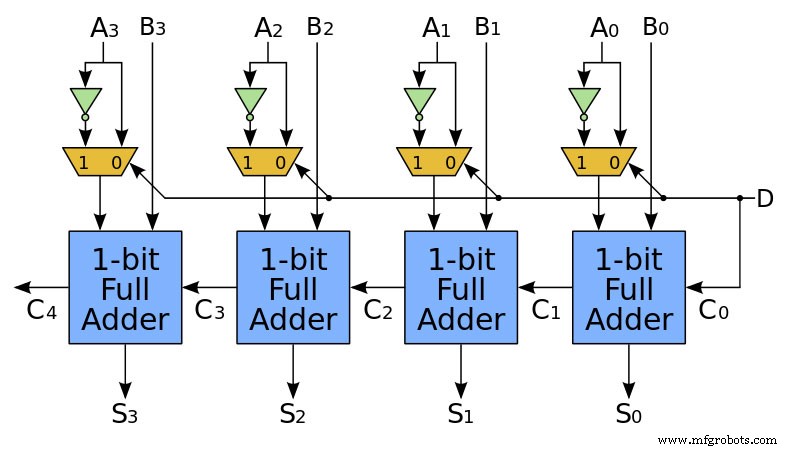

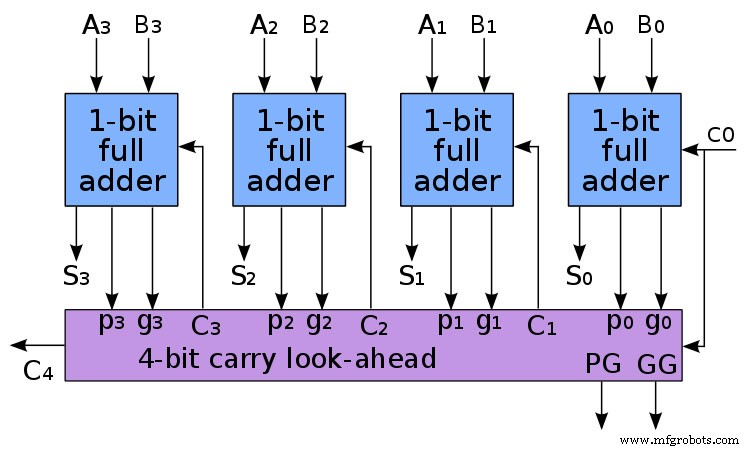

进行前瞻加法器

进位超前逻辑在达到总和之前计算进位位,有效地减少了时间延迟。这发生在通过两种方法生成进位信号之后。第一个涉及等于一的 a 和 b 位。同时,第二种方法涉及进位和等于 1 的 a 或 b 位。这些位在前一阶段实现,而进位则在加法器的开头开始。

进行前瞻加法器原理图。

来源:维基共享资源

在纹波进位加法器中,每个全加器在计算总和之前将进位位处理到下一个加法器。因此,该过程会导致很长的延迟。

总结

总体而言,进位纹波加法器提供了在数字电路中将两个 n 位数字相加的能力。尽管过程缓慢,但它仍然具有有用的应用程序,这些应用程序基本上有助于数字信号处理。以这种方式,纹波进位加法器将进位位纹波到每个全加器级,直到它到达最终的全加器。此时,它将执行所需的计算。但是,超前进位加法器可以更快地完成此计算,因为它使用了不同的技术。从而减少延迟时间。

您对纹波进位加法器有任何疑问吗?欢迎随时联系我们!

工业技术