Verilog n 位双向移位寄存器

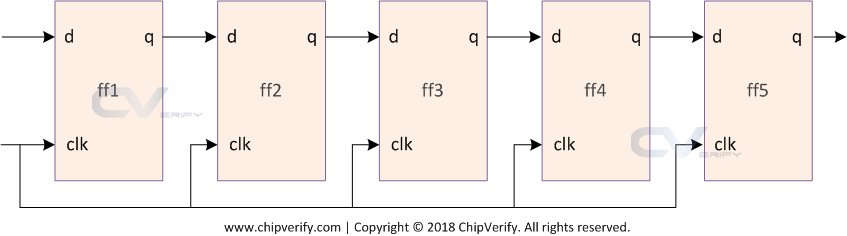

在数字电子学中,移位寄存器 是触发器的级联,其中输出引脚 q 一个触发器连接到下一个触发器的数据输入引脚 (d)。因为所有触发器都在同一个时钟上工作,所以存储在移位寄存器中的位数组将移位一个位置。例如,如果一个 5 位右移位寄存器的初始值为 10110,并且移位寄存器的输入绑定为 0,那么下一个模式将是 01011 和下一个 00101。

<无脚本>

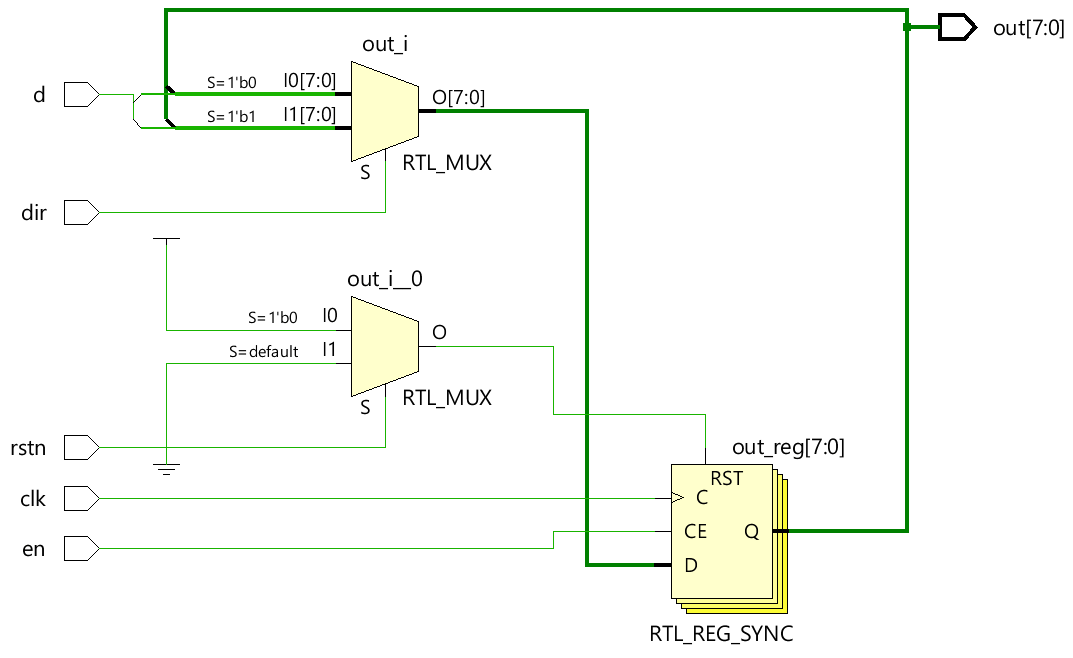

设计

此移位寄存器设计有五个输入和一个 n 位输出,该设计使用 parameter 进行参数化 MSB 表示移位寄存器的宽度。如果 n 为 4,则它成为一个 4 位移位寄存器。如果n为8,则成为8位移位寄存器。

这个移位寄存器有几个关键特性:

- 可以通过驱动设计的en pin来启用或禁用

- 在驱动 dir 时可以左右移动

- rstn拉低,移位寄存器复位,输出为0

- 移位寄存器的输入数据值可由d管脚控制

module shift_reg #(parameter MSB=8) ( input d, // Declare input for data to the first flop in the shift register

input clk, // Declare input for clock to all flops in the shift register

input en, // Declare input for enable to switch the shift register on/off

input dir, // Declare input to shift in either left or right direction

input rstn, // Declare input to reset the register to a default value

output reg [MSB-1:0] out); // Declare output to read out the current value of all flops in this register

// This always block will "always" be triggered on the rising edge of clock

// Once it enters the block, it will first check to see if reset is 0 and if yes then reset register

// If no, then check to see if the shift register is enabled

// If no => maintain previous output. If yes, then shift based on the requested direction

always @ (posedge clk)

if (!rstn)

out <= 0;

else begin

if (en)

case (dir)

0 : out <= {out[MSB-2:0], d};

1 : out <= {d, out[MSB-1:1]};

endcase

else

out <= out;

end

endmodule

硬件示意图

<无脚本>

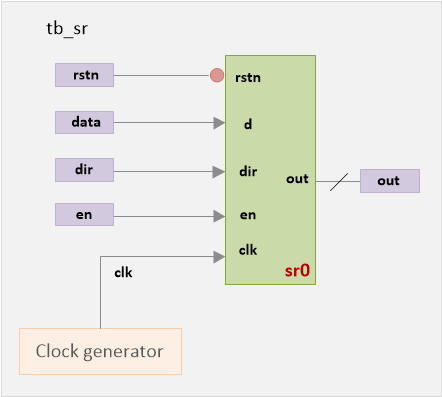

测试台

测试台用于验证该移位寄存器的功能。设计实例化到顶部module 并且输入以不同的值驱动。每个输入的设计行为都可以在输出引脚上观察到。

module tb_sr;

parameter MSB = 16; // [Optional] Declare a parameter to represent number of bits in shift register

reg data; // Declare a variable to drive d-input of design

reg clk; // Declare a variable to drive clock to the design

reg en; // Declare a variable to drive enable to the design

reg dir; // Declare a variable to drive direction of shift registe

reg rstn; // Declare a variable to drive reset to the design

wire [MSB-1:0] out; // Declare a wire to capture output from the design

// Instantiate design (16-bit shift register) by passing MSB and connect with TB signals

shift_reg #(MSB) sr0 ( .d (data),

.clk (clk),

.en (en),

.dir (dir),

.rstn (rstn),

.out (out));

// Generate clock time period = 20ns, freq => 50MHz

always #10 clk = ~clk;

// Initialize variables to default values at time 0

initial begin

clk <= 0;

en <= 0;

dir <= 0;

rstn <= 0;

data <= 'h1;

end

// Drive main stimulus to the design to verify if this works

initial begin

// 1. Apply reset and deassert reset after some time

rstn <= 0;

#20 rstn <= 1;

en <= 1;

// 2. For 7 clocks, drive alternate values to data pin

repeat (7) @ (posedge clk)

data <= ~data;

// 4. Shift direction and drive alternate value to data pin for another 7 clocks

#10 dir <= 1;

repeat (7) @ (posedge clk)

data <= ~data;

// 5. Drive nothing for next 7 clocks, allow shift register to simply shift based on dir

repeat (7) @ (posedge clk);

// 6. Finish the simulation

$finish;

end

// Monitor values of these variables and print them into the logfile for debug

initial

$monitor ("rstn=%0b data=%b, en=%0b, dir=%0b, out=%b", rstn, data, en, dir, out);

endmodule

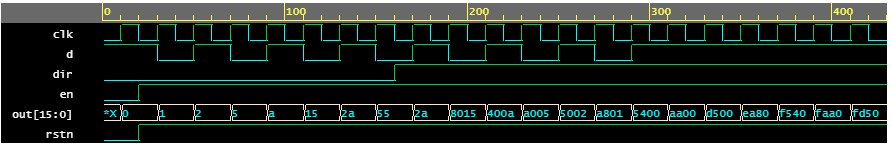

启用移位寄存器的时间在下面给出的日志中以绿色突出显示。它改变方向的时间以黄色突出显示。数据输入引脚保持不变的时间以蓝色突出显示。

模拟日志ncsim> run rstn=0 data=1, en=0, dir=0, out=xxxxxxxxxxxxxxxx rstn=0 data=1, en=0, dir=0, out=0000000000000000 rstn=1 data=1, en=1, dir=0, out=0000000000000000 rstn=1 data=0, en=1, dir=0, out=0000000000000001 rstn=1 data=1, en=1, dir=0, out=0000000000000010 rstn=1 data=0, en=1, dir=0, out=0000000000000101 rstn=1 data=1, en=1, dir=0, out=0000000000001010 rstn=1 data=0, en=1, dir=0, out=0000000000010101 rstn=1 data=1, en=1, dir=0, out=0000000000101010 rstn=1 data=0, en=1, dir=0, out=0000000001010101 rstn=1 data=0, en=1, dir=1, out=0000000001010101 rstn=1 data=1, en=1, dir=1, out=0000000000101010 rstn=1 data=0, en=1, dir=1, out=1000000000010101 rstn=1 data=1, en=1, dir=1, out=0100000000001010 rstn=1 data=0, en=1, dir=1, out=1010000000000101 rstn=1 data=1, en=1, dir=1, out=0101000000000010 rstn=1 data=0, en=1, dir=1, out=1010100000000001 rstn=1 data=1, en=1, dir=1, out=0101010000000000 rstn=1 data=1, en=1, dir=1, out=1010101000000000 rstn=1 data=1, en=1, dir=1, out=1101010100000000 rstn=1 data=1, en=1, dir=1, out=1110101010000000 rstn=1 data=1, en=1, dir=1, out=1111010101000000 rstn=1 data=1, en=1, dir=1, out=1111101010100000 rstn=1 data=1, en=1, dir=1, out=1111110101010000 Simulation complete via $finish(1) at time 430 NS + 0<无脚本>

Verilog