变量 - VHDL 示例

VHDL 中的变量的作用类似于 C 中的变量。它们的值在代码中修改变量的确切位置有效。因此,如果一个信号使用变量 before 的值 赋值,它将具有旧的变量值。如果信号使用变量之后的值 分配它将具有新的变量值。

变量规则:

- 变量只能在进程内部使用

- 在一个进程中创建的任何变量都不能在另一个进程中使用

- 变量需要在关键字process之后定义 但在关键字开始之前

- 使用 := 分配变量 赋值符号

- 立即赋值的变量采用赋值的值

要理解的最重要的事情是变量会立即获取其赋值的值。 下面的示例展示了使用变量的一种有用方法:存储数据以供临时使用 .它使用 case 语句和与 (&) 连接运算符。

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

在前面的示例中,我们连接了两个信号,以便可以在 case 语句中使用它们。变量 v_Choices 在分配后立即可用。让我们看另一个例子。下面的示例更全面,并演示了变量如何立即获取其赋值的值。信号 r_Var_Copy1 和 r_Var_Copy2 看起来是一样的,但 r_Var_Copy2 在复位之前永远无法达到 5。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

为了模拟我们的设计,我们需要创建一个测试平台。此外,在模拟中显示变量可能有点棘手。如果您使用的是 Modelsim,请阅读有关如何在 Modelsim 的波形窗口中查看变量的更多信息。

测试台:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

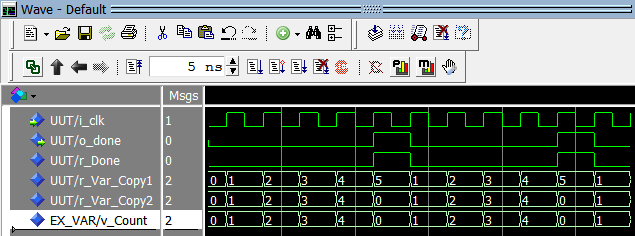

变量示例测试台波形

变量示例测试台波形 上面的例子演示了变量的行为与信号的不同。信号 r_Var_Copy1 和 r_Var_Copy2 看起来是一样的,但 r_Var_Copy2 在复位之前永远无法达到 5。

VHDL