通过氩等离子体处理插入 ZnO 降低金属和 n-Ge 之间的接触电阻

摘要

我们研究了 n-Ge 上的金属-绝缘体-半导体接触,利用 ZnO 界面层 (IL) 克服金属/Ge 界面的费米能级钉扎 (FLP) 效应并降低电子的势垒高度。在 ZnO 和 n-Ge 之间的界面处获得了 0.22 eV 的小导带偏移,并且 ZnO IL 导致接触电阻显着降低 (R c) 由于消除了 FLP,与没有 ZnO 的控制装置相比,在金属/ZnO/n-Ge 中。观察到 ZnO 的氩 (Ar) 等离子体处理可以进一步提高 R 在 Al/ZnO/n-Ge 器件中的 c 特性,这是由于 Ar 等离子体处理增加了氧空位的浓度 V o,充当 ZnO 中的 n 型掺杂剂。在掺杂浓度为 3 × 10 16 的 Al/ZnO/n-Ge 中证明了欧姆接触 厘米 −3 在葛。在重掺杂 n + -Ge 带有磷离子 (P + ) 注入,比接触电阻率为 2.86 × 10 − 5 Ω cm 2 在 Al/ZnO/n + 中实现 -Ge采用Ar等离子体处理。

背景

与 Si 相比,锗 (Ge) 的载流子迁移率更高,因此在先进的金属氧化物半导体场效应晶体管 (MOSFET) 中备受关注 [1, 2]。对于 Ge p 沟道 MOSFET,在应变 Ge 沟道 [3,4,5]、表面钝化 [6,7,8,9] 和源极/漏极 (S/D) 接触 [3,4,5] 的生长方面取得了很大进展。 10] 和超尺度 Ge pFinFET [11] 已经证明了 Si 器件的优越电气性能。相比之下,Ge n 沟道晶体管仍然面临挑战,这对 Ge CMOS 的集成产生了障碍,包括界面质量差,导致电子迁移率低,以及由于有限的激活而导致的高 S/D 电阻Ge 中 n 型掺杂剂的速率 [12] 和金属/n-Ge 界面处的费米能级钉扎 (FLP) [13]。对于 n-Ge 上的大多数金属,FLP 导致电子的肖特基势垒高度约为 0.5 eV,从而产生非常大的接触电阻 R c [13,14,15]。

费米能级脱钉可以通过在金属和 n-Ge [18] 之间插入薄界面层 (IL),例如 TiO2 [16] 和 ZnO [17] 来完成,因为薄的 IL 可以阻挡金属波函数转化为 Ge 以减少金属诱导的间隙态 [19, 20]。 ZnO 相对于 Ge 的导带偏移 (CBO) 较小,这会导致 R c 在金属/ZnO/n-Ge 中,与金属/TiO2/n-Ge 相比,TiO2/Ge 具有正 CBO [16]。 ZnO 的介电常数小于 TiO2 的介电常数,因此与 TiO2 相比,ZnO IL 可以在金属和 n-Ge 之间获得更薄的耗尽区。此外,通过引入非化学计量缺陷,如氧空位V,很容易在ZnO中实现n型掺杂 o [21, 22],这会在金属和 n-Ge 之间产生更小的 ZnO 耗尽区。到目前为止,在金属/ZnO/n-Ge接触中,V掺杂ZnO o 是通过在氮气氛中退火进行的 [16],然而,这可能导致退火过程中 ZnO 和 Ge 的相互扩散 [23],以及退火过程中掺杂原子在 n-Ge 中的扩散 [24, 25] ,导致器件电流性能下降。因此,需要开发一种低温沉积和掺杂ZnO工艺。

在这项工作中,我们通过插入 ALD 沉积的 ZnO IL 来研究金属和 n-Ge 之间界面处的费米能级脱钉。研究了氩(Ar)等离子体处理ZnO层对Al/ZnO/n-Ge接触电阻特性的改善作用。

方法

在轻掺杂和重掺杂 n-Ge (001) 晶片上均形成金属触点。轻掺杂Ge样品的掺杂浓度约为3 × 10 16 厘米 −3 .为了实现重掺杂的 n-Ge,磷离子 (P + ) 植入剂量为 1 × 10 15 cm −2 对 n-Ge(001) 施加 30 keV 的能量,然后在 600°C 下快速热退火 60 秒。在使用去离子水和稀释的 HCl 的几次循环清洗晶片后,立即将 Ge 晶片装入 ALD (Beneq TSF-200) 室中以沉积 ZnO,然后使用剥离工艺在 Ge 上溅射沉积铝 (Al) 触点.在这里,使用了 1、2 和 3 纳米的三种 ZnO 厚度,这通过光谱椭偏法 (SE) (J. A. Woollam M2000) 得到证实。在 ZnO 沉积过程中,分别使用二乙基锌 (DEZn) 和去离子水 (H2O) 作为 Zn 和 O 前驱体,并且基板温度保持在 150°C 以消除 GeOx 的形成 .使用 ALD 的详细 ZnO 沉积过程在我们以前的工作中报告过。 [26, 27]。为了进一步提高 ZnO 薄膜的导电性,Ge 样品上的一些 ZnO 用氩 (Ar) 等离子体处理。还制造了不含 ZnO IL 的对照 Al/n-Ge 样品。 R 使用圆形传输线方法 (CTLM) 提取 ZnO/Ge 上的铝 c,这是通过剥离形成的。暴露的ZnO通过等离子体蚀刻完全蚀刻,以确保相邻器件之间的完全隔离[16]。

Keithley 4200 SCS 用于测量 Al/ZnO/n-Ge 合同和 CTLM 结构的电气特性,使用高分辨率透射电子显微镜 (HRTEM) 和 X 射线光电子能谱 (XPS) 确定微观结构和界面样品的性质,紫外可见分光光度计(LAMBDA 950,PerkinElmer)用于确定带隙E g 沉积的氧化锌薄膜。

结果与讨论

Al/ZnO/n-Ge 的材料表征

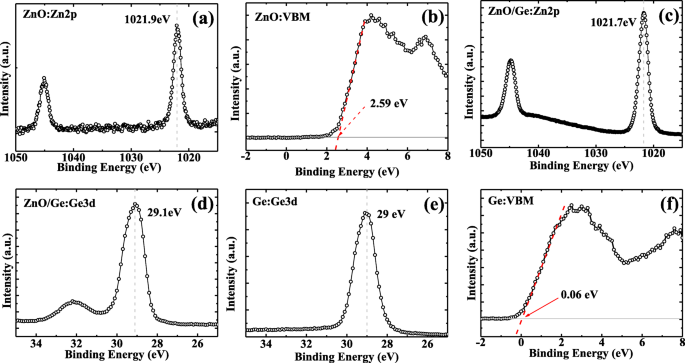

Ge/ZnO 的 XPS 价带光谱和 ZnO 的透射光谱如图 1 和图 2 所示。图1和图2分别用于研究Al/ZnO/n-Ge界面费米能级脱钉效应的机制。我们对厚 ZnO 样品、ZnO/n-Ge 界面样品和纯 Ge 样品进行了 XPS 测量,以获得 ZnO/Ge 的价带偏移 (VBO),如图 1 所示。Zn 2 厚 ZnO 样品的峰值位置和 VBM 分别为 1021.9 eV 和 2.59 eV。 Zn 2p 和 Ge 3d ZnO/Ge 界面样品的峰值位置分别为 1021.7 eV 和 29.1 eV。 Ge 3d 纯 Ge 样品的峰值位置和 VBM 分别为 29 eV 和 0.06 eV。这表明 ZnO/Ge 的 VBO 为 2.33 eV [30]。

<图片>

ZnO/Ge 样品价带的 XPS 光谱。 一 锌 2p 和 b 厚 ZnO 样品的价带光谱 c 氧化锌 2p 和 d Ge 3d ZnO/Ge 界面样品的光谱,以及 e Ge 3d 和 f 块状Ge样品的价带光谱

<图片>

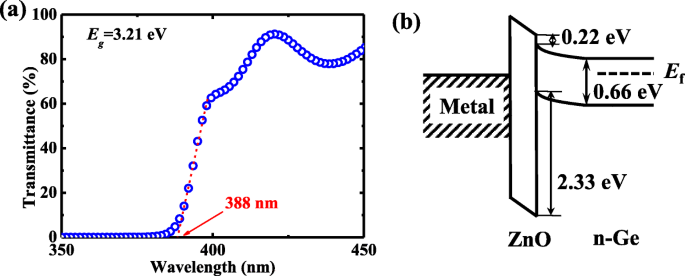

一 沉积的 ZnO 薄膜的透射光谱证明了 E g 为 3.21 eV。 b Al/ZnO/Ge接触的能带排列

图 2a 显示了从 UV-VIS 光谱获得的厚 ZnO 样品的透射率图,以及 E g 的 ZnO 被确定为 3.21 eV,与 [28, 29] 中报告的值一致。通过使用获得的 E g 的 ZnO 和 VBO,确定 ZnO 和 Ge 之间的 CBO 为 0.22 eV,如图 2b 所示。这表明使用 ZnO 插入层可以在 Al/n-Ge 界面实现费米能级脱钉,从而产生低 R c为Al/ZnO/n-Ge接触。

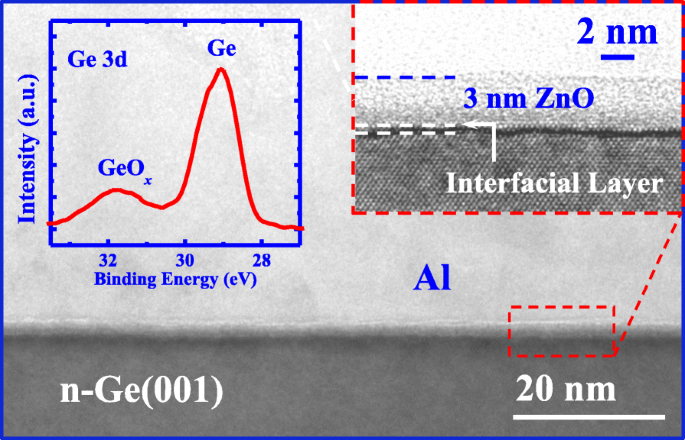

图 3 显示了 Al/ZnO/n-Ge 结构的 TEM 图像,其中 ZnO 的厚度为 3 nm。在 Al 和 n-Ge 之间观察到均匀且共形的 ZnO 层。右上角的插图说明了 Al/ZnO/n-Ge 界面的放大视图的 HRTEM 图像。测得ZnO薄膜的厚度为3 nm,与SE测量的结果一致,ZnO薄膜为非晶态。

<图片>

Al/ZnO/n-Ge 样品的 TEM 图像显示了 Al 和 Ge 之间的均匀 ZnO 层。右上角插图显示了 Al/ZnO/n-Ge 界面的 HRTEM 图像,左上角插图显示了 XPS Ge 3d 证明 GeOx 存在的样品结果 界面层

薄的 GeOx Ge 和 ZnO 之间形成界面层,由于这项工作中使用的沉积温度较低,因此与 [31] 相比,界面层要小得多。这是因为在 ZnO 沉积过程中,Ge 与 O 前驱体发生反应,导致形成 GeOx 伊利诺伊州。 GeOx XPS Ge 3d 也证明了这一点 导致左上角的插图。

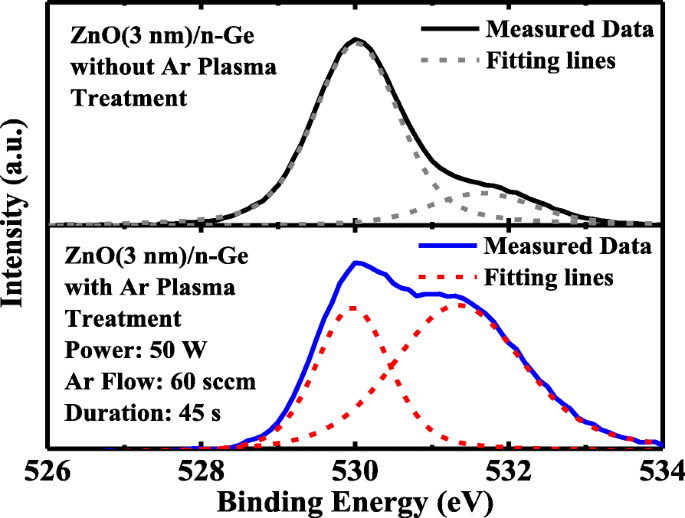

Ar等离子体处理可以提高ZnO薄膜的导电性,导致氧空位浓度增加V o,作为 ZnO 的供体 [32, 33]。图 4 描绘了 O 1s 的 XPS 结果 对于沉积态 ZnO 和经过 Ar 等离子体处理的样品,功率为 50 W,Ar 气流为 60 sccm,持续时间为 45 s。 O 1s 使用高斯拟合将峰解卷积为两个峰。 ~ 530 eV 处的峰值对应于 ZnO 中的晶格氧 [34, 35]。对于沉积态样品,531.7 eV 处的峰值对应于 V o (~ 531.5 eV) 和化学吸附在 ZnO 薄膜表面的氧,如羰基和羟基 [35, 37]。对于经过 Ar 等离子体处理的样品,峰值在 ~ 531.5 eV,其转移到较低的结合能,并且与沉积样品相比变得更加明显,表明更多的 V o 由于 Ar 等离子体处理而产生,并且化学吸附的氧被有效去除。 ZnO 中 n 型掺杂剂的增加导致更薄的隧道势垒和更低的界面串联电阻,是 R 降低的原因 c [36]。

<图片>

O 1s 的 XPS 结果 以及沉积态(上)和 Ar 等离子体处理(下)ZnO (3 nm)/n-Ge 样品的解卷积结果

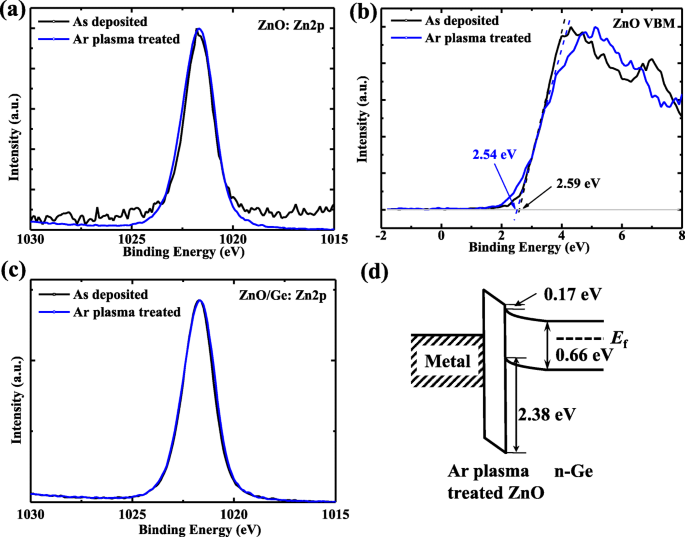

我们使用厚 ZnO 样品和 ZnO/Ge 界面样品进行了 XPS 测量,有和没有 Ar 等离子体处理,如图 5 所示。我们发现,在 Ar 等离子体处理后,有 - 0.05 eV 偏移。这可能表明 Ar 等离子体处理后 ZnO/Ge VBO 约为 2.38 eV,CBO 约为 0.17 eV。

<图片>

使用和未使用 Ar 等离子体处理的 ZnO/Ge 界面样品的 VBM。 一 锌 2p 和 b 厚 ZnO 样品的价带光谱 c 氧化锌 2p ZnO/Ge 界面样品的光谱。 d Ar等离子体处理金属/ZnO/n-Ge的能带对准图

Al/ZnO/n-Ge 触点的电性能

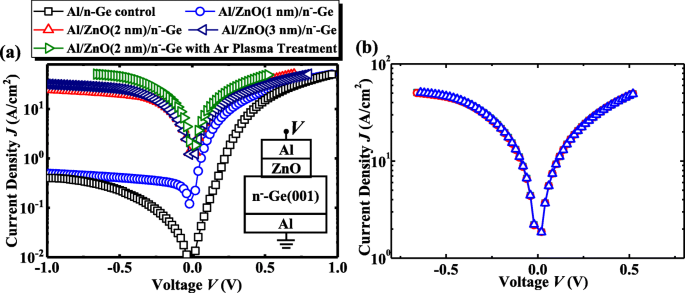

图 6a 显示了测得的电流密度 J 作为外加电压的函数 V 轻掺杂 n-Ge 上的 Al 触点的特性。 Al/ZnO/n − -Ge 器件具有不同厚度的 ZnO 层。装置示意图如图 6 插图所示。

<图片>

一 J -V Al/n − 的特性 -Ge控制,Al/ZnO/n - -Ge,ZnO 厚度为 1 nm、2 nm 和 3 nm,Al/2 nm Ar 等离子体处理的 ZnO/Ge,b J 三种 Al/2 nm Ar 等离子体处理的 ZnO/Ge 器件的 -V 特性

正如预测的那样,由于 Al/n − 处的费米能级钉扎,不含 ZnO 的 Al/n-Ge 控制器件显示出具有高势垒高度的整流特性 -葛 [38]。与不含 ZnO 的对照 Al/n-Ge 样品相比,Al/ZnO/n-Ge 器件表现出改进的反向 J ,这是由于金属/Ge 界面处金属诱导间隙态 (MIGS) 减少引起的费米能级脱钉 [18, 19]。使用更厚的 ZnO,这种改进会更加增强,这是因为消除了更多 MIGS。但是 3 nm ZnO 插入器件的正向电流密度小于 2 nm 器件的正向电流密度。这可以解释如下。 Al/ZnO/n-Ge 的主要电流密度是隧道电流。如果ZnO不够厚,MIGS就不会被有效消除,仍然表现出整流特性。但如果氧化锌太厚,氧化锌的串联电阻将主导整个电阻,电流变小。因此,在消除 MIGS 和增加 ZnO 的串联电阻之间存在权衡,因此 IL 存在临界厚度 [19]。总之,2 nm 被认为是 Al/ZnO/n-Ge 接触的最佳厚度。

Ar等离子体处理后,Al/ZnO/n − 的性能 -Ge器件进一步改进。无论施加电压的反向或正向扫描 V , Al/2 nm ZnO/n − -采用Ar等离子体处理的Ge器件实现了增强的J 与具有 2 nm ZnO 或 3 nm ZnO 的器件相比,这是由于大量的 V o 在 Ar 等离子体处理期间在 ZnO 膜中生成。 ZnO中较高的掺杂浓度可以有效降低ZnO的串联电阻,降低ZnO与Al界面处电子的隧穿势垒,提高隧穿电流密度。

图 6b 显示了 J -V 三个 Al/2 nm ZnO/n − 的特性 -Ge 器件采用 Ar 等离子体处理。很明显,J 不同器件的情况几乎相同,说明ALD工艺和Ar等离子体处理对电流密度的提高效果均一。

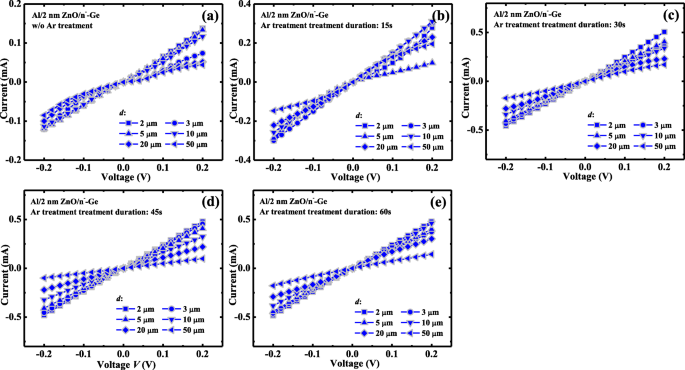

获得了 Al/2 nm ZnO/n − 的欧姆接触 -Ge 没有和有不同的 Ar 等离子体处理持续时间分别为 15 s、30 s、45 s 和 60 s,如图 7 所示。

<图片>

我 –V Al/2 nm ZnO/n − 处的曲线 -Ge 具有不同的 d 一 未经过 Ar 等离子体处理且具有 b 的 Ar 等离子体处理持续时间 15 秒,c 30 秒,d 45 秒和 e 60 秒

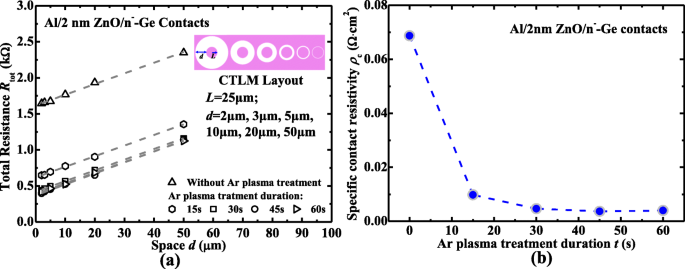

原始总电阻 R 两个接触之间的tot随着d的减小而减小 ,以及最后的 R tot 由修正系数 C 修改,其计算公式为 C =(L /d )·ln(1 + d /L ) [39],其中 L =25 μm 表示内垫的半径,如图 8a 中的插图所示。通过绘制 R 作为 d 的函数的 tot 在图 8a 中,薄层电阻 R n − 的 sh -Ge 可以从直线斜率得到,然后 ρ c 是根据线性拟合线与垂直轴的截距计算的。对于 Al/2 nm ZnO/n − -Ge 器件未经 Ar 等离子体处理,ρ c 是 6.87 × 10 −2 Ω cm 2 , 但经过 45 s 的 Ar 等离子体处理后,与未经过 Ar 等离子体处理的相比降低了 17.2 倍,并且具有接触电阻率 ρ c 为 3.66 × 10 −3 Ω cm 2 .我们比较ρ的值 c 对于 Al/2 nm ZnO/n − -Ge 器件在图 8b 中具有不同的 Ar 等离子体处理持续时间。观察到 ρ 设备的 c 随处理时间延长至 30 秒而降低。然而,由于处理时间大于 30 秒,ρ c 几乎保持不变。 ρ 的减少 c 可能归因于 ZnO 的掺杂,从而降低了隧道势垒和串联电阻,如前所述。但是 n − 的薄层电阻没有可观察到的变化 -Ge,说明对n − 的电导率没有影响 -Ge采用Ar等离子体处理。

<图片>

一 R tot 与 d 具有 Al/2 nm ZnO /n − 的 CTLM 曲线 -Ge 接触不同的 Ar 等离子体处理持续时间,图 5a 中的插图是本工作中使用的 CTLM 结构的信息。 b ρ c与不同Ar等离子体处理时间的比较

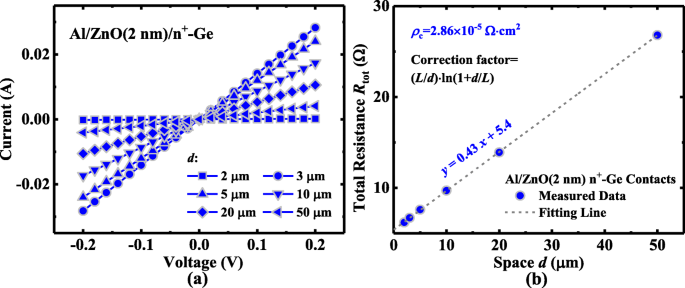

使用在重掺杂 Ge 上具有 Al 触点的 CTLM 结构来研究 Al/2 nm ZnO/n + 的接触电阻特性 - 葛。 ZnO 层经历了 45 秒的 Ar 等离子体处理。图 9a 显示了测量的 I -V 具有不同 d 的 Al 触点之间的曲线 ,显示出优异的欧姆性能。图 9b 绘制了 R 作为 d 的函数的 tot 对于 Al/2 nm ZnO/n + -Ge CTLM 和 R sh 和 ρ c 被提取为 64Ω/□ 和 2.86 × 10 −5 Ω cm 2 , 分别。

<图片>

一 我 –V 曲线在 Al/ZnO(2 nm)/n + -Ge 具有不同的 d 使用 Ar 等离子体处理的 ZnO。 b R tot 与 d 具有 Al/ZnO(2 nm)/n + 的 CTLM 曲线 -Ge接触

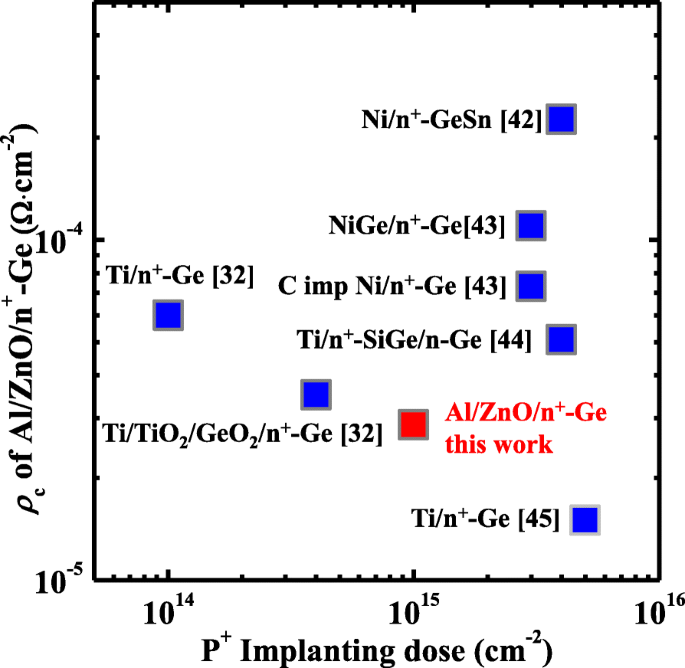

我们比较ρ Ar等离子体处理的ZnO的c Al/ZnO/n + -Ge 器件在这项工作中与文献中报道的那些,如图 10 所示。对于重掺杂的 n + -Ge接触样品,Al/ZnO/n + -Ge 触点显示较小的 ρ c 与 Ni/GeSn [40, 41]、Ni/Ge [42]、Ti/n + 的比较 -参考文献中的Ge。 [31], Ti/TiO2/GeO2/Ge [31], 碳注入 Ni/Ge [42], Ti/n + -SiGe/n-Ge [43]。 Ni/Ge、Ni/GeSn、Ti/Ge 和碳注入 Ni/Ge 等金属欧姆接触受到严重的费米能级钉扎,导致较大的 ρ C。对于 Ti/TiO2/GeO2/Ge 接触,1 nm TiO2/1.5 nm GeO2 IL 的双层引入了大的隧道电阻,降低了接触电阻率特性。但是ρ 在这项工作中的 c 比参考中的大。 [44]。我们假设这可能是由于 P + 的四倍大 植入剂量比我们工作中的要高。较大的注入剂量将使 n + 的表面掺杂更重 -Ge,导致更薄的肖特基势垒和更小的ρ C。我们相信随着 n + 的掺杂更重 -Al/ZnO/n中的Ge + -Ge 器件,更小 ρ c 会导致。

<图片>

ρ的比较 c Al/ZnO/n + -Ge 与其他报告的联系人的工作中,使用 P + 植入剂量作为 x 轴

结论

研究了由 ZnO IL 在 Al/ZnO/n-Ge 结构中引起的费米能级脱钉效应。 XPS 测量显示 ZnO/n-Ge 处的小 CBO 为 0.22 eV,即消除了 FLP,从而导致 n-Ge 上的欧姆金属接触。据进一步报道,Ar等离子体处理ZnO导致V浓度增加 o, 作为 ZnO 中的 n 型掺杂剂,提高了 R c 在 Al/ZnO/n-Ge 器件中的性能。在 n − 上获得欧姆金属触点 和 n + -Ge 与 Ar 等离子体处理的 ZnO IL。基于 CTLM 结构,ρ 的值 c 3.66 × 10 −3 Ω cm 2 和 2.86 × 10 − 5 Ω cm 2 在 Al/2 nm ZnO/n − 中实现 -Ge 和 Al/2 nm ZnO/n + -Ge,分别用 Ar 等离子体处理 ZnO,功率为 50 W,持续 45 秒。

缩写

- Al:

-

铝

- ALD:

-

原子层沉积

- Ar:

-

氩气

- CBO:

-

导带偏移

- CTLM:

-

环形传输线法

- DEZn:

-

二乙基锌

- E 克:

-

带隙

- FLP:

-

费米能级钉扎

- 哥:

-

锗

- GeOx :

-

氧化锗

- GeSn:

-

锗锡

- HCl:

-

盐酸

- HRTEM:

-

高分辨透射电子显微镜

- IL:

-

界面层

- MIGS:

-

金属诱导间隙态

- MOSFET:

-

金属氧化物半导体场效应晶体管

- Ni:

-

镍

- P + :

-

磷离子

- R :

-

接触电阻

- R 总:

-

原始总电阻

- SE:

-

光谱椭偏仪

- Si:

-

硅

- Ti:

-

钛

- 二氧化钛:

-

二氧化钛

- 紫外可见光:

-

紫外可见

- VBO:

-

价带偏移

- V :

-

氧空位

- XPS:

-

X射线光电子能谱

- 氧化锌:

-

氧化锌

- ρ :

-

比接触电阻率

纳米材料