数字斜坡 ADC

也称为楼梯坡道 ,或者干脆计数器 A/D 转换器,这也很容易理解,但不幸的是有几个限制。

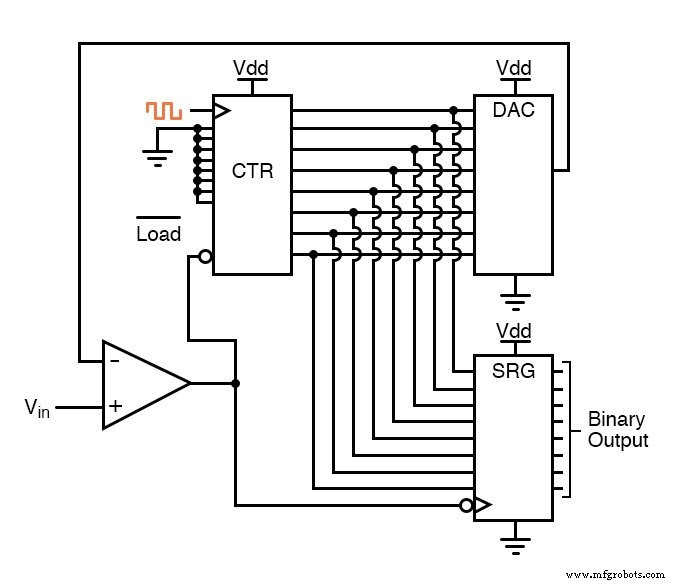

基本思想是将自由运行的二进制计数器的输出连接到 DAC 的输入,然后将 DAC 的模拟输出与要数字化的模拟输入信号进行比较,并使用比较器的输出告诉计数器何时停止计数和复位。下图展示了基本思想:

当计数器随着每个时钟脉冲递增计数时,DAC 输出略高(更正)的电压。比较器将该电压与输入电压进行比较。

如果输入电压大于 DAC 输出,则比较器的输出将为高电平,计数器将继续正常计数。但最终,DAC 输出将超过输入电压,导致比较器的输出变低。

这将导致两件事发生:首先,比较器输出的高到低转换将导致移位寄存器“加载”计数器输出的任何二进制计数,从而更新 ADC 电路的输出;其次,计数器将在低电平有效的 LOAD 输入端收到一个低电平信号,使其在下一个时钟脉冲复位为 00000000。

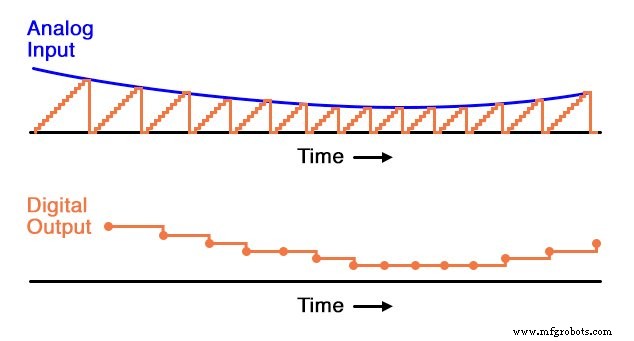

该电路的作用是产生一个 DAC 输出,该输出上升到模拟输入信号所处的任何电平,输出对应于该电平的二进制数,然后重新开始。随着时间的推移,它看起来像这样:

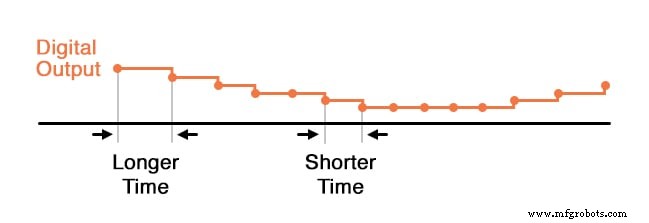

请注意更新(新数字输出值)之间的时间如何根据输入电压的高低而变化。对于低信号电平,更新间隔相当近。对于更高的信号电平,它们在时间上间隔得更远:

对于许多 ADC 应用,更新频率(采样时间)的这种变化是不可接受的。这一点,以及电路需要在每个计数周期开始时从 0 开始一直计数的事实导致模拟信号的采样相对较慢,这使得数字斜坡 ADC 与其他计数器策略相比处于劣势。

工业技术