使用恰到好处的 RISC-V 自定义指令加速应用程序的指南

RISC-V 的开放指令集架构 (ISA) 允许在实现方面具有广泛的灵活性,并提供可选功能,可以采用新的方法来解决硬件-软件设计权衡。基于模块化结构,可以使用许多标准扩展和选项来配置基础处理器作为起点。然而,真正的价值实际上在于 RISC-V 为开发人员提供了创建新扩展、指令和配置的机会,以独特地满足其创新应用理念的需求。

固定 ISA 的软件挑战

传统上,ISA 一直是商业组织的知识产权 (IP),这些组织要么想要销售微处理器或微控制器,要么想要将其设计授权给他人使用。嵌入式开发人员只能执行基准测试软件,以确定哪种解决方案最适合他们的应用需求。由于开发具有所有必要生态系统的独立 ISA 的成本,半导体供应商越来越依赖主流 IP 提供商提供的标准固定 ISA,依靠摩尔定律和集成外设来提供差异化,例如超低功耗, 给他们的客户。

这里的挑战是用于执行代码的指令无法更改。因此,无法实现可能通过例如加密算法的优化指令获得的效率。这可能意味着开发人员的应用程序太慢,可能会使用过多的功率,或者经常错过控制循环中的硬实时截止日期。即使有世界上最好的意愿,这些因素也难以仅通过半导体制造改进或工艺缩减来解决。

RISC-V ISA 最初是加州大学伯克利分校的一个项目,现在由 RISC-V 国际协会维护,该协会是一个拥有 300 多名成员的非营利组织。这些有助于制定 ISA 规范、软件工具(例如模拟器和编译器)以及支持此类任务所需的生态系统的其他部分。使用是否有意义取决于是否可以利用两个因素之一:在许可方面是免费的,或者它提供的自由。

它开放且免费提供,提供了一个基本的处理平台,可供学术界用于教学和研究以及商业应用。开放的 ISA 还为寻求半导体 IP 来源的开发人员提供多种商业模式支持,从商业 IP 供应商到开源项目和自建设计。商业组织也发现这很有吸引力,将其用于 FPGA、SoC,甚至微控制器或标准产品的核心。

由于它提供的自由,学术界可以研究解决计算挑战的新方法,实现从新指令和其他加速器、多核和众核异构设计以及不同微架构选项的任何内容。其中许多选项对希望解决复杂挑战的初创公司和企业也很有吸引力,例如在边缘运行的低功耗人工智能 (AI) 芯片组,通过添加根据最终应用要求调整的自定义指令。

由于生态系统已经建立并内置了 RISC-V 灵活性,因此任何标准配置或自定义扩展都应该能够利用 ISA 兼容框架内的工具和软件。

了解开放 RISC-V ISA 的灵活性

由于 RISC-V ISA 和相关工具的可访问性,启动调查项目以评估其在特定应用程序中的适用性很容易。模拟工具允许对标准基础 ISA 进行试验以确定开箱即用的性能。例如,一个好的起点是具有整数“I”和乘法“M”扩展的 32 位 RISC-V 配置(可称为 RV32IM),提供对基本 32 位整数指令集的支持;还有更多选项可用,但这对于本示例来说已经足够了。然后将其与模拟内存一起实例化,包括访问延迟和等待状态。

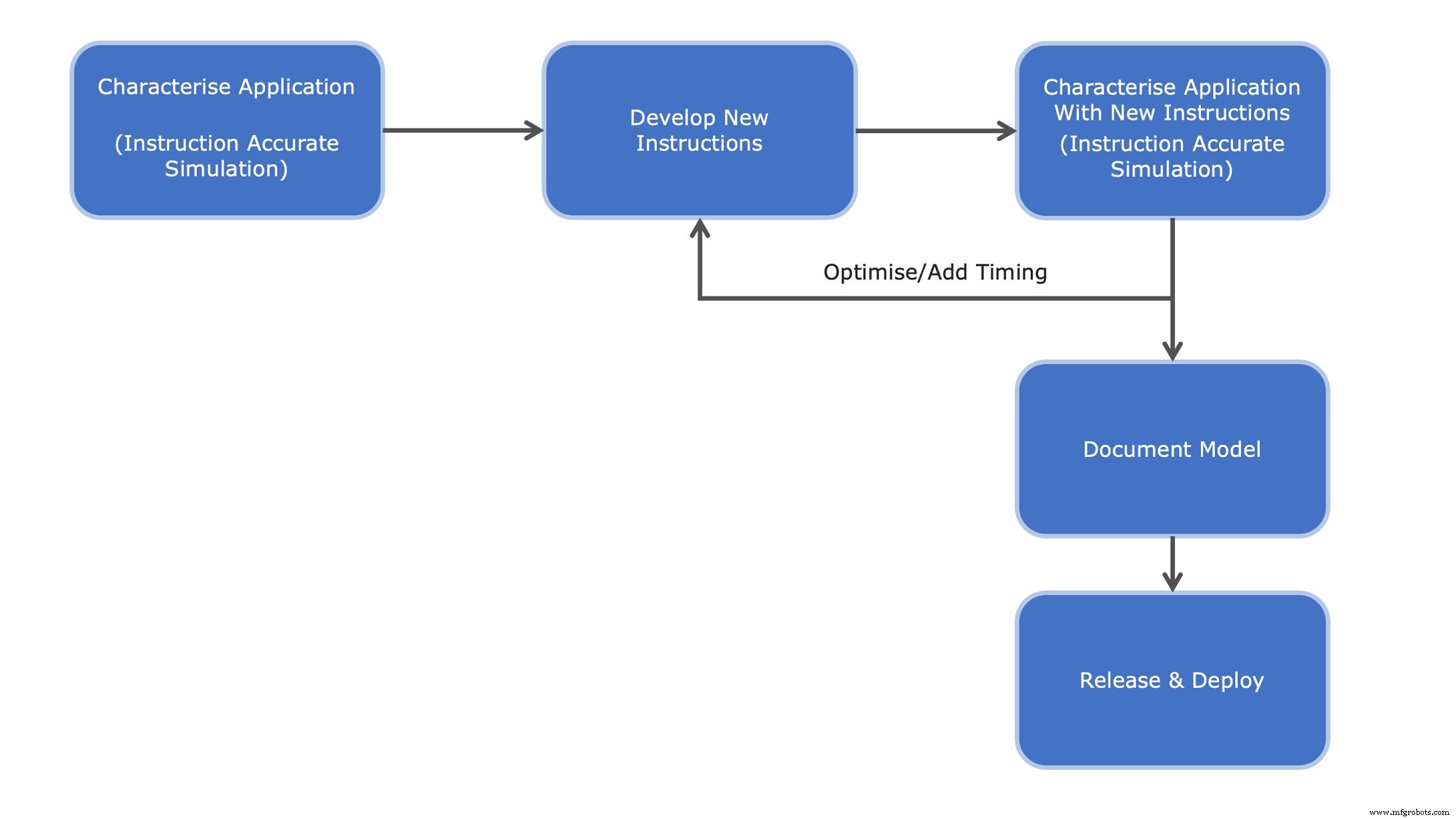

然后可以使用标准工具链交叉编译用 C/C++ 编写的应用程序。这可以在裸机上运行,也可以作为(实时)操作系统 (RTOS/OS) 的一部分运行。然后使用指令集模拟器 (ISS) 等工具执行生成的二进制代码,该工具允许集成和模拟所选的基本处理器模型(图 1)。此环境还提供标准输入/输出功能和对主机文件系统的访问。然后可以使用标准的集成开发环境 (IDE) 工具(例如 Eclipse)来控制代码执行,并通过 GNU 调试器 GDB 进行连接。

从这里开始,通过剖析和分析过程,识别、设计和建模指令候选。通过使用原始应用程序代码作为基本功能模型,可以对由此产生的改进进行快速测试、验证和性能比较。这种剖析和分析的快速迭代允许快速选择和优化值得实施的指令。文档可以从模型中生成,并构成寄存器传输逻辑 (RTL) 设计和优化模型的功能规范的基础。

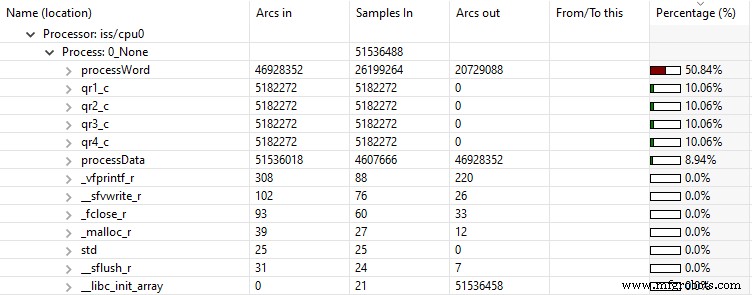

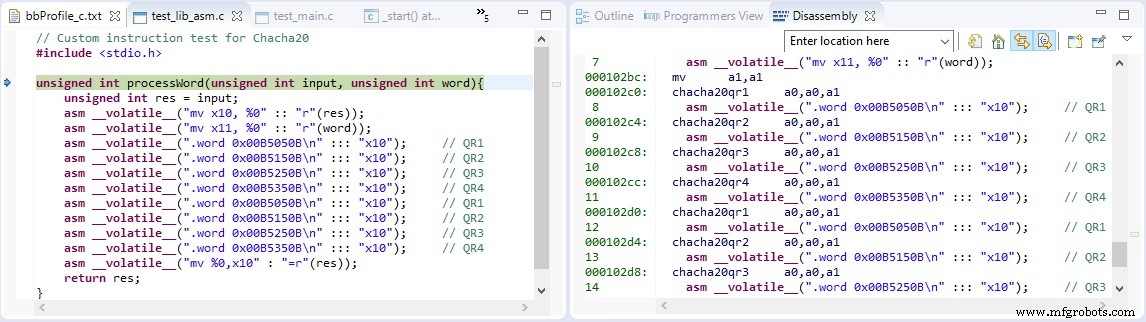

例如,ChaCha20 等加密算法可能对特定应用程序至关重要。可用的源代码可以针对“普通”RV32IM 基础进行编译、执行,然后使用基本块分析以估计的指令周期时序进行分析,以确定在哪些代码段中花费了多少时间。 ChaCha20 算法的核心大量使用异或和旋转指令,称为四分之一轮(图 2)。块分析的结果立即突出显示,大部分执行时间都花在这些函数上。

这些热点的图形可视化也可以通过使用验证、分析和剖析 (VAP) 工具生成。执行时间不是提供文本输出,而是作为可折叠统计数据树提供,有助于更好地可视化具有高比例执行指令的热点。这可以在图 3 中看到,其中函数 processWord() 实现ChaCha20算法,依次调用四个qrx_c 功能以实现所需的四分之一轮功能。

通过查看编译器生成的汇编代码和/或通过运行基本块分析,然后可以确定已使用哪些指令和指令组合来实现算法。从这里开始,下一步是确定哪些自定义指令在 ISA 规范的范围内可能会提高执行速度。

确定 RISC-V 可以提供的潜在改进

ChaCha20 算法大量使用 XOR 加上 7、8、12 和 16 位的左旋转。使用 RV32IM 基本规范的可用指令表明,这需要 XOR 指令后跟左移指令。这意味着有可能将这两个步骤优化为四个专用指令,这些指令与 7、8、12 或 16 位的左旋转一起实现 XOR。

作为加载存储架构,任何自定义指令都必须假设要操作的数据已经驻留在此 RISC-V 的 32 位寄存器之一中。这立即确定将需要可以位于 custom-1 中的 R 类型(寄存器)指令 解码空间(图4)。

ISA 为此类指令提供了清晰的结构。通过遵循这些规则,我们可以快速确定如何对我们的新指令进行编码。低 7 位定义为操作码, 它被分配了一个值,将其标记为 custom-1 中的自定义指令 解码空间。这与OP相反 或 OP-IMM 分别用于现有 XOR 和左移指令的操作码。

ISA 为此类指令提供了清晰的结构。通过遵循这些规则,我们可以快速确定如何对我们的新指令进行编码。低 7 位定义为操作码, 它被分配了一个值,将其标记为 custom-1 中的自定义指令 解码空间。这与OP相反 或 OP-IMM 分别用于现有 XOR 和左移指令的操作码。

ISA 定义中保留了三个预定义的位块,用于为结果指定两个源寄存器和目标寄存器。这留下了一个称为 funct3 的位块 .这三位为我们提供了编码八种可能指令的空间,本例中将使用其中四种。

这些指令不需要 RTL 的详细硬件实现,可以在 ISS 环境中模拟它们,看看它们是否对所面临的挑战有任何好处。这四个新指令使用开放虚拟平台 (OVP) VMI 应用程序编程接口 (API) 建模。这使开发人员能够根据目标应用程序的新指令快速迭代指令的设计,以提供最佳的所需结果。只有实现了这一点,才需要将资源投入到 RTL 实现中。

为了对指令进行初始功能评估,有两种可能的方法。第一种是调用算法的原始 C/C++ 版本,将新指令绑定到该函数(图 5a)。第二个是将它们实现为 VMI 变形指令,以创建相同的行为(图 5b)。这样做的好处是效率更高,是推荐的方法。

当然,仅仅存在新指令并不意味着编译器可以立即使用它们。因此,需要使用内联汇编器重新编写原始 C/C++ 应用程序并交叉编译以使用新指令。由于候选指令的剖析和分析可能是一项迭代任务,基于内在的方法提供了最有效的方法来调整原始 C 应用程序以使用新的自定义指令。

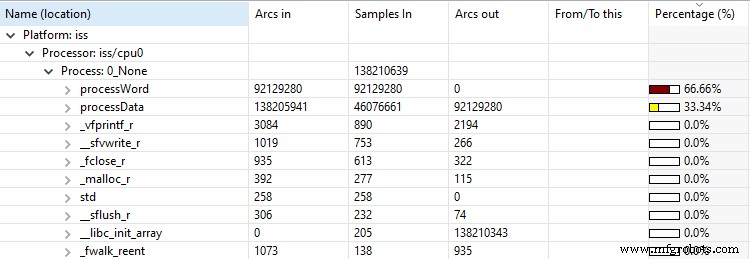

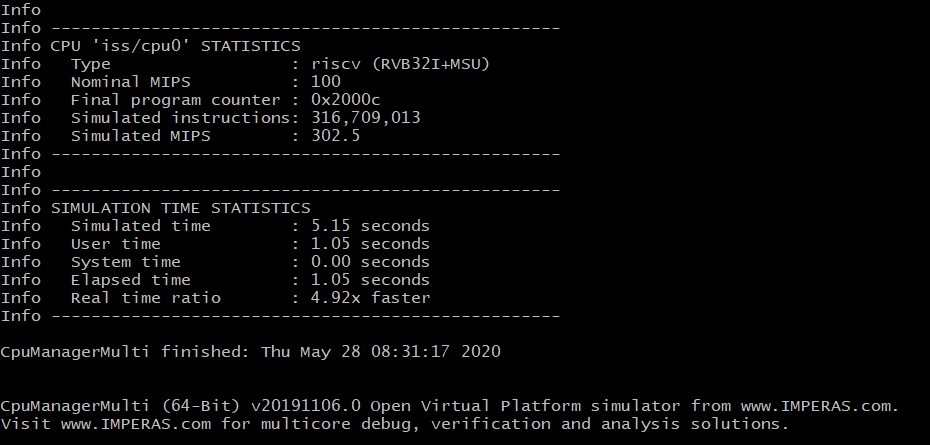

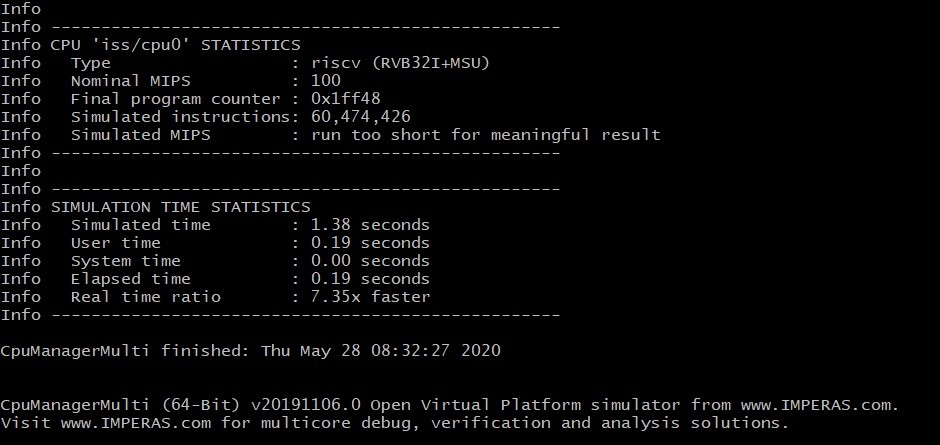

加载到模拟器中的 RISC-V 基础实现也需要了解新指令,以便从中受益。这是通过在重新运行模拟之前将它们包含在模型中来实现的。在此特定示例中,重复分析表明执行算法所花费的总时间更少(图 6)。 Imperas VAP 分析工具显示 processWord() 函数,使用专用的内联指令,现在占整个算法执行的 66%,但算法的整体执行时间大大减少(图 6b)。

原始 C 实现的结果

信息模拟指令:316,709,013

信息模拟时间 :5.15 秒

带有自定义说明的结果

信息模拟指令:60,474,426

信息模拟时间 :1.38 秒

一旦确定了正确的功能,模型就会通过声明处理器周期中每条指令的执行时间来进一步完善。然后可以使用更多轮模拟来确定任何性能改进,甚至考虑与最终硬件实现中可能发生的内存访问相关的等待状态。

由于与常见的开源 IDE 和 GDB 工具紧密集成,因此在将设计提交给硬件实现之前,可以结合优化的 RISC-V 设计对解决方案进行全面调试(图 7)。

从模拟转向实施

确定潜在的性能改进后,下一步需要在 RTL 中实现四个新指令。由于进行了初步工作,这成为定义需求的功能规范,也可以用作 RTL 验证测试计划的一部分,作为黄金参考模型。虽然在 C 应用程序中使用内在函数有助于对自定义指令进行剖析和分析,但这种方法也可用于未来的生产代码开发,或者可以考虑用于潜在的编译器工具链增强。

另一个剩下的基本任务,文档,也是一个简单的过程。所有开放式虚拟平台 (OVP) 快速处理器模型都包含可扩展以涵盖更改和修改功能的文档。按照给定的模板,可以声明和描述新指令,从而允许开发人员社区发现它们的能力并加以利用。然后将文档转换为可以生成 PDF 的 TeX 文件(图 8)。

总结

凭借 RISC-V 开放 ISA 的自由,除了规范中定义的标准选项和功能外,用户还可以开发进一步的自定义扩展和指令。简而言之,它支持新的和创造性的商业模式,包括商业和开源实施,此外,它还支持更广泛的自由来探索超越主流传统方法的增值功能。

然而,真正的价值来自于采用成熟的、有文档记录的和受支持的基本核心,并对其进行修改以满足特定的应用程序需求。通过仔细的应用程序分析、代码分析和模拟,可以获得通过固定 ISA 无法实现的显着性能改进。在开始详细的硬件实现之前,所有这些都可以通过实际应用工作负载进行开发和配置。

嵌入式