PCB 串扰:它是什么以及如何应对它

面对现实吧。 PCB 串扰是普通工程师在使用高速 PCB 时面临的一个大问题。

如今,我们拥有更紧凑的电路板,因此在组装 PCB 之前分析串扰变得更加重要。但是,如果您不熟悉串扰的概念,则可能难以应对。

本文将向您展示什么是串扰以及如何防止它。我们还将更多地介绍不同类型的串扰。

你准备好了吗?开始吧!

什么是 PCB 中的串扰?

PCB 串扰是走线之间不需要的能量耦合。它会导致一条迹线的信号脉冲覆盖另一条迹线,即使它们没有物理接触。这通常发生在您没有正确间隔平行迹线时。

PCB走线

尽管您可能会争辩说您的设计保持最小间距要求,但这可能不足以防止电磁耦合。

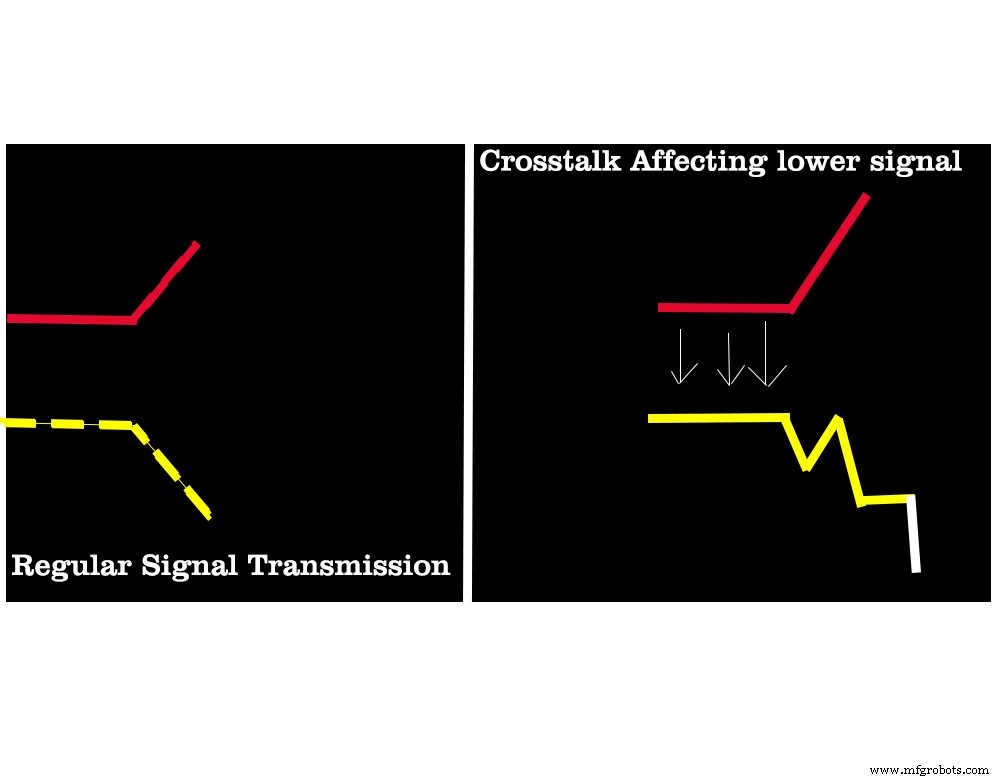

因此,考虑一下 PCB 上的两条平行走线;如果一条迹线具有较高的幅度,它可能会影响具有较低幅度的迹线。结果,较弱的迹线信号开始复制,较强的信号而不是传输它。这就是串扰发生的时候。

事实上,互感会导致电流从强迹线转移到弱迹线。然后,由互电容产生的电容器使电流相似,这会影响电路的信号完整性。

许多设计人员认为串扰是由同一层上的平行线引起的。但是,它也可能出现在不同层的相邻行中。

此外,控制或防止串扰可能很棘手,主要是在它未被检测到的情况下。如果您在设计的初始阶段不处理它,它会降低您 PCB 的功能。

PCB 上的串扰是如何发生的?

手检PCB

电路中通常有两种方式会发生串扰:公共阻抗耦合或电磁耦合。公共阻抗耦合易于分析,仅在各种信号共用一个返回路径时才会发生。

另一方面,电磁场耦合比较复杂,有电感和电容两个细分。

电容耦合

平行走线是由电介质隔开的高速 PCB 的电容器平行板。而强弱迹线之间的电场就是我们给电容贴上的标签。

现在,如果电容器电压发生变化,它将改变电场并产生位移电流。该位移电流会导致电容耦合电流,从而导致串扰。我们称这种效应为寄生电容。

感应耦合

电感耦合取决于围绕弱迹线旋转的磁场环的数量。越强的走线磁场包围越脆弱的线路并改变其传输电流。

发生这种情况时,根据法拉第感应定律,较强的线会感应出电压。感应电压以串扰的形式传输电流。

宽边耦合

当平行走线靠近相邻层时,会发生宽边耦合。此外,当少量的核心厚度将这些相邻的信号层分开时,更有可能发生这种情况。通常,它是 0.1 毫米(4 密耳),这对于在同一层或相邻层上间隔两条迹线来说是不够的。

串扰的类型

串扰影响信号传输

我们可以将各种串扰类型分为传播方向、测量区域和量化。让我们仔细看看。

基于传播方向

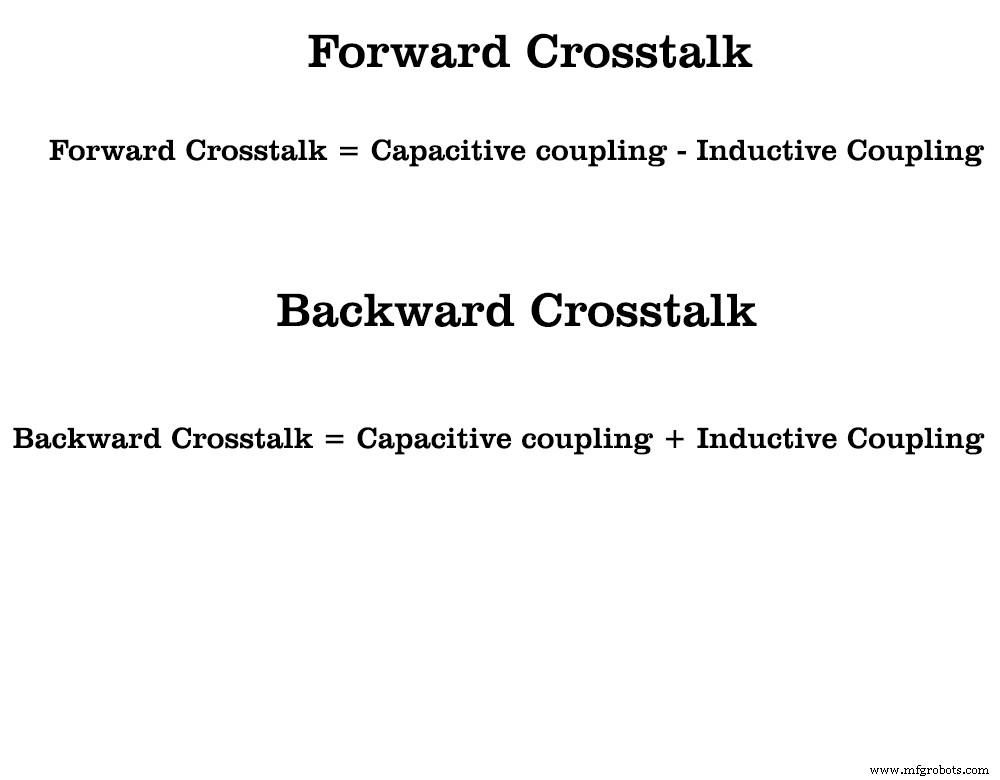

在这种分类下,我们有两种串扰类型,包括前向串扰和后向串扰。

对于前向串扰,更脆弱的走线将复制的电流沿更强的信号方向传输。相反,反向串扰是指复制信号以相反的方向传输。

以下是基于传播方向的串扰公式:

基于测量区域

此分类下还有两种串扰类型。它们包括:

- 远端串扰 (FEXT):指较弱迹线接收端的干扰。

- 近端串扰 (NEXT):指较弱走线驱动器侧的噪声。

此外,这些串扰类型可能发生在迹线上的任何地方。所以不管是单端导体还是双导体都没有关系。

基于量化

在这里,我们有三种串扰类型,包括:

- 一、Power-sum-FEXT (PS-FEXT):指的是远端串扰的绝对影响。

- 二、Power-sum-NEXT (PS-NEXT):指近端串扰的相对影响。

- 三、Power-sum-equal-level-crosstalk (PS-ELFEXT):指PS-NEXT和PS-FEXT相加。

外星人串扰

这种串扰比其他变体更复杂。它很难消除,屏蔽也无法提供足够的保护。当不同的信号破坏微弱的信号时,就会发生这种情况。

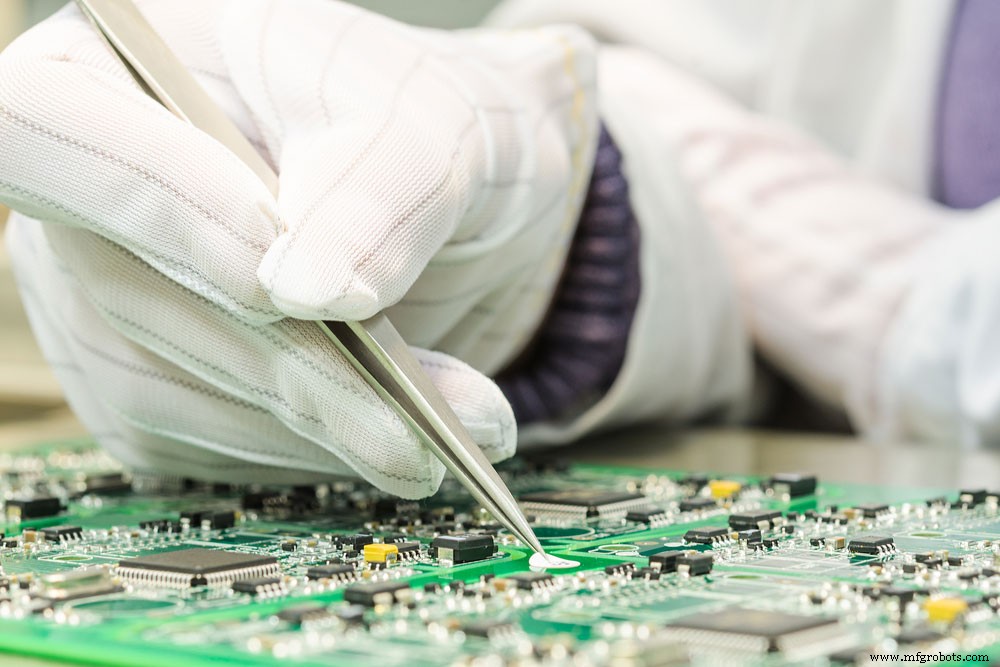

什么导致串扰?

测量串扰

以下是一些可能导致PCB串扰的因素:

- 交叉可能是传播速度差异的结果。但是,您可以通过传播延迟和走线长度匹配来缓解它。

- 提高的数据速率也会导致串扰。具有高数据速率的电路板也将具有高上升时间。法拉第定律指出,较高的上升时间会增加串扰。

- 截断的 PCB 过孔是另一个可能产生串扰的因素。它们会产生反射和振铃,从而导致串扰。

- 电路板尺寸:更大的电路板需要更长的走线。但较长的走线会导致串扰——因为它们就像天线一样。

如何减少 PCB 中的串扰

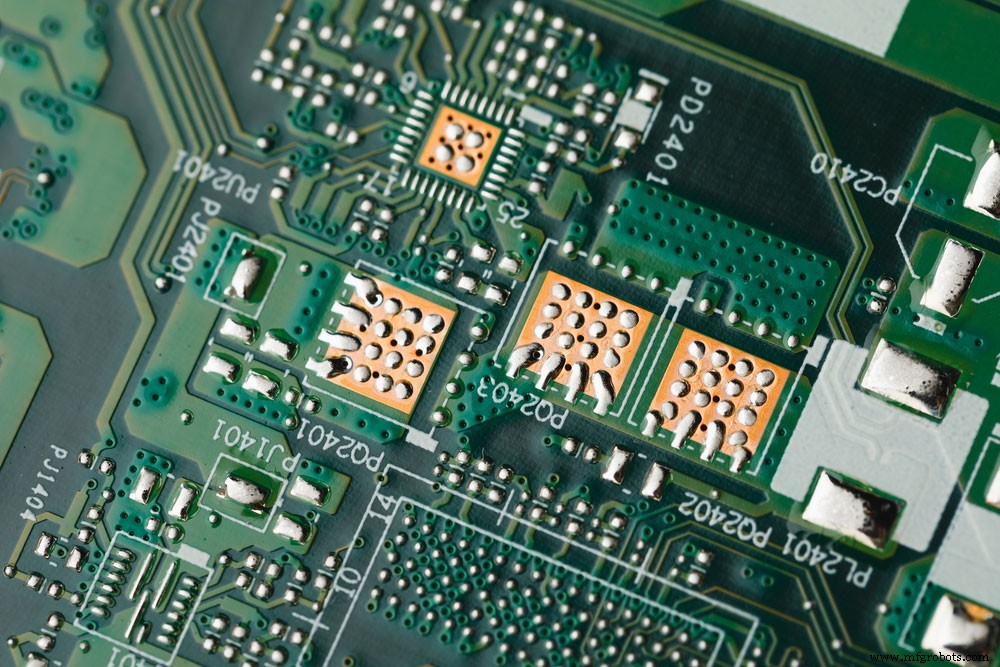

高速PCB

您不能总是避免高速 PCB 中的串扰。但是您可以将其降低到微不足道的水平。以下是您可以用于此任务的一些方法。

1.仅使用实体参考平面。

固体参考平面可以吸收溢出的磁场和电场。因此,它不会传播和破坏其他信号。

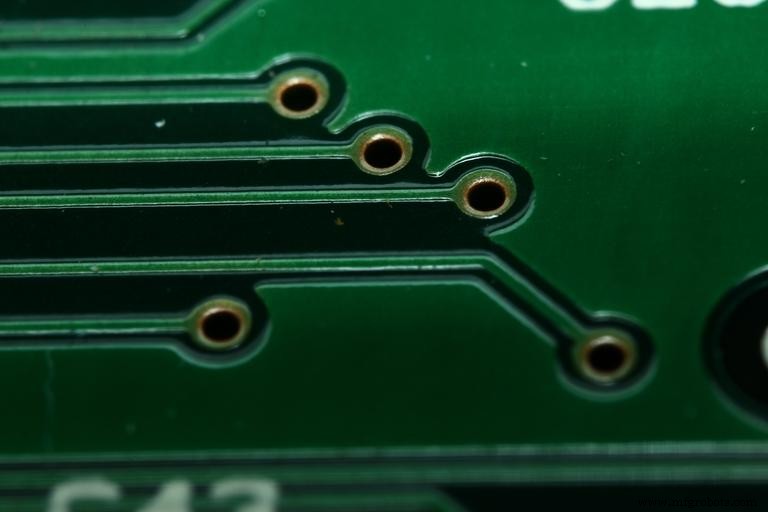

2。使用背钻过孔

带过孔的PCB

避免使用 via subs,因为它们会削弱信号完整性并导致串扰。相反,选择背钻过孔。

3.检查和限制串扰

测量电路板的串扰并确保其不超过 150mV。此外,避免调整信号上升时间。它可能会增加串扰并可能使其超出限制。

4.选择差分对路由

使用紧密耦合的差分路由有助于减少串扰。如何?由于不存在等耦合,差分对不会接受共模噪声,从而减轻串扰。

5.分离高频信号

在 PCB 上工作的人

避免将高频信号放置在其他信号附近。将它们分开将有助于减少串扰的机会。

6.正确消除奇偶传播方式

您可以使用三电阻网络或T-termination来有效地取消偶数和奇数传输模式。

7.利用短迹线

带走线的PCB

换句话说,你的走线越长,串扰的机会就越大。然而,保持走线短有助于减少耦合和减少串扰。

8.分离异步信号

始终使异步信号远离高频信号。尝试将它们放置在靠近电源线的位置,以减少串扰的可能性。

9.减少并行跟踪运行

更长的走线(超过 500mils)会增加互感并引起串扰。

10.利用保护跟踪

您可以使用保护走线来减轻传输线之间的串扰。但是,这些痕迹很棘手,使路由变得复杂。

11.使用正交路由

如果您正在使用相邻的信号层,请尝试正交路由它们。这将有助于减少层间的电容耦合。

12.保持痕迹分开

间隔良好的痕迹

使用 3W 规则正确分隔所有迹线。如果不遵守此规则,则会增加互电容,从而导致串扰。但使用 3W 定律将有助于将串扰减少 70%。

注意:使用 10w 规则可以减少 98% 的串扰。

结束语

电路板

串扰是高速PCB不可避免的问题之一。不幸的是,它不可能从您的电路板中消除,但您可以将其降低到保证信号完整性和电路性能安全的水平。

串扰是平行或相邻走线之间无意耦合的结果。但是你可以通过正确地间隔你的行来最小化耦合的机会。

请记住,有多种方法可以减少串扰,因此请务必使用适合您的电路设计的一种。

如果您有任何问题,请随时与我们联系。

工业技术