Verilog 块语句

有一些方法可以将一组语句组合在一起,这些语句在语法上等同于单个语句,称为 块语句 .块语句有两种:顺序和并行。

顺序

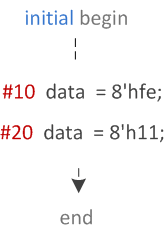

使用 begin 包装语句 和 end 关键字,并将按给定的顺序依次执行,一个接一个。延迟值是相对于前一条语句的执行时间来处理的。在执行完块内的所有语句后,控制可能会传递到其他地方。

module design0;

bit [31:0] data;

// "initial" block starts at time 0

initial begin

// After 10 time units, data becomes 0xfe

#10 data = 8'hfe;

$display ("[Time=%0t] data=0x%0h", $time, data);

// After 20 time units, data becomes 0x11

#20 data = 8'h11;

$display ("[Time=%0t] data=0x%0h", $time, data);

end

endmodule

在上面的例子中,begin-end 中的第一条语句 由于相对性质,块将在 10 个时间单位执行,第二条语句在 30 个时间单位执行。上一条语句执行后20个时间单位。

ncsim> run [Time=10] data=0xfe [Time=30] data=0x11 ncsim: *W,RNQUIE: Simulation is complete.

平行

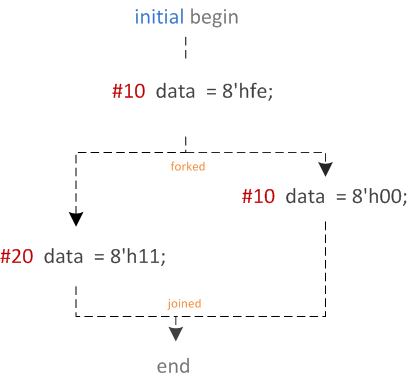

一个并行 块可以同时执行语句,延迟控制可以用来提供分配的时间顺序。语句通过将它们包装在 fork 中来并行启动 和 join 关键字。

initial begin

#10 data = 8'hfe;

fork

#20 data = 8'h11;

#10 data = 8'h00;

join

end

<无脚本>

在上面的例子中,fork-join 块将在 10 个时间单位执行语句后启动。该块中的语句将并行执行,并且将启动的第一个语句将是数据被分配值 8'h00 的语句,因为延迟是在启动 fork-join 后 10 个时间单位。再过 10 个时间单位后,将启动第一个语句,数据将得到值 8'h11。

initial begin

#10 data = 8'hfe;

fork

#10 data = 8'h11;

begin

#20 data = 8'h00;

#30 data = 8'haa;

end

join

end

<无脚本>

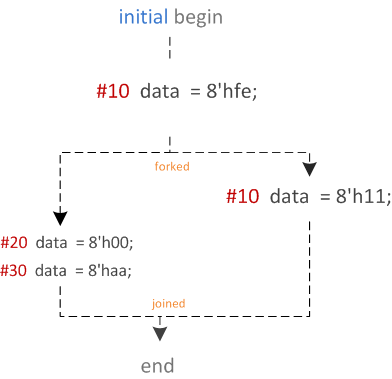

有一个begin-end 上例中的块,begin-end 块中的所有语句将按顺序执行,但块本身将与其他语句一起并行启动。因此,数据将在 20 个时间单位获得 8'h11,在 30 个时间单位获得 8'h00,在 60 个时间单位获得 8'haa。

区块命名

顺序块和并行块都可以通过添加 : name_of_block 来命名 在关键字 begin 之后 和 fork .通过这样做,可以在 disable 中引用该块 声明。

begin : name_seq

[statements]

end

fork : name_fork

[statements]

join

Verilog