教程 - VHDL 简介

VHDL 是一个可怕的首字母缩略词。它代表 V 恒生H 硬件D 说明 L 语言。首字母缩略词中的首字母缩略词,太棒了! VHSIC 代表 V 埃里 H 哎 S 撒尿我 综合C 电路。因此,VHDL扩展为V ery 高速集成电路 H 硬件D 说明 L 语言。 PHEW 那是一口。 VHDL 是教育和商业用于设计 FPGA 和 ASIC 的两种语言之一。如果您不熟悉这些引人入胜的电路,您可能首先会从对 FPGA 和 ASIC 的介绍中受益。 VHDL 和 Verilog 是数字设计师用来描述其电路的两种语言,它们在设计上不同于 C 和 Java 等传统软件语言。

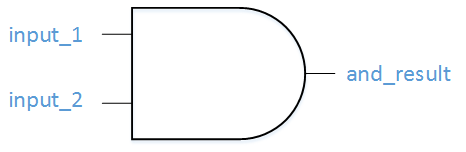

对于下面的示例,我们将创建一个 描述 的 VHDL 文件 和门。作为复习,一个简单的 And Gate 有两个输入和一个输出。只有当两个输入都等于1时,输出才等于1。下面是我们将用VHDL描述的与门的图片。

安与门

安与门 让我们开始吧! VHDL的基本单元称为信号 .现在让我们假设一个信号可以是 0 或 1(实际上还有其他可能性,但我们会谈到)。下面是一些基本的 VHDL 逻辑:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

第一行代码定义了一个 std_logic 类型的信号,它被称为 and_gate。 Std_logic 是最常用于定义信号的类型,但您将了解其他类型。此代码将生成具有单个输出(and_gate)和 2 个输入(input_1 和 input_2)的 AND 门。关键字“and”在 VHDL 中是保留的。 <=运算符称为赋值运算符。当你口头解析上面的代码时,你可以大声说:“信号和门GETS input_1 and-ed with input_2。”

现在您可能会问自己 input_1 和 input_2 来自哪里。正如他们的名字所暗示的,他们是这个文件的输入,所以你需要告诉工具他们。文件的输入和输出在 entity 中定义 .实体包含一个端口,该端口定义文件的所有输入和输出。让我们创建一个简单的实体:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

这是你的基本实体。它定义了一个名为 example_and 的实体和 3 个信号、2 个输入和 1 个输出,所有这些都是 std_logic 类型。需要另一个 VHDL 关键字来完成此操作,即 architecture .架构用于描述特定实体的功能。将其视为论文:实体是目录,架构是内容。让我们为这个实体创建一个架构:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

上面的代码定义了一个名为 rtl 的实体 example_and 的架构。架构使用的所有信号都必须在“is”和“begin”关键字之间定义。实际的架构逻辑位于“开始”和“结束”关键字之间。你几乎完成了这个文件。您需要告诉工具的最后一件事是使用哪个库。库定义了某些关键字在文件中的行为方式。现在,理所当然地认为你需要在文件的顶部有这两行:

library ieee; use ieee.std_logic_1164.all;

恭喜!您已经创建了第一个 VHDL 文件。你可以在这里看到完成的文件:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

似乎您必须编写大量代码才能创建一个愚蠢的门?首先,盖茨并不愚蠢。其次,你是对的; VHDL 是一种非常冗长的语言。习惯这样一个事实,即在软件中做一些非常容易的事情会花费你在 HDL 中显着更长的时间,例如 Verilog 或 VHDL。但只要请一些软件人员尝试在 VGA 显示器上生成一个图像,以显示康威的生命游戏,然后看着他们惊奇地头晕目眩!顺便说一句,该视频是使用 VHDL 和 FPGA 创建的。你很快就能做到这一点!

VHDL