什么是 VHDL?

总之,VHDL是一种用于设计数字电路的计算机语言。

我使用术语“计算机语言”来区分 VHDL 与其他更常见的编程语言,如 Java 或 C++。但是 VHDL 是一种编程语言吗?是的。它是一种编程语言,在创建计算机程序时毫无用处!

VHDL 是一种事件驱动的并行编程语言。虽然它不适合创建可由计算机上的 CPU 运行的程序,但它非常适合创建实际的 CPU。它是一种硬件描述语言,这意味着它可以用于设计数字逻辑。

在此处访问基本 VHDL 教程系列!

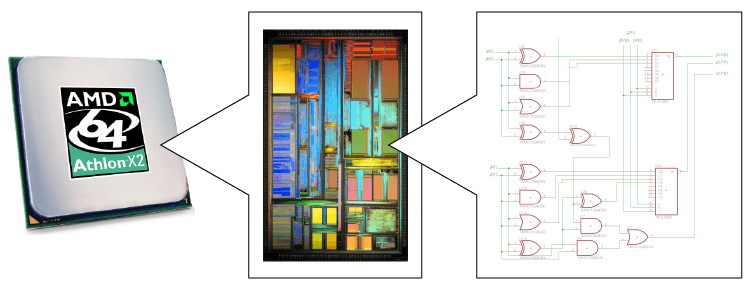

考虑上面的插图。 CPU芯片内部有很多很多主要是数字电子电路(中间)。这些数字电路可以使用示意图(右)来显示。在创建集成电路芯片时,例如 CPU,我们必须从创建右侧的逻辑电路图开始。

可以合理地假设此类电路图是在某种原理图编辑器中创建的,但这不是它的完成方式。电路采用 VHDL 等文本语言进行描述。

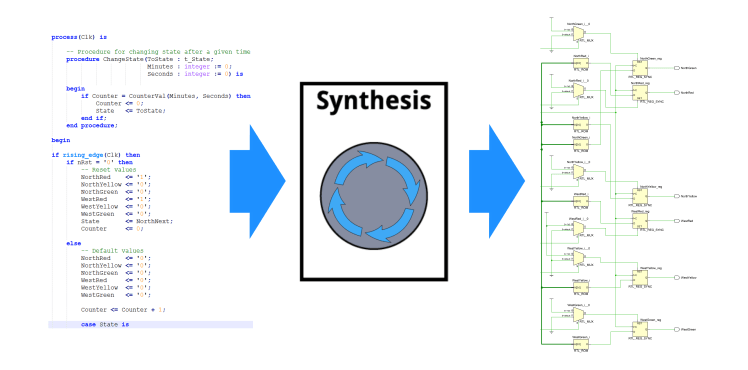

合成

我们不是在原理图编辑器中绘制确切的电路,而是使用 VHDL 来描述电路的期望行为。然后可以在称为综合的过程中将 VHDL 代码转换为精确的原理图 .综合工具是一个软件应用程序,它采用 VHDL 代码并尝试为您描述的行为找到可能的解决方案。

如果成功,合成器的输出将是一个网表,可以在原理图编辑器中查看。

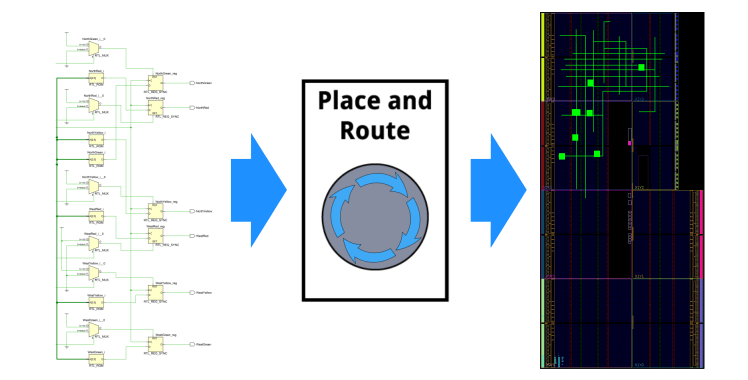

地点和路线

虽然网表给出了电路的准确逻辑描述,但它并没有说明物理实现。为了得到物理布局的精确描述,网表通过一个称为布局和布线的过程运行 , 或简称 PAR。路由器将尝试将网表中的元素分配给目标设备上的物理组件。它还需要在所有组件之间布线。这是一个路由器必须解决的巨大难题!

如果成功,PAR 的输出将是另一种网表。此网表包含布局和布线信息,并且特定于目标器件类型。如果目标器件是 FPGA,则路由网表可以转换为编程文件。如果目标设备是 ASIC,事情会复杂一些。

那么,什么是 VHDL?

它是一种用于为集成电路创建数字逻辑的编程语言。

在这里学习基本的 VHDL 教程>>

VHDL