如何在 VHDL 中创建时钟进程

绝大多数 VHDL 设计使用时钟逻辑 ,也称为同步逻辑 或顺序逻辑 .时钟进程仅由主时钟信号触发,而不是在任何其他输入信号发生变化时触发。

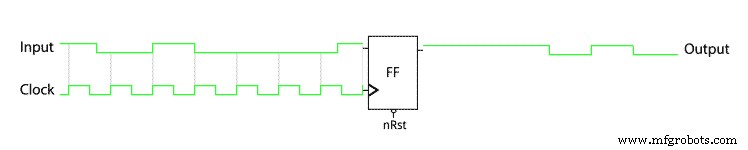

时钟逻辑的基本构建块是一个称为触发器的组件 .它有不同的变体,在本教程中,我们将重点介绍带负复位的正沿触发触发器:

触发器是一个采样保持电路,这意味着它会在时钟信号的上升沿到达时将值从输入复制到输出。然后输出保持稳定在采样值,直到时钟的下一个上升沿,或直到产生复位信号。

这篇博文是基本 VHDL 教程系列的一部分。

所有时钟进程同时触发,并将立即读取它们的输入。同时,他们将输出上一次迭代的结果。时钟信号有效地在数据流中创建时间步长。这使得设计人员可以管理创建复杂、深入的逻辑。他或她可以将算法的动作分解为在时钟周期发生的事件。

触发器或触发器数组有时称为寄存器 ,是一样的。

时钟进程的敏感度列表通常只包含时钟信号。这是因为时钟进程仅由时钟信号的侧翼触发,其他输入信号根本不会使其唤醒。

这是使用同步重置创建时钟进程的模板:process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

运动

在本视频教程中,我们将学习如何在 VHDL 中创建时钟进程:

触发器 testbench 的最终代码 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

触发器模块的最终代码 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

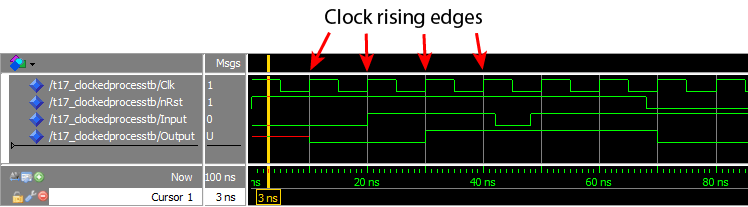

我们按下运行后 ModelSim 中的波形窗口,并在时间轴上放大:

分析

从波形中我们可以看出,输出信号只在时钟信号的每个上升沿更新。仅当时钟信号从“0”变为“1”时才对输入信号进行采样。从大约 45 ns 开始的输入信号的负倾角完全消失。它没有被复制到输出,因为它在时钟的两个上升沿之间,因此它被忽略了。

此动画说明了输出如何对不断变化的输入和时钟信号做出反应:

垂直线表示输入信号与时钟上升沿的关系。

特别注意从 20 ns 开始的输入信号上的一个正脉冲。它与时钟同步,并且正好是一个时钟周期长。输出不是瞬间反应,而是延迟了一个时钟周期。

当我学习 VHDL 时,我发现这特别难以理解。时钟的上升沿与输入的上升沿同步,那么触发器如何选择一个值或另一个值呢?

模拟器使用时间步长以可预测的方式对事件进行建模,并且信号在零时间内传播。因为触发器在更新输出的同时读取输入,所以它会看到输入的旧值并将其复制到输出。

在此处阅读有关 VHDL 时间步长的更多信息:Delta 周期解释

我应该在这个答案中补充一点,这不是真的 这个怎么运作。在物理世界中,信号需要时间来传播,我们不知道它何时到达触发器。这些传播延迟是由将 VHDL 代码转换为网表的软件过程(布局和布线)自动为我们估算的。

实际上,输入必须在时钟上升沿前后保持稳定几纳秒:

这些关键时间段称为建立和保持时间。幸运的是,这不是您通常必须考虑的事情。当纯粹使用时钟逻辑时,这些问题由将 VHDL 代码转换为网表的软件来处理。

外卖

- 具有同步重置的时钟进程仅在敏感度列表中具有时钟信号

if rising_edge(Clk)确保进程只在时钟的上升沿唤醒- 在同步设计中,事情只发生在有效的时钟边沿

参加基本 VHDL 测验 - 第 3 部分 »

或

转到下一个教程 »

VHDL