eFPGA 定制块增强数据加速系统

长期以来,我一直对 Achronix 的技术感兴趣。大约在 2004/2005 年,他们的异步 FPGA 架构首次引起了我的兴趣。最终,这设法达到了与时钟频率为 2 GHz 的同步 FPGA 相当的速度(如果有这样的野兽的话),但它仅适用于数量有限的算法和数据流应用。

2013 年,Achronix 推出了名为 Speedster 的高性能、高密度独立 FPGA 系列,专注于目标应用。 2016 年,Achronix 产品组合得到了 Speedcore 的扩充,Speedcore 是一款高性能嵌入式 FPGA (eFPGA)。

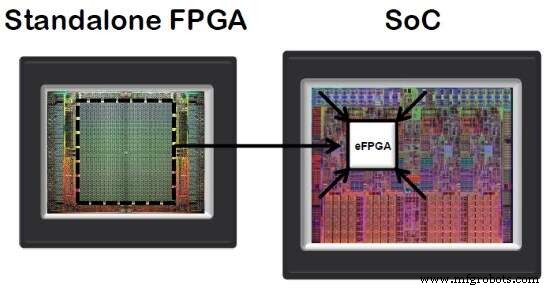

FPGA 非常适合加速数据密集型人工智能 (AI)/机器学习 (ML)、5G 无线、汽车 ADAS、数据中心和网络应用。一种解决方案是将独立 FPGA(如 Speedster)与独立处理器或片上系统 (SoC) 结合使用。然而,通过将核心 FPGA 架构(eFPGA)嵌入到 SoC 本身中,可以实现更高的性能和更低的功耗。

(来源:Achronix)

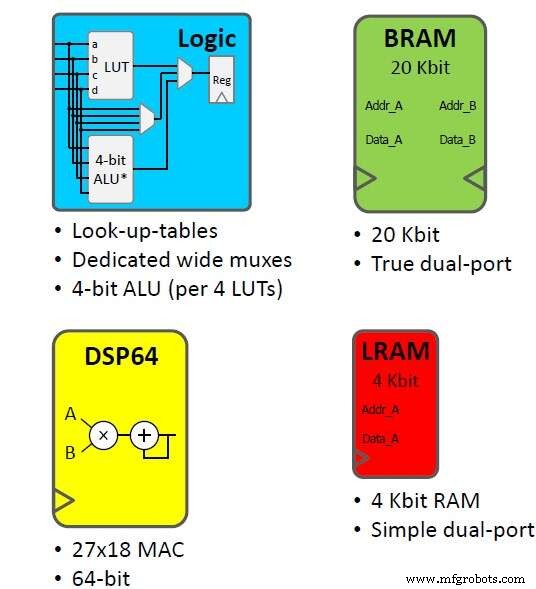

就 Speedcore 而言,SoC 开发人员可以访问用于逻辑、DSP、BRAM 和 LRAM 的预定义块库。

Speedcore 块(来源:Achronix)

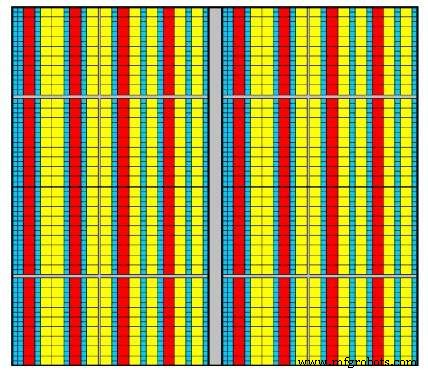

这些块以列的形式呈现。此外,开发人员可以指定所需的“高度”(列中的块数)、“宽度”(列数)和“混合”(列类型)。例如,一些项目可能受益于更多的逻辑和更少的 DSP,而其他项目可能需要更多的 DSP 和内存。

开发人员可以指定 Speedcore 结构的“混合”(来源:Achronix)

现在,那些生活在软件方面的人习惯于分析他们的代码以识别任何瓶颈功能,然后他们对其进行微调以实现尽可能高的性能。好吧,Achronix 现在为我们这些在围栏硬件方面闲逛的人提供了相同的功能。

对于那些需要最高性能的开发人员,Achronix 现在提供了创建 Speedcore 自定义块的功能。这些自定义块由 Achronix 通过对加速工作负载的详细架构分析与其客户协作定义。作为性能和/或面积瓶颈的重复功能提供了强化为 Speedcore 自定义块的理想候选。

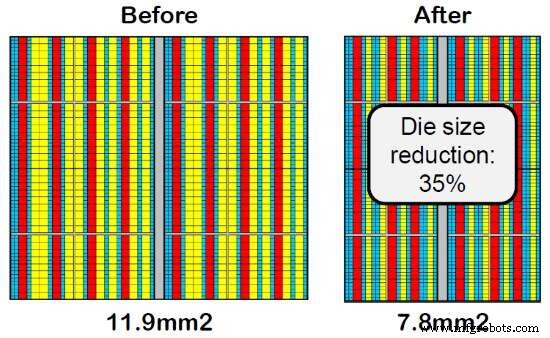

作为一个例子,考虑在先进的实时对象检测和识别系统中使用的 YOLO(“你只看一次”)对象识别功能。在这种情况下,创建和部署 Speedcore 自定义模块来优化矩阵乘法的 DSP 和内存模块,显着减小了芯片尺寸。

减小 AI 卷积网络的芯片尺寸(来源:Achronix)

Achronix ACE 设计工具以与存储器和 DSP 模块相同的方式完全支持 Speedcore 自定义模块,从设计捕获到比特流生成和系统调试。 Achronix 为管理所有配置规则的每个 Speedcore 自定义块创建了一个独特的 GUI。 ACE 包含 Speedcore 自定义模块所有配置的完整时序详细信息,使其能够完成基于时序的布局布线设计。最后但同样重要的是,开发人员还可以使用 ACE 强大的 SnapShot 嵌入式逻辑分析器在 Speedcore 设备中创建复杂的触发器并显示运行时信号。

有关 Speedster、Speedcore 和 Speedcore 自定义块的更多信息,请访问 Achronix 网站。

嵌入式