关于信号完整性的高速 PCB 设计挑战及其解决方案

随着电子技术的不断进步,数字系统的时钟频率越来越高,上升沿时间越来越短,PCB系统已经成为一种高性能的系统结构,而不仅仅是一个平台支撑元件。从电气性能上看,高速信号之间的互连不再是快速和透明的,引线之间的互连对高速PCB和板平面性能的影响也不容忽视。成功处理高速信号互连引起的反射、串扰、延迟、调用和阻抗匹配等信号完整性问题,确保信号传输质量决定设计成败。

PCB信号完整性基本理论

• 高速电路及其判定原理

高速电路的定义术语主要有两个版本。一方面,在一个电路中,当传输线上的数字信号延迟超过上升沿时间的20%时,该电路可视为高速电路。另一方面,在一个电路中,当数模电路的频率达到或超过45MHz到50MHz时,该电路被认为是高速电路。

基本上,如果L(引线长度)大于Tr,则该电路被认为是高速电路;如果 L 小于 Tr,则认为该电路为低速电路。这里的Tr是指脉冲上升沿时间。

• 信号传输速度和脉冲上升沿时间

信号在空中的传输速率为 3 x 10

8

小姐; PCB的材料FR4的介电常数显示为εr,即4。PCB中的信号传输速率可以使用公式计算  。

。

Vp 等于 15cm/ns,约为 6inch/ns。脉冲上升沿时间Tr=1/(10 x fclk),100MHz信号的上升沿时间为1ns。当PCB走线的信号延迟超过上升沿时间的20%时,信号上就会发生明显的调用。对于上升时间为1ns(100MHz)的方波,当PCB走线长度大于0.2ns x 6=1.2inch时,信号会发生严重调用。因此,临界长度为 1.2 英寸(约 3 厘米)。

• 特性阻抗

特性阻抗是阻抗匹配中的一个重要参数,它影响反射、调用、上冲和下冲,直接关系到高速信号传输的完整性,在高速设计中非常重要。

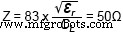

信号沿传输线传输,其电压与电流之比称为瞬态阻抗。输电线路上的瞬态阻抗由公式计算  。在这个公式中,Cl是指每单位长度的容量,单位为pF/inch(通常为3.3pF/inch)。当沿传输线的瞬态阻抗为恒定值时,该值被视为传输线的特性阻抗。对于PCB上的微带线和带状线,它们的特性阻抗可以通过传输线设计工具Polar Si9000计算出来,如图1所示。

。在这个公式中,Cl是指每单位长度的容量,单位为pF/inch(通常为3.3pF/inch)。当沿传输线的瞬态阻抗为恒定值时,该值被视为传输线的特性阻抗。对于PCB上的微带线和带状线,它们的特性阻抗可以通过传输线设计工具Polar Si9000计算出来,如图1所示。

影响信号完整性的要素及解决方案

• 阻抗匹配

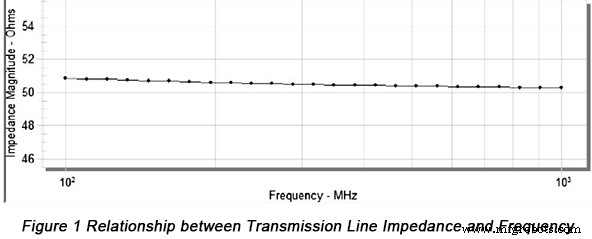

在高速电路设计中需要阻抗匹配,以确保快速和正确的数据传输。数据积累系统一般由传感器、信号调理仪、AD数据积累芯片、FPGA和SDRAM组成,如图2所示。

AD9649用作AD芯片,1.8V供电,14位数据线并行采样。采样频率设置为20M。采用PCI9054作为PCI接口芯片,支持DMA数据传输。 93LC66B被选为PCI配置芯片。 HY57V561620FTP-H用作数据存储,由4个BANK组成,每个BANK的存储空间为4M x 16bit,13行地址线和9列地址线。 FPGA选用EP1C6F256C8,终端电压3.3V,内核电压1.5V。 PCI总线宽度为32位,读写时钟采用33MHz时钟,最大连线和读取速度达到132MByte/s,能够支持累积数据的高速传输。

在设计PCB的过程中应考虑以下因素:

一个。 AD作为数字和模拟的混合部分,是PCB设计的重点之一。由于数字部分的高频,模拟部分对干扰非常敏感。如果不实施适当的处理,数字信号将倾向于干扰模拟信号,从而出现 EMI 问题。设计人员遵循的正确原则应该是:首先,在信号混合的PCB上,应将数字地和模拟地分开;第二,模拟和数字电子元件分为模拟地分布在模拟区,数字地分布在数字区;第三,模拟地和数字地在区域分割周围用磁珠连接。这些措施能够实现数字地和模拟地的分离。

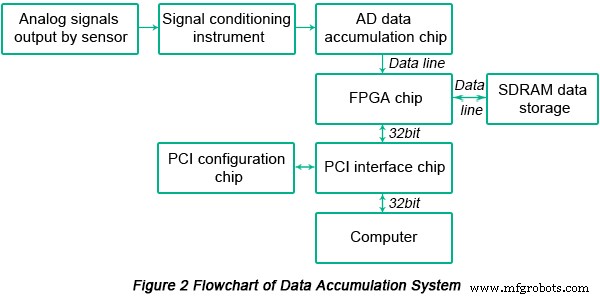

湾。 SDRAM应用于数据存储系统,手册明确指出与FPGA连接的数据线必须配置50Ω阻抗匹配,以保证高速传输,如图3所示。

FPGA将累积的数据写入SDRAM后,为了保持数据,必须不断进行刷新,每行刷新周期要快于64毫秒。

Polar Si9000软件阻抗匹配步骤如下:

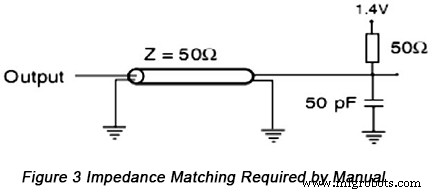

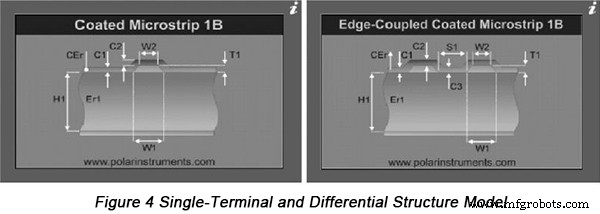

一个。高速信号线应穿过 PCB 的顶面,并应尽可能避开孔洞。软件中提取微带线结构模型,如图4所示。

50Ω阻抗匹配一般在单端走线时进行,90Ω阻抗匹配一般在差分走线时进行(如USB2.0 D+、D-)。

湾。软件界面填入PCB制作工艺所需的阻抗匹配值和具体值,参数包括介质厚度、PCB材料介电常数、铜箔厚度、绿油厚度和绿油介电常数。

| 项目 | 说明 | 参考和计算值 |

| H1 | 介电厚度(PP或板料) | 3.5-8.5mil |

| Er1 | 板材介电常数 | 4-4.6 |

| W1 | 信号走线宽度 | 基于阻抗值 |

| C1 | 基板材料绿色iol的厚度 | 0.8mil |

| C2 | 铜上绿油的厚度 | 0.5mil |

| CEr | 绿油介电常数 | 3.3 |

| Zo | 要匹配的阻抗值 | 单端:50Ω 差分:90Ω |

制作工艺的具体参数可以通过与PCB制造商的沟通了解,从而确定引线的宽度。对于差分微带线,还要算出引线间距(S1)。

C。如果计算出的引线宽度较大,PCB布线无法完成,则需要与PCB制造商进行更多的沟通,以调整制造工艺中的参数以满足设计要求。

• 串扰

串扰是指当信号在传输线上传输时,由于电磁耦合而对相邻传输线造成的意外电压噪声干扰。过多的串扰可能导致电路误触发,使系统无法正常工作。串扰是由电磁耦合产生的,耦合分为电容耦合和电感耦合。前者实际上是由干扰源电压变化引起的感应电流引起的电磁干扰,而后者实际上是干扰源电流变化引起的感应电压引起的电磁干扰。随着干扰源状态的变化,会在被干扰物体上产生一系列干扰脉冲,这在高速系统中很常见。

应对串扰的措施如下:

a.相邻平面之间的布线方向应保持正交性。不同信号线的相邻平面应避免同一方向,以减少串扰。尤其是在信号速率比较高的情况下,要考虑地线分开走线平面,信号线之间要用地线信号线隔开。

b.为了减少线路之间的串扰,线路之间的间距应该足够大。当线中心间距不小于线宽的3倍时,可以阻止70%的电场相互干扰,这就是3W原理。

c.在高速信号线满足要求的情况下,可以对连接端子进行匹配,以减少或消除反射,减少串扰。

信号完整性设计方法的应用

在PCB设计过程中,基于信号完整性理论总结了很多设计规则。参考这些PCB设计规则,可以更好地获得信号完整性。在PCB设计过程中,必须详细了解设计信息,包括:

a.元器件布局位置,对贴片元器件的大功率和散热有无特殊要求。

b.信号分类、速率、传输方向和阻抗匹配要求。

c.信号驱动能力、关键信号及保护措施。

d.电源的种类、地、电源和地的噪声限制要求、电源平面和地平面的设置和划分。

e.时钟线的类型和速率、时钟线的来源、方向、时钟的延迟要求和最大走线要求。

有用的资源:

• PCB 高速信号电路设计中的 3 种布线技术

• 高速 PCB 布局中信号反射的抑制方法

• 高速信号完整性分析和 PCB 设计数模混合电路

• 过孔的阻抗控制及其对 PCB 设计中信号完整性的影响

• PCBCart 的全功能 PCB 制造服务 - 多种增值选项

• 先进的 PCB 组装服务来自 PCBCart - 从 1 件开始

工业技术