逻辑信号电压电平

逻辑门的输入电压

逻辑门电路设计为仅输入和输出两种类型的信号:“高”(1) 和“低”(0),由可变电压表示:“高”状态为全电源电压,“高”状态为零电压。 “低”状态。在一个完美的世界中,所有逻辑电路信号都将存在于这些极端电压限制下,并且永远不会偏离它们(即“高”低于全电压,或“低”高于零电压)。

然而,实际上,由于晶体管电路中的杂散电压下降,逻辑信号电压电平很少达到这些完美的限制,因此我们必须了解门电路的信号电平限制,因为它们试图解释位于之间的信号电压 /em> 全电源电压和零。

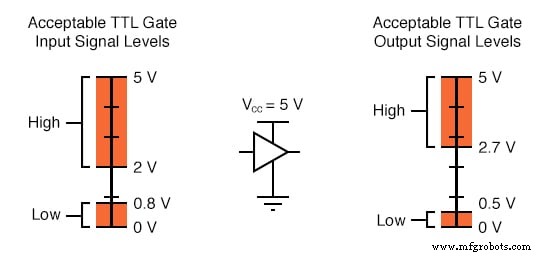

TTL 门输入的电压容限

TTL 门在 5 伏(+/- 0.25 伏)的标称电源电压下运行。理想情况下,TTL“高”信号恰好为 5.00 伏,而 TTL“低”信号恰好为 0.00 伏。

然而,真正的 TTL 门电路不能输出如此完美的电压电平,并且被设计为接受与这些理想值有很大偏差的“高”和“低”信号。

对于“低”逻辑状态,“可接受的”输入信号电压范围为 0 伏到 0.8 伏,对于“高”逻辑状态,范围为 2 伏到 5 伏。

“可接受的”输出信号电压(栅极制造商在指定负载条件范围内保证的电压电平)范围为“低”逻辑状态的 0 伏至 0.5 伏,“高”逻辑状态的 2.7 伏至 5 伏:

如果将 0.8 伏到 2 伏之间的电压信号发送到 TTL 门的输入端,门将没有确定的响应。这样的信号将被视为不确定 ,并且没有逻辑门制造商会保证他们的门电路如何解释这样的信号。

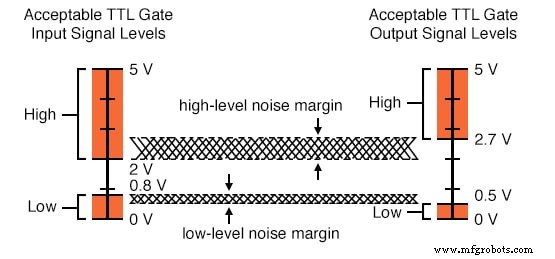

TTL 噪声余量

如您所见,输出信号电平的容许范围比输入信号电平窄,以确保任何将数字信号输出到另一个 TTL 门的输入的 TTL 门将传输接收门可接受的电压。可容忍的输出范围和输入范围之间的差异称为噪声容限 的大门。

对于 TTL 门,低电平噪声容限是 0.8 伏和 0.5 伏(0.3 伏)之间的差异,而高电平噪声容限是 2.7 伏和 2 伏(0.7 伏)之间的差异。简单地说,噪声容限是在接收门可能错误解释之前叠加在弱门输出电压信号上的杂散或“噪声”电压的峰值量:

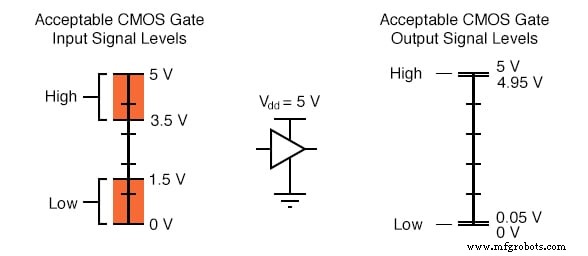

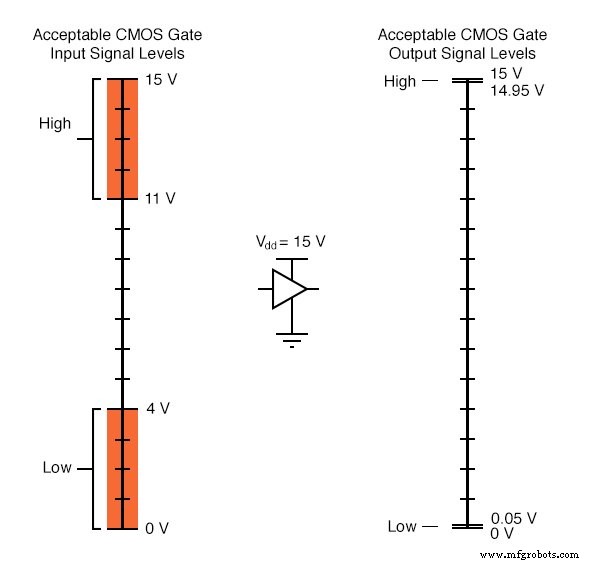

CMOS 栅极输入的电压容限

CMOS 门电路具有与 TTL 完全不同的输入和输出信号规格。对于在 5 伏电源电压下工作的 CMOS 门,“低”逻辑状态可接受的输入信号电压范围为 0 伏至 1.5 伏,“高”逻辑状态为 3.5 伏至 5 伏。

“可接受的”输出信号电压(栅极制造商在指定负载条件范围内保证的电压电平)范围为“低”逻辑状态的 0 伏至 0.05 伏,“高”逻辑状态的 4.95 伏至 5 伏:

CMOS 噪声容限

从这些图中可以明显看出,CMOS 门电路的噪声容限远大于 TTL:CMOS 低电平和高电平余量为 1.45 伏,而 TTL 的最大噪声容限为 0.7 伏。换句话说,在导致信号解释错误之前,CMOS 电路可以承受其输入线上两倍以上的叠加“噪声”电压。

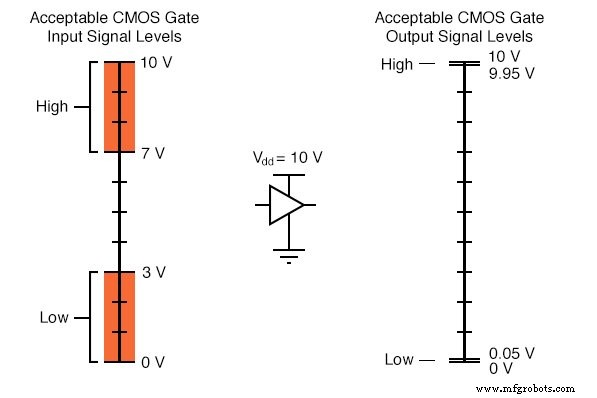

较高工作电压下的噪声容限

CMOS 噪声容限随着工作电压的升高而进一步扩大。与 TTL 的供电电压限制为 5 伏不同,CMOS 可以由高达 15 伏的电压供电(有些 CMOS 电路高达 18 伏)。

此处显示的是分别在 10 伏和 15 伏下工作的 CMOS 集成电路的输入和输出可接受的“高”和“低”状态:

可接受的“高”和“低”信号的余量可能大于前图中所示的余量。所示内容代表“最坏情况”输入信号性能,基于制造商的规格。在实践中,可能会发现门电路可以容忍比此处指定的电压低得多的“高”信号和电压明显高得多的“低”信号。

相反,所显示的极小输出裕度——保证“高”和“低”信号的输出状态在电源“轨”的 0.05 伏以内——是乐观的。这种“稳定”的输出电压电平仅适用于最小负载的条件。如果栅极向负载提供或吸收大量电流,由于栅极最终输出 MOSFET 的内部沟道电阻,输出电压将无法保持这些最佳水平。

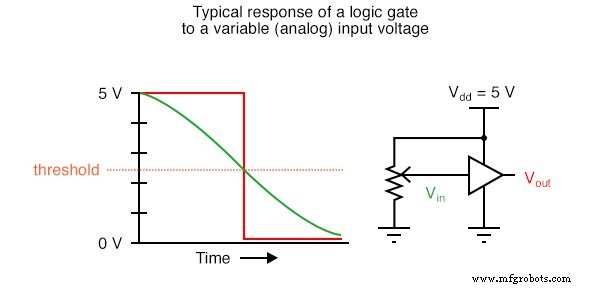

电压阈值

在任何门输入的“不确定”范围内,会有一些分界点将门的实际“低”输入信号范围与其实际“高”输入信号范围分开。也就是说,在栅极制造商保证的最低“高”信号电压电平和最高“低”信号电压电平之间,有一个阈值电压,栅极实际上 将其对信号的解释从“低”或“高”切换,反之亦然。对于大多数门电路,这个未指定的电压是一个点:

交流噪声输入

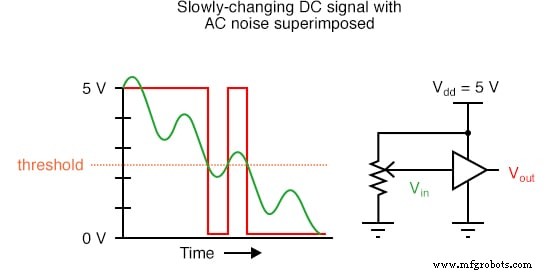

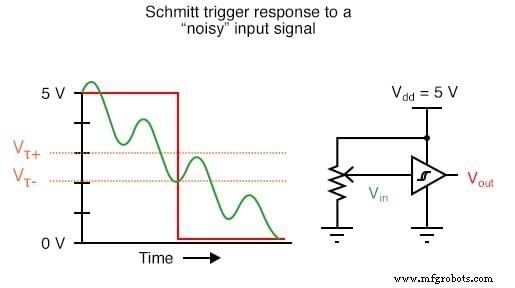

在交流“噪声”电压叠加在直流输入信号上的情况下,门改变其逻辑电平解释的单个阈值点将导致输出不稳定:

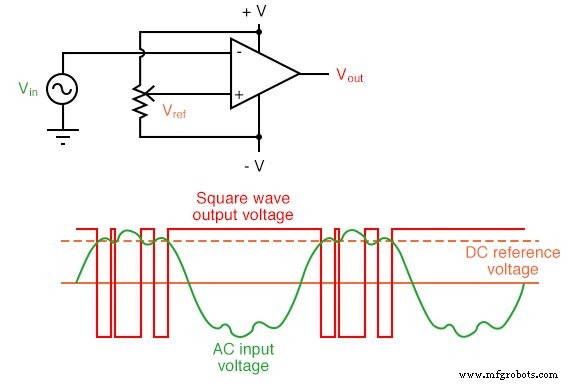

如果您觉得这种情况很熟悉,那是因为您还记得(模拟)电压比较器运算放大器电路存在类似问题。由于输入导致输出在“高”和“低”状态之间切换的单个阈值点,显着噪声的存在将导致输出发生不稳定变化:

施密特触发器

这个问题的解决方案有点积极 反馈引入放大器电路。对于运算放大器,这是通过将输出通过电阻连接回同相 (+) 输入来实现的。

在栅极电路中,这需要重新设计内部栅极电路,在栅极封装内部而不是通过外部连接建立反馈。如此设计的门称为施密特触发器 .施密特触发器根据两个解释变化的输入电压 阈值电压:正向 阈值 (VT+) 和一个负向 阈值(VT-):

施密特触发门中的滞后

施密特触发器门在示意图中通过其中绘制的小“磁滞”符号来区分,让人联想到铁磁材料的 B-H 曲线。由门电路内的正反馈产生的迟滞为门的性能增加了额外的抗噪水平。

施密特触发门经常用于输入信号线上预计会有噪声和/或不稳定输出对系统性能非常有害的应用中。

在同一系统中使用 TTL 和 CMOS 技术

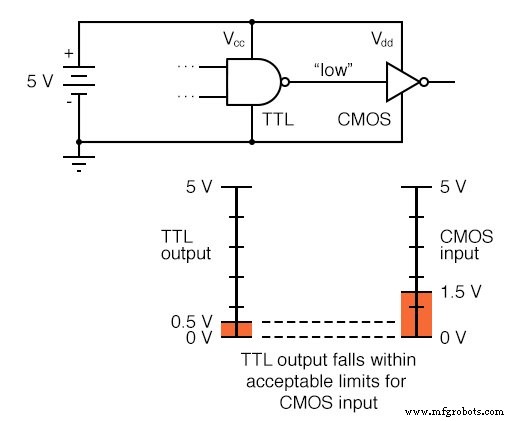

当在同一系统中使用两种类型的门时,TTL 和 CMOS 技术的不同电压电平要求会出现问题。虽然在 TTL 门所需的相同 5.00 伏电源电压上操作 CMOS 门是没有问题的,但 TTL 输出电压电平将与 CMOS 输入电压要求不兼容。

TTL和CMOS组合电路示例

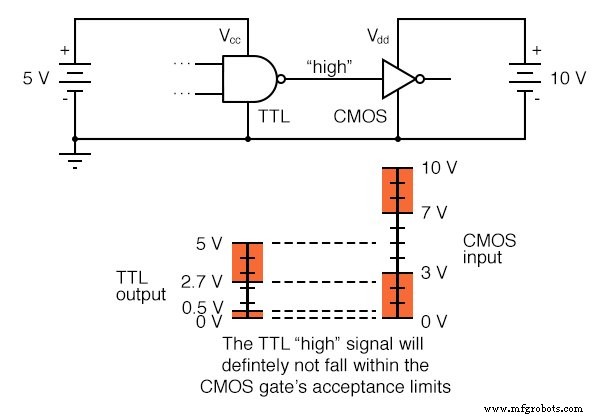

以将信号输出到 CMOS 反相器门的输入的 TTL 与非门为例。两个门都由相同的 5.00 伏电源 (Vcc) 供电。如果 TTL 门输出“低”信号(保证在 0 伏和 0.5 伏之间),它将被 CMOS 门的输入正确解释为“低”(期望电压在 0 伏和 1.5 伏之间):

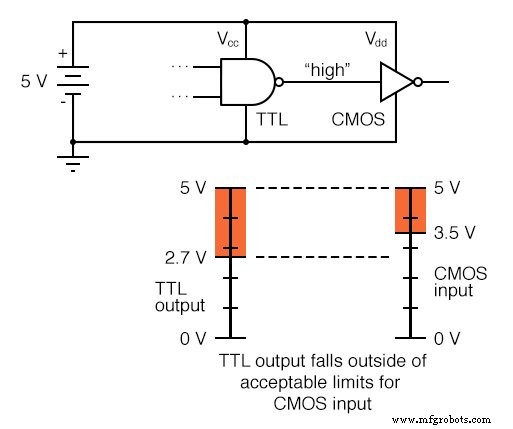

但是,如果 TTL 门输出“高”信号(保证在 5 伏到 2.7 伏之间),它可能 没有被 CMOS 门的输入正确解释为“高”(预计电压在 5 伏到 3.5 伏之间):

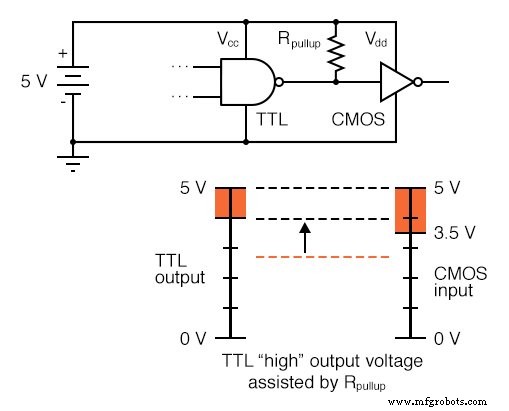

鉴于这种不匹配,TTL 门完全有可能输出一个有效的“高”信号(有效,即根据 TTL 的标准),该信号位于 CMOS 输入的“不确定”范围内,并且可能是(错误地)被接收门解释为“低”。这个问题的一个简单“修复”是通过一个上拉电阻来增加 TTL 门的“高”信号电压电平:

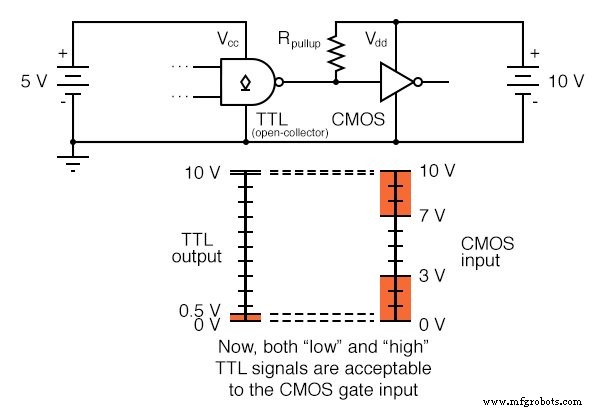

但是,如果接收 CMOS 门由更高的电源电压供电,则需要更多的东西将 TTL 输出与 CMOS 输入接口:

使用带有 CMOS 门的开路集电极 TTL 门

当然,CMOS 门解释 TTL 门的“低”输出没有问题,但来自 TTL 门的“高”信号完全是另一回事。 TTL 栅极输出的 2.7 伏至 5 伏保证输出电压范围远不及 CMOS 栅极可接受的“高”信号的 7 伏至 10 伏范围。

如果我们使用 open-collector 然而,TTL 门而不是图腾柱输出门,连接到 10 伏 Vdd 电源轨的上拉电阻会将 TTL 门的“高”输出电压提高到为 CMOS 门供电的全电源电压。由于集电极开路只能灌电流,不能拉电流,“高”态电压电平完全由上拉电阻所连接的电源决定,从而巧妙地解决了失配问题:

CMOS输出转TTL输入的问题

由于 CMOS 门极好的输出电压特性,将 CMOS 输出连接到 TTL 输入通常没有问题。唯一重要的问题是 TTL 输入呈现的电流负载,因为 CMOS 输出必须在处于“低”状态时为每个 TTL 输入吸收电流。

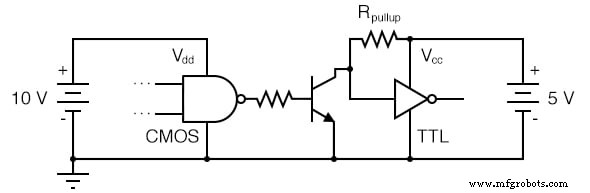

但是,当有问题的 CMOS 栅极由超过 5 伏 (Vcc) 的电压源供电时,就会出现问题。 CMOS 门的“高”输出状态大于 5 伏特,将超过“高”信号的 TTL 门可接受的输入限制。

使用集电极开路逆变电路

这个问题的解决方案是使用分立的 NPN 晶体管创建一个“集电极开路”反相器电路,并用它来将两个栅极连接在一起:

“Rpullup”电阻是可选的,因为 TTL 输入当悬空时自动呈现“高”状态,这就是当 CMOS 栅极输出为“低”并且晶体管截止时会发生的情况。当然,实现该解决方案的一个非常重要的结果是晶体管产生的逻辑反转:当 CMOS 门输出“低”信号时,TTL 门看到“高”输入;当 CMOS 门输出“高”信号时,晶体管饱和,TTL 门看到“低”输入。只要在系统的逻辑方案中考虑到这种反转,一切都会好起来的。

相关工作表:

-

数字逻辑信号工作表

工业技术