D 门闩

由于门控 SR 锁存器上的使能输入提供了一种在不考虑 S 或 R 状态的情况下锁存 Q 和非 Q 输出的方法,我们可以消除这些输入中的一个以创建一个没有“非法”输入的多谐振荡器锁存电路状态。

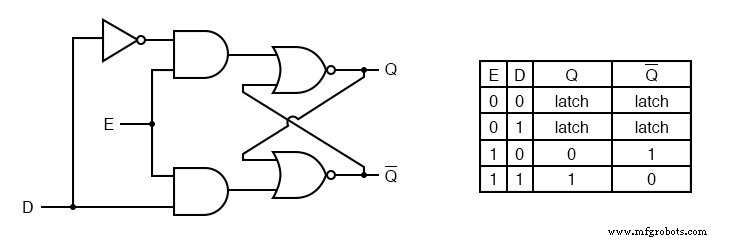

这样的电路称为D锁存器,其内部逻辑是这样的:

请注意,R 输入已替换为旧 S 输入的补码(反转),并且 S 输入已重命名为 D。与门控 SR 锁存器一样,如果启用,D 锁存器将不会响应信号输入输入为 0——它只是保持锁定在最后一个状态。然而,当使能输入为 1 时,Q 输出跟随 D 输入。

由于 S-R 电路的 R 输入已被取消,因此该锁存器没有“无效”或“非法”状态。 Q 和非 Q 总是 彼此相反。

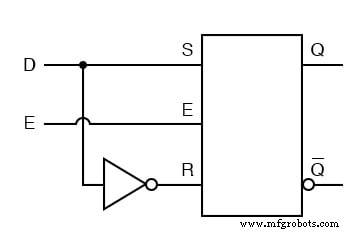

如果上图完全令人困惑,下图应该使概念更简单:

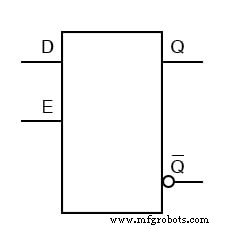

与 S-R 和门控 S-R 锁存器一样,D 锁存器电路可以作为它自己的预封装电路找到,并带有标准符号:

D 锁存器只不过是一个门控 S-R 锁存器,添加了一个反相器,使 R 成为 S 的补码(反相)。

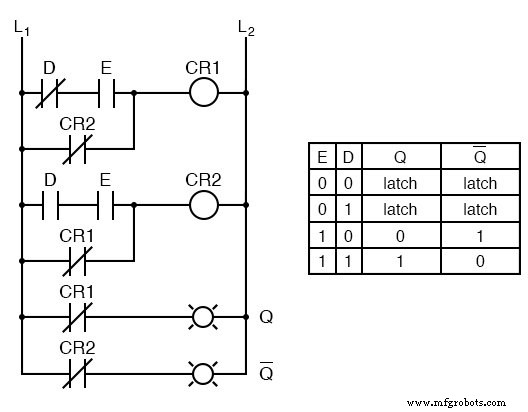

让我们探索 D 锁存器的梯形逻辑等价物,修改自 S-R 锁存器的基本梯形图:

D 锁存器的一个应用是 1 位存储电路。您可以通过使使能输入为高电平 (1) 并将 D 设置为您希望存储位的任何值,在此锁存电路中“写入”(存储)0 或 1 位。当使能输入变为低电平 (0) 时,锁存器忽略 D 输入的状态并快乐地保持存储的位值,在 Q 处以存储值输出,在输出非 Q 处取反。

评论:

- D 锁存器类似于 S-R 锁存器,只有一个输入:“D”输入。激活 D 输入设置电路,停用 D 输入复位电路。当然,这仅在启用输入 (E) 也被激活的情况下。否则,输出将被锁存,对 D 输入的状态无响应。

- D 锁存器可用作 1 位存储器电路,禁用时存储“高”或“低”状态,启用时从 D 输入“读取”新数据。

相关工作表:

- 锁存电路 - D 锁存工作表

工业技术