边缘触发锁存器:触发器

到目前为止,我们已经研究了具有使能输入的 S-R 和 D 锁存电路。只有当启用输入被激活时,锁存器才会响应数据输入(S-R 或 D)。然而,在许多数字应用中,希望将锁存电路的响应限制在非常短的时间段内,而不是将启用输入激活的整个持续时间。

启用多谐振荡器电路的一种方法称为边沿触发 ,其中电路的数据输入仅在启用输入转换期间具有控制权 从一种状态到另一种状态。

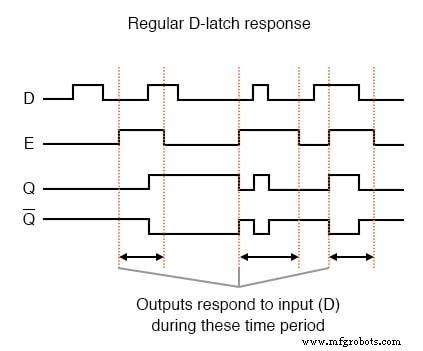

让我们比较普通 D 锁存器与边沿触发的时序图:

在第一个时序图中,只要使能 (E) 输入为高电平,无论它保持高电平多久,输出都会响应输入 D。当使能信号回落到低电平时,电路保持锁存。

在第二个时序图中,我们注意到电路输出中有明显不同的响应:它仅在使能信号改变的那段短暂时间内响应 D 输入 , 或 过渡 ,从低到高。这被称为积极 边缘触发。

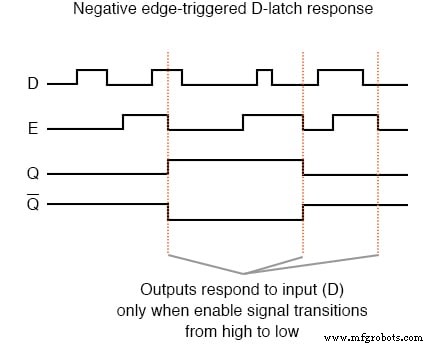

有一种否定 边沿触发,它对相同的输入信号产生以下响应:

每当我们在方波使能信号的过渡沿上使能多谐振荡器电路时,我们称其为触发器 而不是闩锁 .

因此,边沿触发的 S-R 电路更恰当地称为 S-R 触发器,而边沿触发的 D 电路称为 D 触发器。使能信号重命名为clock 信号。此外,我们将这些触发器的数据输入(分别为 S、R 和 D)称为同步 输入,因为它们仅在时钟脉冲边沿(转换)时起作用,从而使任何输出变化与该时钟脉冲同步,而不是在数据输入的突发奇想时。

但是,我们如何真正实现这种边缘触发呢?从常规 S-R 锁存器创建“门控”S-R 锁存器使用几个与门很容易,但是我们如何实现只关注上升沿或下降沿的逻辑 变化的数字信号?

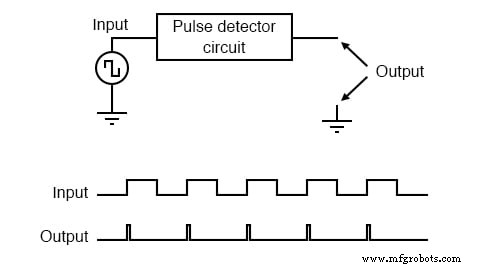

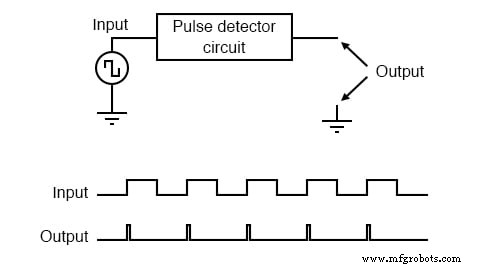

我们需要的是一个数字电路,只要输入被激活一段时间,就会输出一个短暂的脉冲,我们可以使用这个电路的输出来短暂地启用锁存器。我们在这里有点超前了,但这实际上是一种单稳态多谐振荡器,现在我们称之为脉冲检测器 .

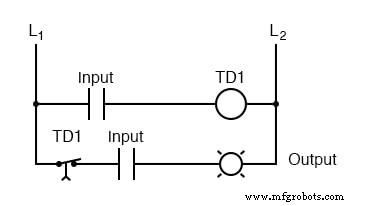

每个输出脉冲的持续时间由脉冲电路本身的组件设置。在梯形逻辑中,这可以通过使用具有极短延迟时间的延时继电器轻松实现:

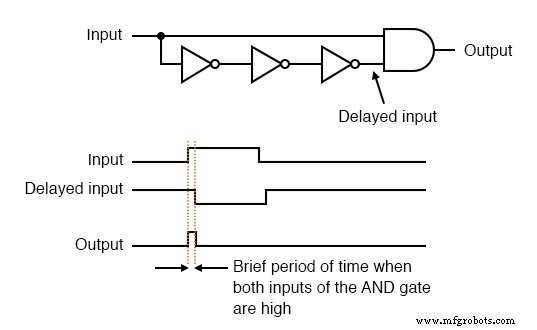

用半导体元件实现这种计时功能实际上很容易,因为它利用了每个逻辑门内的固有时间延迟(称为传播延迟 )。我们所做的是将输入信号分成两种方式,然后在其中一个信号路径中放置一个门或一系列门只是为了延迟一点,然后让原始信号和延迟的对应信号进入两输入门,在延迟信号尚未赶上非延迟信号的低到高变化的短时间内输出高信号。此处显示了用于在输入信号从低到高转换时产生时钟脉冲的示例电路:

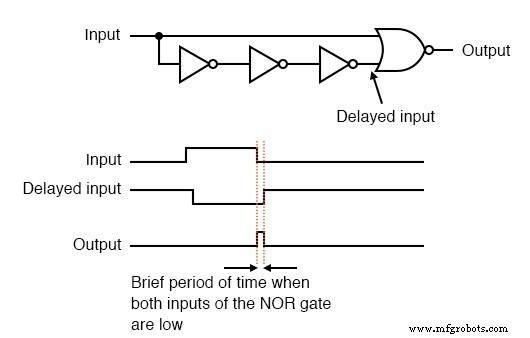

这个电路可以转换成一个负沿脉冲检测器电路,只需要将最终的门从AND变为NOR即可:

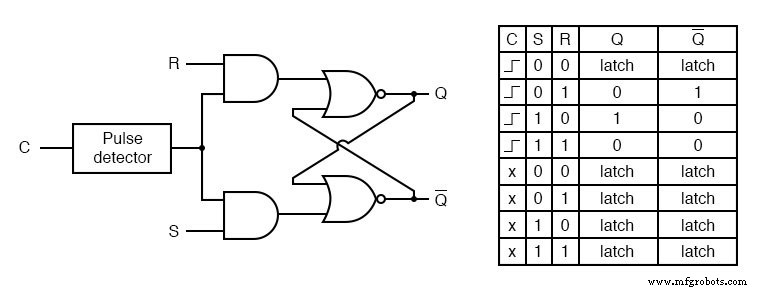

现在我们知道如何制作脉冲检测器,我们可以展示它连接到锁存器的启用输入端,将其变成触发器。在这种情况下,电路是一个 S-R 触发器:

只有当时钟信号 (C) 从低电平转换为高电平时,电路才会响应 S 和 R 输入。对于时钟信号(“x”)的任何其他条件,电路将被锁存。

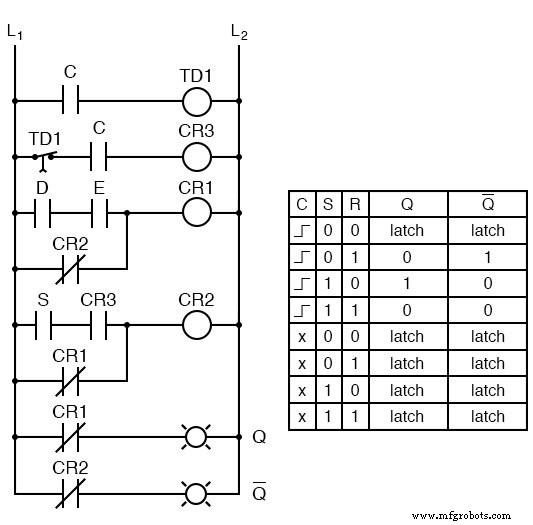

S-R 触发器的梯形逻辑版本如下所示:

梯形图中的继电器触点 CR3 代替了 S-R 锁存电路中旧的 E 触点,并且仅在 C 闭合和延时触点 TR1 闭合的短时间内闭合。在任一情况下(门电路或梯形电路),我们看到输入 S 和 R 没有影响,除非 C 从低 (0) 状态转换为高 (1) 状态。否则,触发器的输出锁存于其先前的状态。

需要注意的是,S-R 触发器的无效状态仅在脉冲检测器电路允许锁存器启用的短时间内保持。在这段短暂的时间过后,输出将锁定到设置或复位状态。再次,竞争条件的问题 表现出来。如果没有使能信号,则无法保持无效的输出状态。然而,多谐振荡器的有效“锁定”状态——置位和复位——是相互排斥的。因此,多谐振荡器电路的两个门会“竞争”至高无上,谁先达到高输出状态就“获胜”。

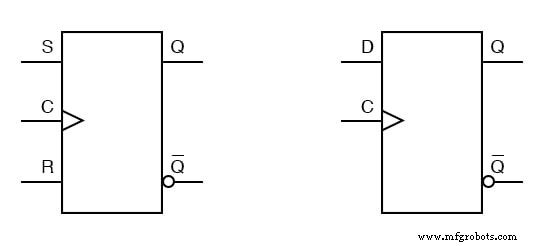

触发器的块符号与其对应的锁存器的块符号略有不同:

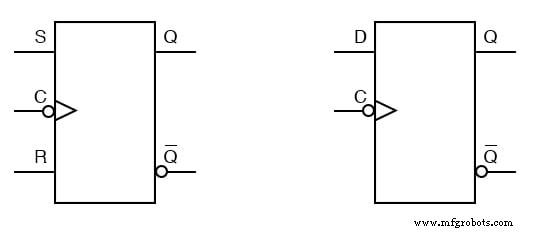

时钟输入旁边的三角形符号告诉我们这些是边沿触发的设备,因此它们是触发器而不是锁存器。上面的符号是正边沿触发的:也就是说,它们在时钟信号的上升沿(低到高转换)“计时”。负沿触发设备在时钟输入线上用气泡符号表示:

上述两个触发器都将在时钟信号的下降沿(高到低转换)“计时”。

评论:

- 一个触发器 是一个锁存电路,其“脉冲检测器”电路连接到启用 (E) 输入端,因此它仅在时钟脉冲的上升沿或下降沿短暂启用。

- 脉冲检测器电路可以由用于梯形逻辑应用的延时继电器制成,也可以由半导体门制成(利用传播延迟现象 ).

相关工作表:

- 人字拖工作表

工业技术