跟踪 ADC

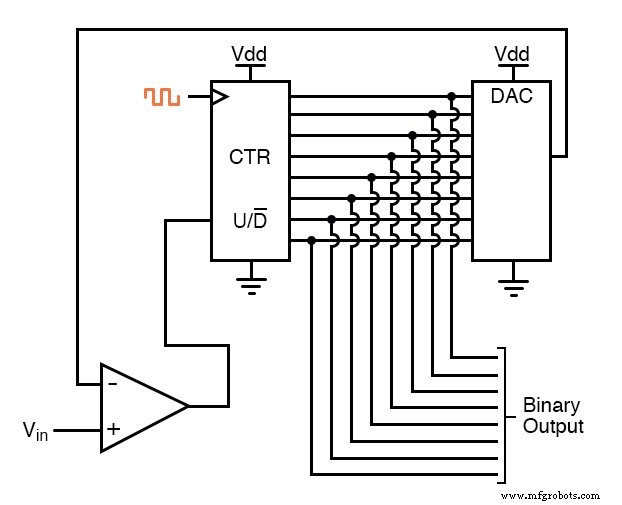

在我看来,基于计数器 DAC 的转换器主题的第三种变体是最优雅的。该电路使用一个递增/递减计数器,而不是驱动 DAC 的常规“递增”计数器。

计数器连续计时,上/下控制线由比较器的输出驱动。因此,当模拟输入信号超过 DAC 输出时,计数器进入“向上计数”模式。

当 DAC 输出超过模拟输入时,计数器切换到“向下计数”模式。无论哪种方式,DAC 输出始终在正确的方向计数以跟踪 输入信号。

注意在循环结束时不需要移位寄存器来缓冲二进制计数。由于计数器的输出连续跟踪输入(而不是计数以满足输入然后重置回零),二进制输出会随着每个时钟脉冲合法地更新。

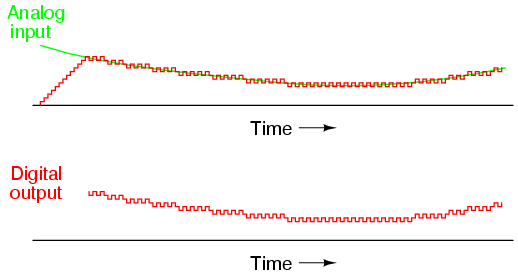

这种转换器电路的一个优点是速度,因为计数器永远不必复位。注意这个电路的行为:

请注意,更新时间比任何其他“计数”ADC 电路快得多。另请注意,在计数器必须“赶上”模拟信号的情节的最开始,输出的变化率与第一个计数 ADC 的变化率相同。

此外,由于该电路中没有移位寄存器,二进制输出实际上会上升,而不是像计数器和逐次逼近 ADC 电路那样从零跳到准确计数。

也许这种 ADC 设计的最大缺点是二进制输出永远不稳定:它总是在每个时钟脉冲的计数之间切换,即使是完美稳定的模拟输入信号。这种现象被非正式地称为 bit bobble ,并且在某些数字系统中可能会出现问题。

不过,可以通过创造性地使用移位寄存器来克服这种趋势。例如,只有当输出变化两步或更多步时,计数器的输出才可以通过并行输入/并行输出移位寄存器锁存。构建一个电路来检测同一个方向上的两个或多个连续计数需要一点聪明才智,但值得付出努力。

相关工作表:

- 模数转换工作表

工业技术