晶体管触发器:一种用于存储二进制数据的时序逻辑电路

您是否有兴趣学习或制作计算机、通信设备和其他类似系统中的数字电路?首先要看的应该是晶体管触发器。

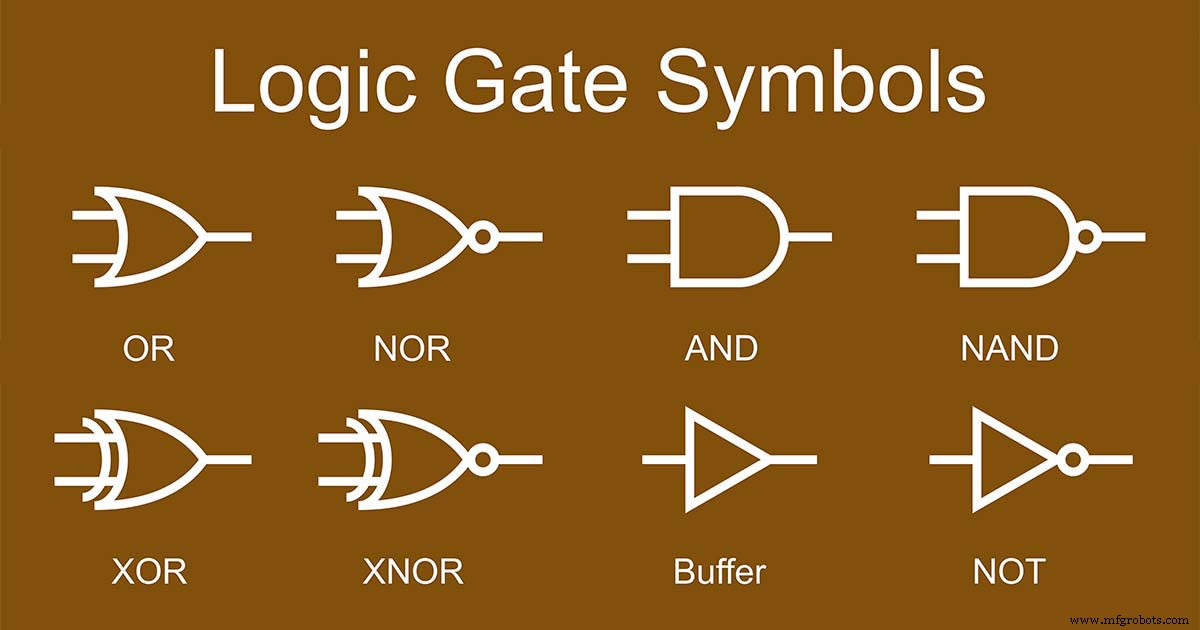

触发器的基本构建块是逻辑门,它是实现布尔函数的理想化电子模型。这些逻辑门可能有几个组件,比如电容器和电阻器,但它们主要是晶体管。

我们在下面详细介绍了不同类型的触发器电路及其接线图。继续阅读以了解如何为您的项目制作它们。

什么是人字拖?

触发器是具有某种形式的内置存储器的时序逻辑电路。因此,您可以使用来自当前输入、先前输入和(或)先前输出的数据来运行系统。

该电路由几个逻辑门组成,这些逻辑门导致两个稳定状态(逻辑电平 0 或 1),使触发器成为双稳态多谐振荡器。

不同类型的逻辑门

来源:维基共享资源。

锁存器和触发器电路之间的区别在于后者是边沿触发的。边沿触发意味着它们有一个控制信号来协调数字电路的动作。控制输入通常是一个专用的时钟信号,这使得它们成为同步系统。

但是,锁存电路是电平触发的,这意味着如果输入发生变化,其输出也会发生变化。没有时钟脉冲或时钟事件来激活它们,因此它们是异步系统。

值得注意的是,锁存器是触发器电路中必不可少的元件,属于易失性存储元件,一旦断电,数据就会丢失。

人字拖的种类

有四种触发器类型,每种都有不同的电路设计和真值表。

SR 人字拖

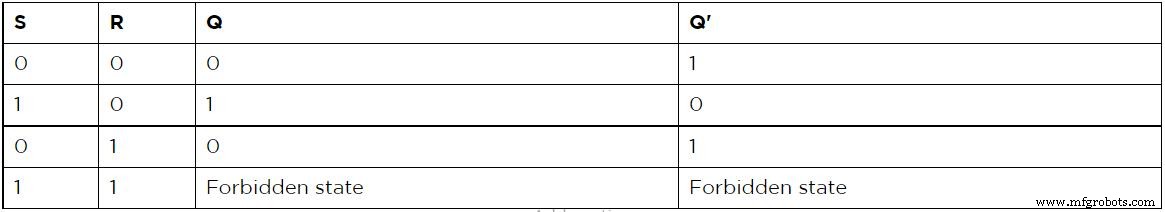

SR 触发器的名称来自其 S(设置)和 R(复位)输入。

具有交叉耦合与非门的时钟 SR 触发器电路。

来源:维基共享资源。

它是四者中最常用的触发器,电路最简单,真值表与SR锁存器相似。

SR 锁存真值表。

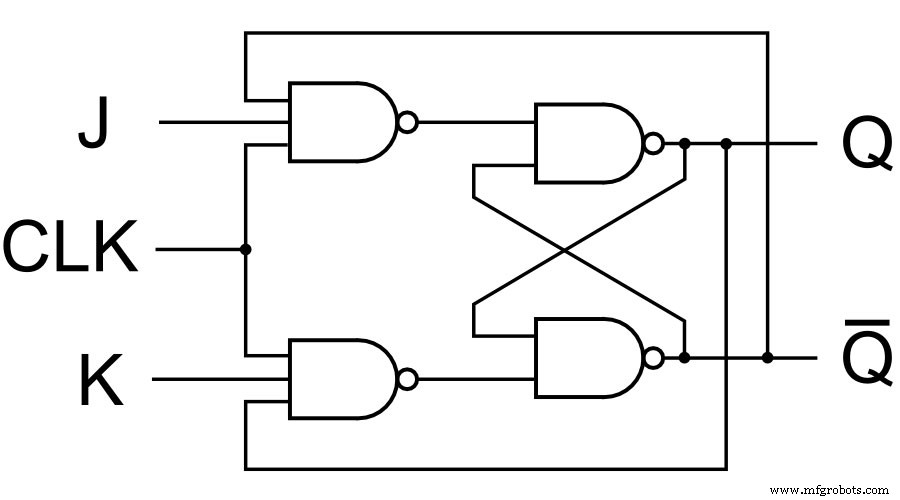

JK 人字拖

JK 数字电路通过确保 S 和 R 不会同时为高电平来改进 SR 触发器的设计。这样一来,就消除了处于禁止状态的可能性。

使用 NAND 门的 JK 触发器电路。

来源:维基共享资源。

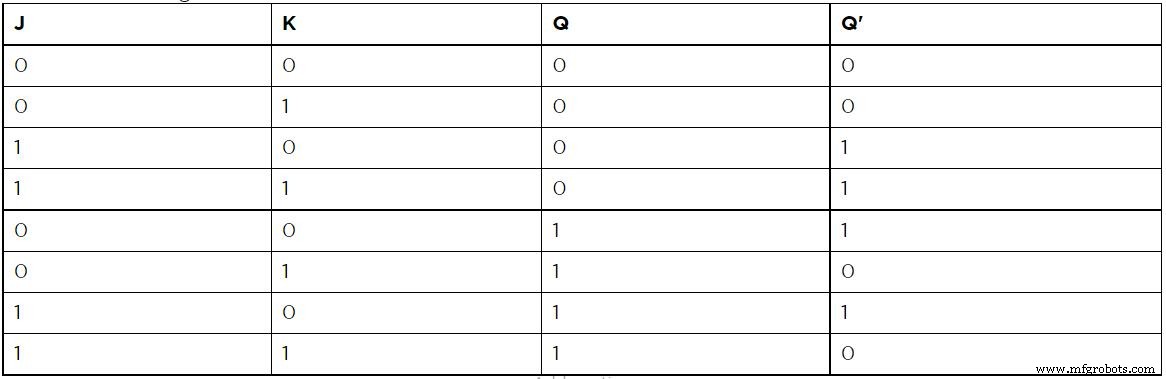

有如下真值表。

JK 触发器真值表。

D 触发器

该电路也称为“数据”或“延迟”触发器,是一个具有一个输入引脚 (D) 的一位存储单元。在数字电子系统中最常用于制作寄存器和计数器。

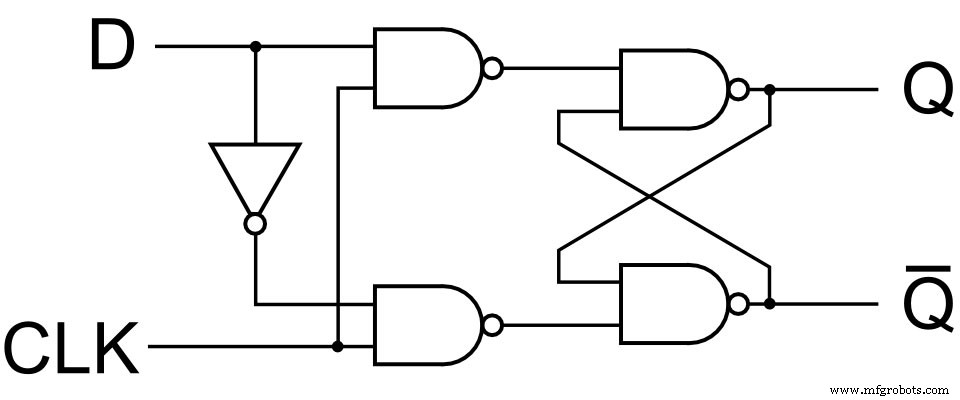

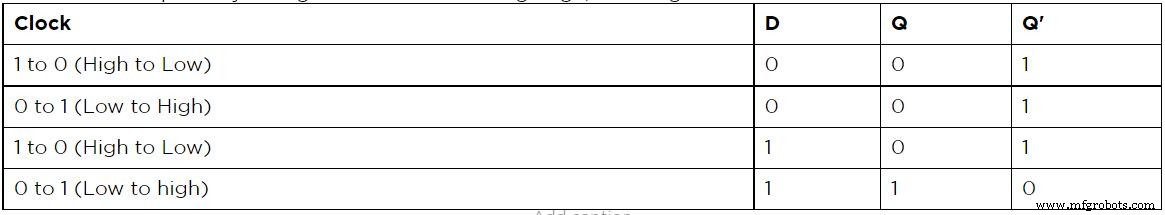

使用一个非门和 4 个与非门的 D 触发器电路。

来源:维基共享资源。

电路的输出只在时钟的上升沿发生变化,从而产生了这个真值表。

D 触发器真值表。

T 触发器

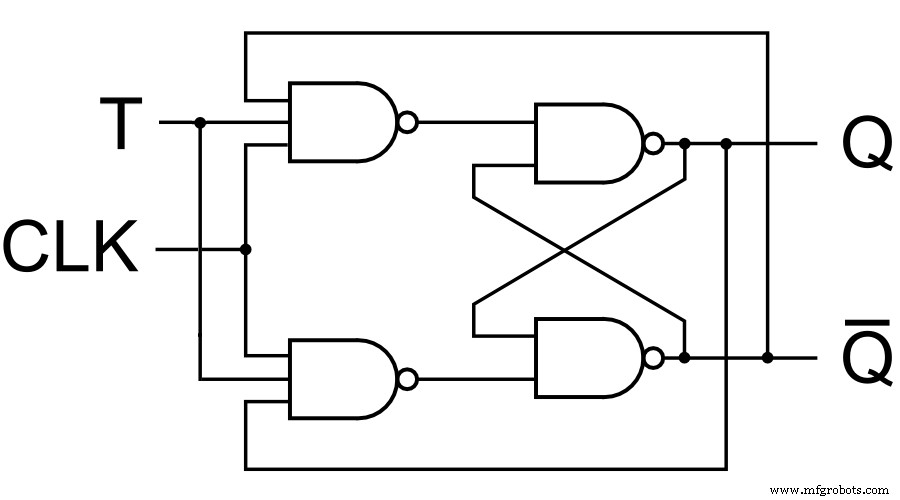

T 触发器是 JK 触发器的单输入版本,连接两个馈电以形成 T 输入。 T 代表 Toggle,因为电路可以补充其状态。

使用 NAND 门的 T 触发器电路

来源:维基共享资源。

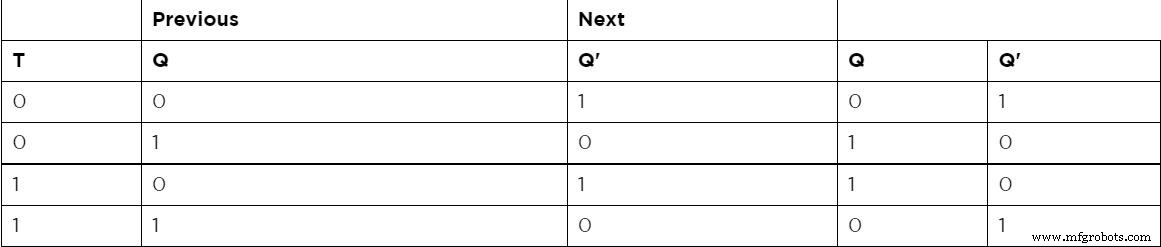

电路给出了这个真值表。

T 触发器真值表。

人字拖的应用

- 计数器

- 分频器

- 存储寄存器

- 移位寄存器

- 闩锁

- 记忆

- 弹跳消除开关

- 数据存储

- 数据传输

- 注册

晶体管触发器电路

逻辑门是触发器中的主要元素,但它们是代表电子学中逻辑的模型。真实的电路具有交叉耦合组件来控制此电流。它们的真值表中的值表示二进制数字 1(高压)或 0(低压)。

它们包括晶体管、电阻器和电容器等组件,在这里,我们将制作三种最常见的电路。

单晶体管触发器

与其他传统触发器一样,单型晶体管存储一位数据,它具有一组设置和复位输入以及一个反馈回路以保持状态稳定。

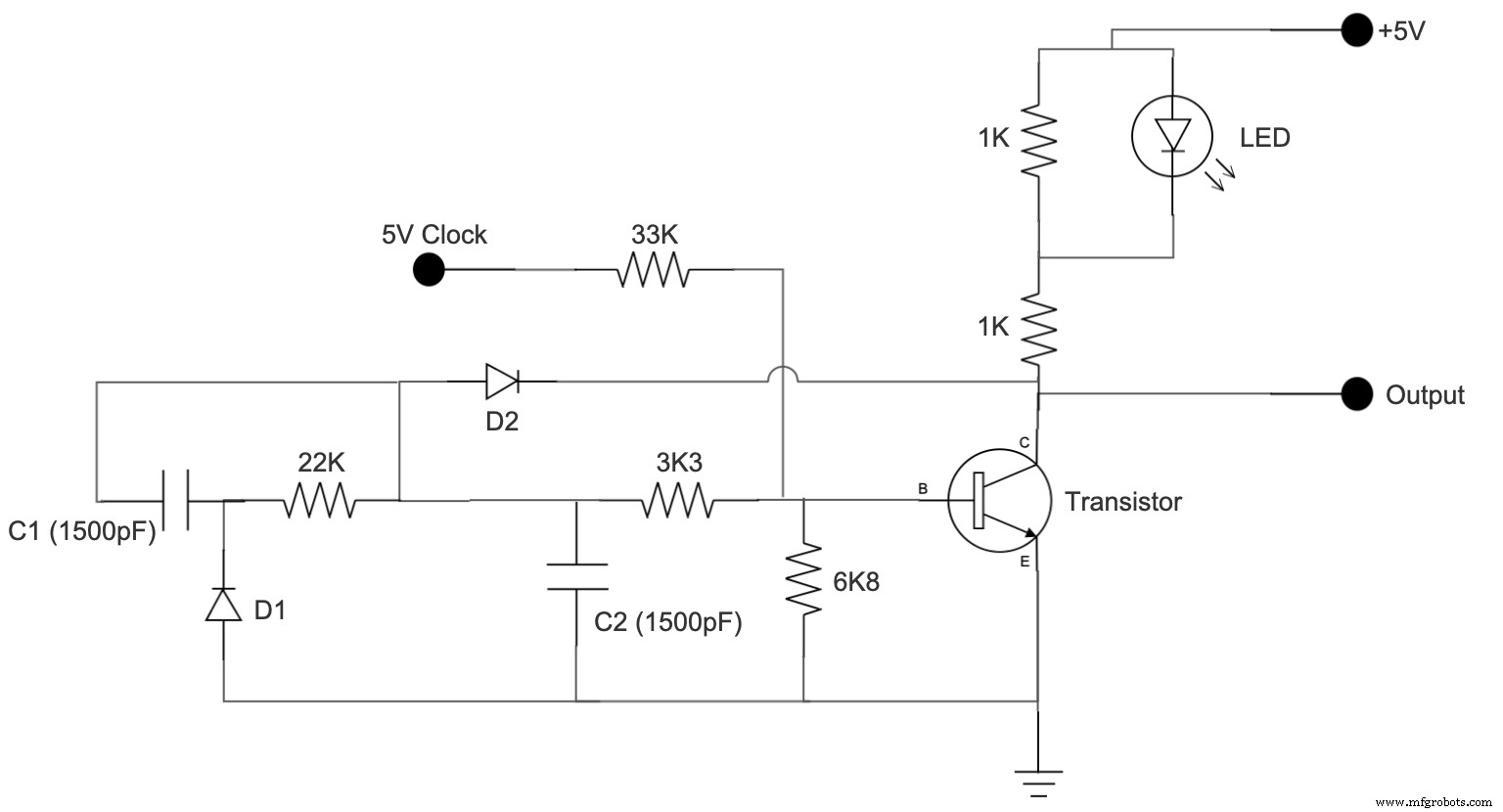

除了晶体管(NPN)外,该电路还具有一组两个二极管、两个电容器、六个电阻器和一个 LED。

单晶体管触发器电路图。

从上图中,您可以通过激活 C2 的电源电压来设置电路。这个 5V 脉冲提高了晶体管的基极电压并放大了时钟信号。 C1 和 D1 将对输出信号进行整流,使产生的直流电压出现在 C2 上。

该电路维持一个正反馈回路,使触发器保持在 ON 状态。 D2 防止晶体管饱和(电流过大),从而防止持续导通状态,从而消除正反馈信号。

要关闭电路,请将 C2 放电或短时间移除时钟信号。即使重新连接时钟信号,触发器也会保持关闭状态,因为 6K8 和 3K3 电阻和电容 C2 会严重衰减高输入。

使用晶体管的 D 触发器电路

D型触发器电路有一个门控D锁存器作为其布线的基础,但增加了一个时钟电路使其成为边沿触发的D触发器。

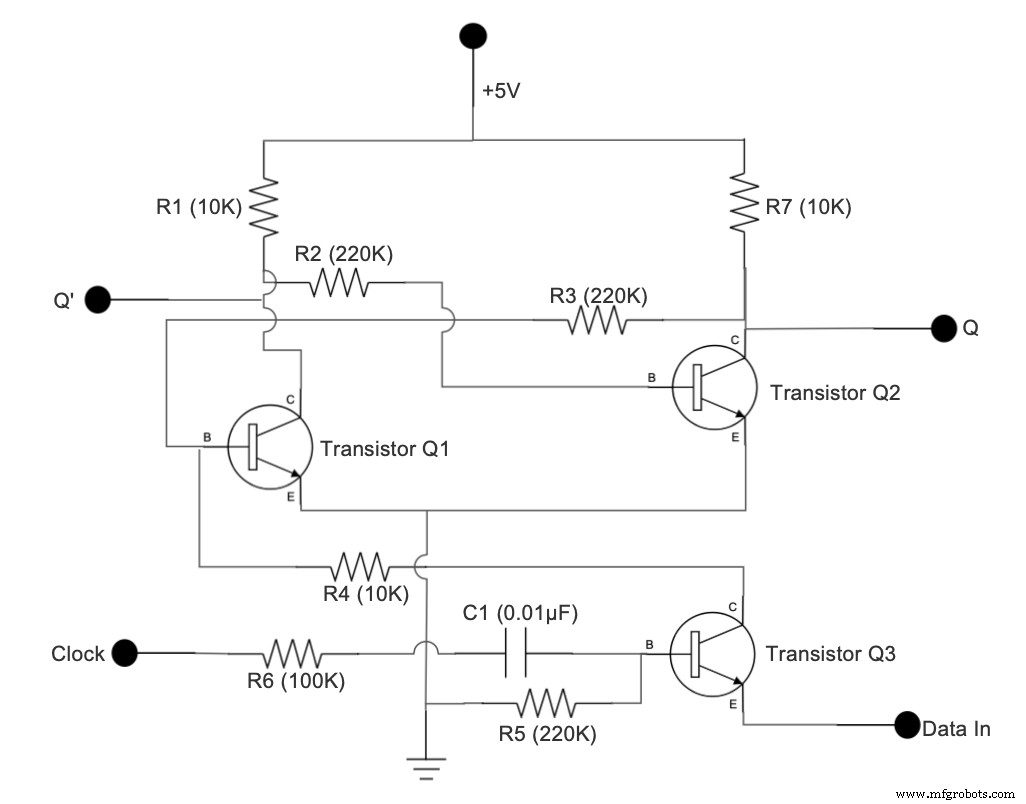

A D 触发器晶体管电路图。

图的下半部分由晶体管、电容器和三个电阻组成,构成了时钟机制。

外部时钟提供基极电压,晶体管只有在具有正基极电压时才能传输输入数据。

电阻R6和电容C1将方波时钟信号转换为尖峰信号,以识别上升沿。

总体而言,锁存器部分有两个晶体管和四个电阻器,从时钟部分,电流输入流向电路中的锁存器晶体管。

如果输出 Q 为逻辑 0,您可以在时钟引脚和数据输入引脚上应用正信号。此操作将存储的数据或状态更改为 1。

时钟输入对晶体管基极充电并将基极正向偏置到集电极结。因此,当数据输入正信号进来时,它会导致小电流从底部流向集电极并进入锁存器。

电流最终触发锁存器,导致其在 Q 处将其状态更改为 1。要应用逻辑 0,请将 Data In 引脚接地,它会将 Q 移回 0 并存储该位。

使用分立晶体管的 T 触发器

Toggle 触发器与 Data 触发器非常相似,但不是有 Data In 输入,而是从互补输出 Q' 获取其信号。

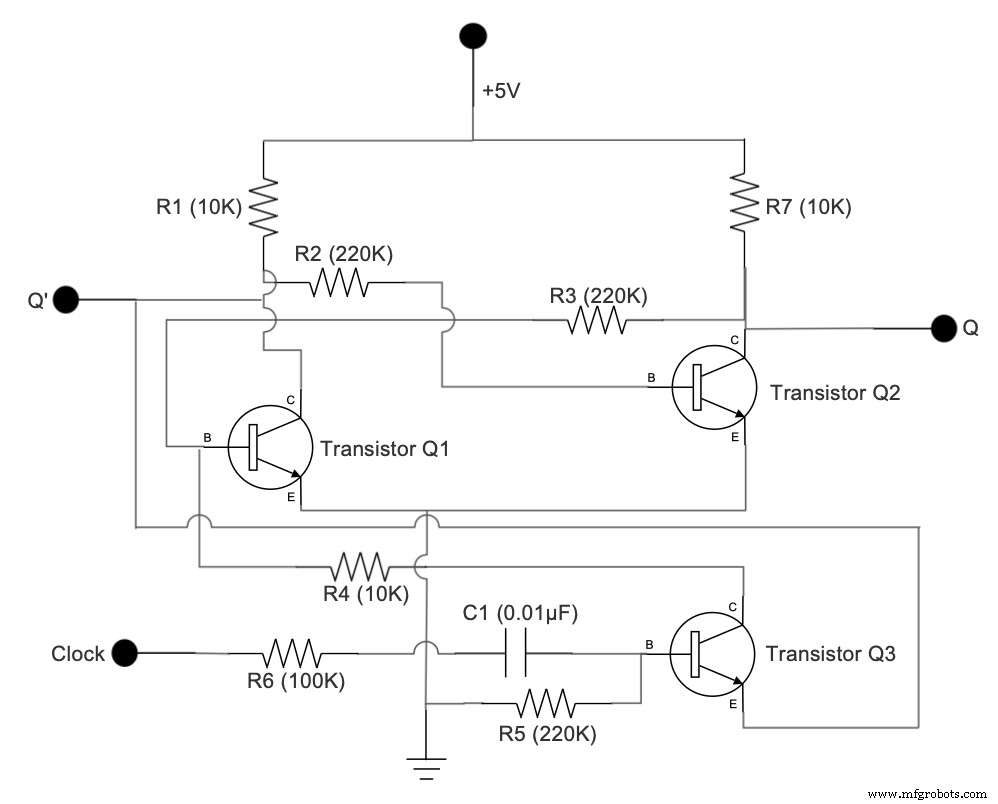

A T 触发器晶体管电路图

目标是在输出高时获得低数据输入,在工作低时获得高数据输入。因此,Q' 在方程中至关重要。

但是,由于它是一个分立电路,因此系统将无法工作,因为它相当于将晶体管基极连接到其集电极。您可以通过引入一个串联的额外电容器 C2 和一个连接到输出 Q 的电阻器 R8 来解决这个问题。

当电阻器对电容器放电时,电容器会在输入和输出信号之间产生延迟。这两者将确保晶体管输出如预期,不断转换状态。

总结

总之,晶体管触发器是大多数电子和计算机电路的基本组成部分,因为它们具有内置的记忆功能。

如果您的项目需要这样的电路,购买上述组件会更便宜,然后自己构建单元。

与我们联系以了解有关这些组件以及设置电路所需的 PCB 的更多信息。

工业技术