如何在 VHDL 中创建并发语句

VHDL 中的并发语句是架构内的信号分配,但在正常流程构造之外。并发语句也称为并发赋值或并发进程。

当您创建并发语句时,您实际上是在创建一个具有某些明确定义的特征的流程。并发语句总是等价于使用敏感度列表的过程,其中信号赋值运算符右侧的所有信号都在敏感度列表中。

当您想要创建导致分配单个信号的简单逻辑时,这些速记符号过程很有用。您可以直接在架构中简单地分配给目标信号,而不是输入带有灵敏度列表的完整过程结构和所有这些。

这篇博文是基本 VHDL 教程系列的一部分。

如果使用得当,代码的意图仍然很清楚。无需为您想要翻转的每一位创建一个流程。

运动

在本视频中,我们将学习如何创建并发语句:

我们在本教程中创建的最终代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

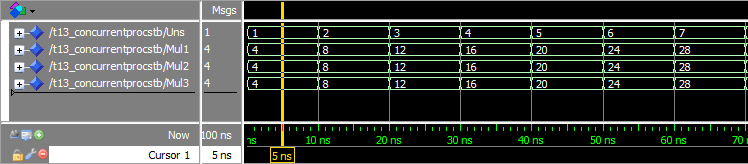

我们按下运行后 ModelSim 中的波形窗口,并在时间轴上放大:

分析

从波形可以看出Mul1 , Mul2 , 和 Mul3 行为完全相同。这是因为并发语句和我们创建的两个进程是等价的。

并发语句就像一个进程一样工作。 <= 右侧的所有信号 会自动添加到敏感度列表中。这意味着 <= 左侧的信号 每当评估的信号之一发生变化时都会更新。

在 VHDL 中有很多方法可以将数字相乘。在这个练习中,我们乘以 Uns 信号 4,使用位移。我们所有的信号都是 unsigned 类型,表示它们由数字解释。在二进制数的右边加一个 0 和乘以 2 是一样的。

这是波形中光标处发生的情况的说明:

外卖

- 并发语句是直接在架构区域中的信号分配

- 并发语句相当于一个进程,所有评估的信号都在敏感度列表中

转到下一个教程 »

VHDL