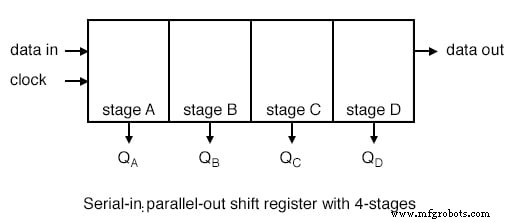

移位寄存器:串行输入、并行输出 (SIPO) 转换

串行输入并行输出移位寄存器类似于串行输入串行输出移位寄存器,因为它将数据移入内部存储元件,并在串行输出、数据输出引脚处将数据移出。

不同之处在于它使所有内部阶段都可用作输出。因此,串行输入并行输出移位寄存器将数据从串行格式转换为并行格式。

串行输入并行输出移位寄存器的使用示例

如果在下面的数据输入处通过一条单线将四个数据位移入四个时钟脉冲,则在第四个时钟脉冲之后,数据在四个输出 QA 到 QD 上同时可用。

串行输入并行输出移位寄存器的实际应用是将数据从单线上的串行格式转换为多线上的并行格式。

让我们用四个输出 (QA QB QC QD ) 点亮四个 LED(发光二极管) ).

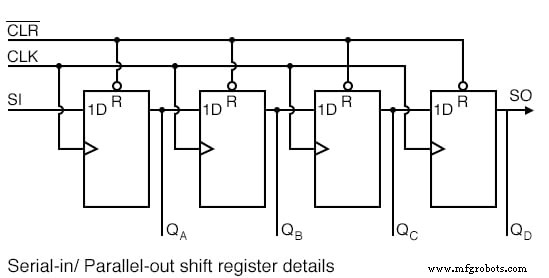

上述串入、并行输出移位寄存器的细节相当简单。它看起来像一个串行输入串行输出移位寄存器,每级输出都添加了抽头。

串行数据移入 SI (串行输入)。经过与阶段数相等的时钟数后,第一个数据位in出现在上图中的SO(QD)处。

一般情况下,没有 SO 引脚。最后一个阶段(上面的 QD)用作 SO,如果存在,则级联到下一个封装。

串行输入、并行输出与串行输入、串行输出移位寄存器

如果串入串出移位寄存器与串入串出移位寄存器如此相似,为什么制造商要费心提供这两种类型?

为什么不直接提供串行输入并行输出的移位寄存器?

答案是他们实际上只提供串行输入并行输出的移位寄存器,只要不超过8位即可。

请注意,串行输入、串行输出移位寄存器的长度大于 8 位,为 18 至 64 位。

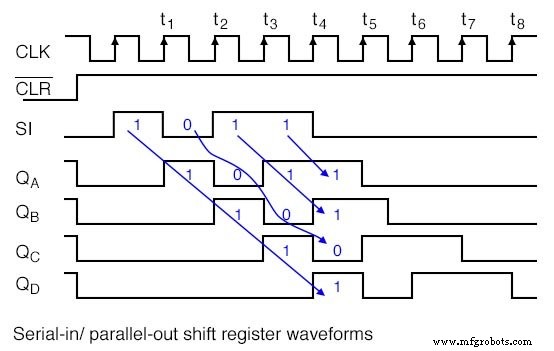

提供需要那么多输出引脚的 64 位串行输入并行输出移位寄存器是不切实际的。以上移位寄存器波形见下图。

CLR' 在任何数据之前清除移位寄存器 , 低电平有效信号,清除移位寄存器内的所有 D 型触发器。

注意串行数据 1011 在 SI 上呈现的模式 输入。此数据与时钟 CLK 同步 .

如果它从另一个移位寄存器之类的东西移入,例如并行输入串行输出移位寄存器(此处未显示),就会出现这种情况。

在 t1 的第一个时钟 , 数据 1 在 SI 从 D 转移 问 第一级移位寄存器。 t2 之后 第一个数据位位于 QB .

t3 之后 它在 QC . t4 之后 它位于 QD .四个时钟脉冲已将第一个数据位一直移动到最后一级 QD .

第二个数据位 a 0 在质量控制 在第 4 个时钟之后。第三个数据位 a 1 在 QB .第四个数据位又1 正在质量检查 .

因此,串行数据输入模式1011 包含在 (QD QC QB QA )。它现在可用于四个输出。

它将在时钟 t4 之后的四个输出上可用 到 t5 之前 .

此并行数据必须在这两次之间使用或存储,否则会因在随后的时钟 t5 移出 QD 阶段而丢失 到 t8 如上图。

串行输入、并行输出设备

让我们仔细看看由 Texas Instruments 提供的可用作集成电路的串行输入、并行输出移位寄存器。

如需完整的器件数据表,请点击链接。

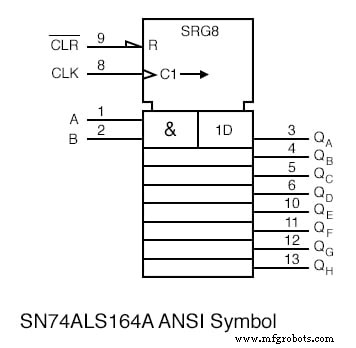

- SN74ALS164A 串行输入/并行输出 8 位移位寄存器

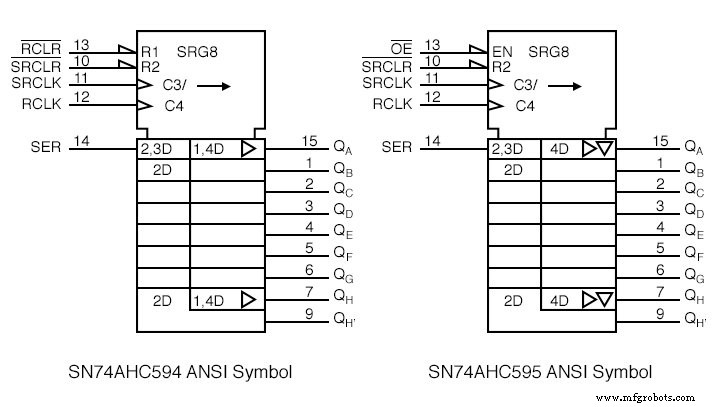

- SN74AHC594 串行输入/并行输出 8 位移位寄存器,带输出寄存器

- SN74AHC595 串行输入/并行输出 8 位移位寄存器带输出寄存器

- CD4094 串行输入/并行输出 8 位移位寄存器带输出寄存器

除了两个串行输入 A 之外,74ALS164A 几乎与我们之前的图表相同 和 B .

未使用的输入应被拉高以启用另一个输入。我们不会显示以上所有阶段。

但是,所有输出都显示在下面的 ANSI 符号上,以及引脚编号。

时钟 上述ANSI符号的控制部分的输入有两个内部函数C1 , 控制前缀为 1 的任何东西 .

这将是 1D 的数据计时 .第二个功能,斜线(/)后面的箭头是移位寄存器内数据的右(下)移。

八个输出位于控制部分下方八个寄存器的右侧。第一阶段比其他阶段更宽以容纳 A&B 输入。

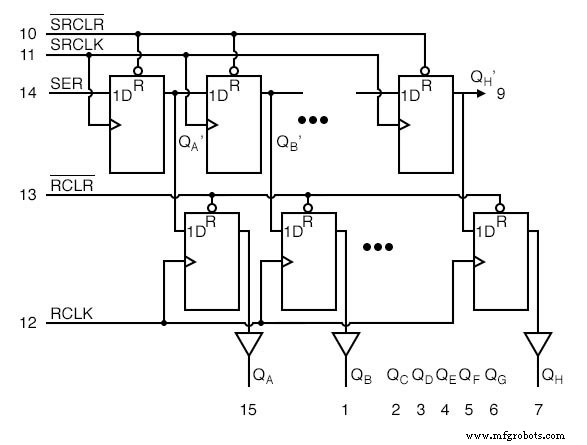

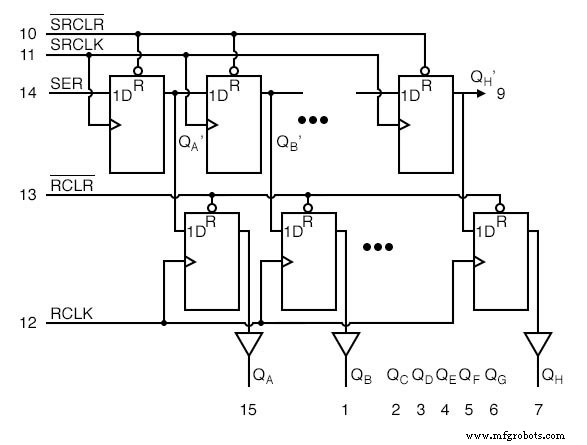

上述内部逻辑图改编自 TI(德州仪器)的 74AHC594 数据表。顶行的“D”型FF由一个串行输入并行输出移位寄存器组成。

本部分的工作方式与前面描述的设备类似。输出 (QA’ QB’ QH' ) 设备的移位寄存器一半并行馈送下半部分的“D”型 FF。 QH' (引脚 9)移出到任何可选的级联器件封装。

RCLK 的单个正时钟沿将传输来自 D 的数据 问 较低的 FF。所有 8 位并行传输到输出寄存器 (存储元素的集合)。

输出寄存器的目的是在新数据被移入上移位寄存器部分时保持恒定的数据输出。

如果输出驱动继电器、阀门、电机、螺线管、喇叭或蜂鸣器,则这是必要的。驱动 LED 时可能不需要此功能,只要在换档过程中闪烁不成问题即可。

请注意,74AHC594 具有单独的移位寄存器时钟(SRCLK ) 和输出寄存器 ( RCLK )。此外,移位器可能会被 SRCLR 清零 并且,输出寄存器由 RCLR .

最好在上电时将输出置于已知状态,特别是在驱动继电器、电机等时。以下波形说明了数据的移位和锁存。

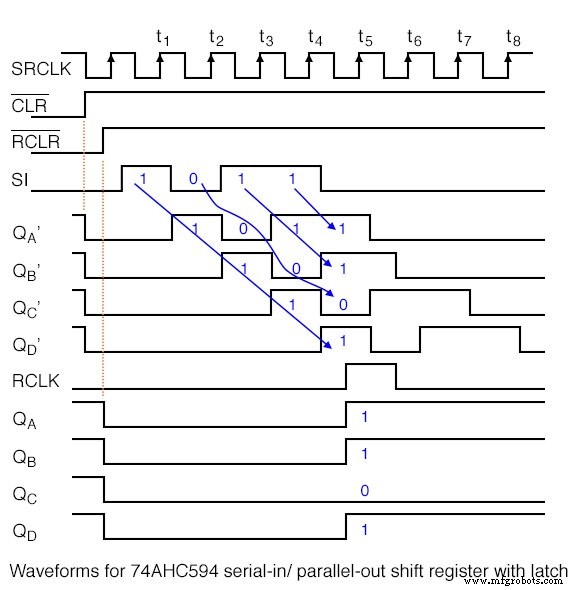

以上波形为4位数据移位到74AHC594的前四级,然后并行传输到输出寄存器。

实际上,74AHC594是一个8位移位寄存器,8位数据移位需要8个时钟周期,这是正常的工作模式。

然而,我们展示的 4 位节省了空间并充分说明了操作。

我们在 t0 前半个时钟清除移位寄存器 SRCLR'=0 . SRCLR' 必须在转换前释放回高位。

就在 t0 之前 RCLR'=0 清除输出寄存器 .它也已发布 ( RCLR'=1 ).

串行数据 1011 出现在时钟之间的 SI 引脚 t0 和 t4 .它由时钟移入 t1 t2 t3 t4 出现在内部换档阶段 QA' QB' QC' QD' .

此数据存在于 t4 之间的这些阶段 和 t5 . t5 之后 所需的数据 (1011 ) 在这些内部移位器阶段将不可用。

t4 之间 和 t5 我们应用积极的RCLK 传输数据1011 注册输出 QA QB QC QD .

此数据将在此处冻结,因为更多数据 (0 s) 在随后的 SRCLK 期间移入 s (t5 到 t8 )。直到另一个RCLK,这里的数据不会发生变化 已应用。

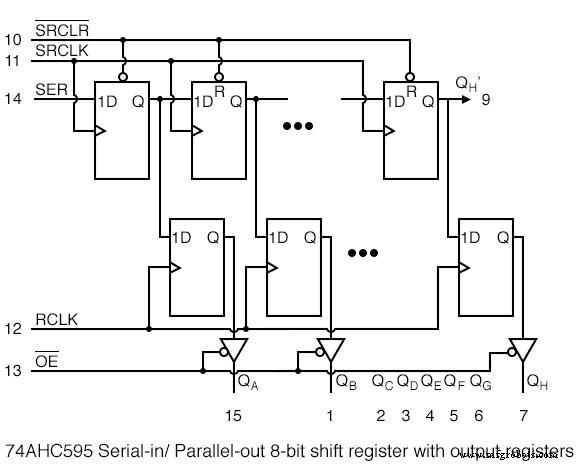

74AHC595 与‘594 相同,除了RCLR 替换为 OE’ 在 8 个输出寄存器位中的每一个的输出端启用一个三态缓冲器。

虽然输出寄存器不能被清除,但输出可能被OE'=1断开 .

这将允许外部上拉或下拉电阻器在系统上电期间强制任何继电器、螺线管或阀门驱动器进入已知状态。

一旦系统通电,比如说,微处理器已经将数据移入并锁存到‘595’中,输出使能可以被断言(OE’=0 ) 以驱动具有有效数据的继电器、螺线管和阀门,但不能在此之前。

以上是为这些设备建议的 ANSI 符号。 C3 时钟数据进入串行输入(外部SER ) 如 3 所示 2,3D 的前缀 .

C3/ 后面的箭头 表示移位寄存器右移(下),控制部分下方'595符号左边的8级。

2 2,3D 的前缀 和 2D 表示这些阶段可以由 R2 重置 (外部 SRCLR' ).

1 1,4D 的前缀 在 '594 表示 R1 (外部RCLR' ) 可能会重置输出寄存器,该寄存器位于移位寄存器部分的右侧。

‘595 , 其中有一个 EN 在外部OE’ 不能复位输出寄存器。但是,EN 启用三态(倒三角形)输出缓冲器。

‘594 的右指三角形 和‘595 表示内部缓冲。 '594 和‘595 输出寄存器由 C4 计时,如 4 所示 1,4D 和 4D 分别。

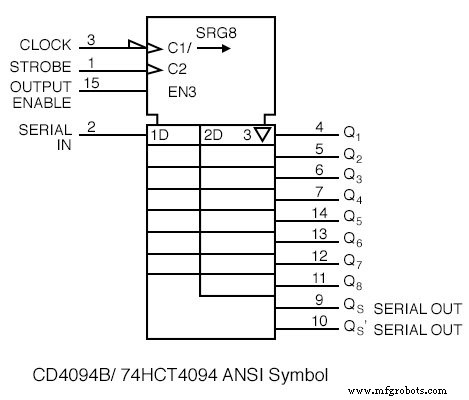

CD4094B 是一款 3 至 15VDC 的锁存移位寄存器,可替代之前的 74AHC594 器件。

时钟 , C 1、将数据移入SERIAL IN 正如 1 所暗示的那样 1D 的前缀 .

它也是C1的/(右箭头)所指示的右移位寄存器(符号体的左半部分)的时钟 /(箭头)在 CLOCK 输入。

频闪 , C2 是符号主体右侧的 8 位输出寄存器的时钟。 2 二维 表示 C2 是输出寄存器的时钟。

输出锁存器中的倒三角形表示输出为三态,由EN3使能 .

3 在倒三角形和 3 之前 EN3 经常被省略,因为任何启用 (EN ) 被理解为控制三态输出。 质量 和 QS' 是移位寄存器级的非锁存输出。

质量 可以级联到SERIAL IN 后继设备。

实际应用

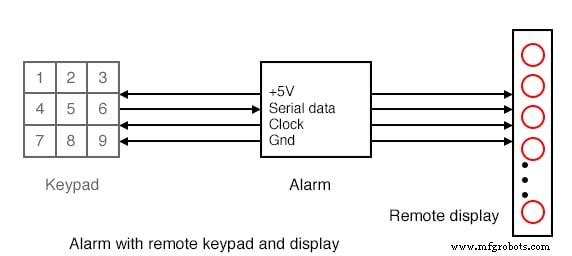

串行输入并行输出移位寄存器的实际应用是将数据从微处理器输出到远程面板指示器。

或者,另一个接受串行格式数据的远程输出设备。

此处从并行输入串行输出部分重复了“远程键盘报警”图,并添加了远程显示器。

因此,我们可以显示,例如,连接到主报警箱的报警回路的状态。

如果报警器检测到一个打开的窗口,它可以发送串行数据到远程显示器让我们知道。

键盘和显示器都可能包含在同一个远程外壳内,与主报警箱分开。不过,本节我们只看显示面板。

如果显示器与警报器在同一块板上,我们只需将八根电线连接到八个 LED,以及两根电线用于电源和接地。

从长远来看,这八根电线对于远程面板来说不太理想。使用移位寄存器,我们只需要运行五根线——时钟、串行数据、一个选通、电源和地。

如果面板距离主板只有几英寸,那么减少连接电缆中的电线数量以提高可靠性可能仍然是可取的。

此外,我们有时会用完微处理器上的大部分可用引脚,需要使用串行技术来扩展输出数量。

一些集成电路输出设备,如数模转换器,包含串行输入、并行输出的移位寄存器,用于从微处理器接收数据。

此处说明的技术适用于这些部分。

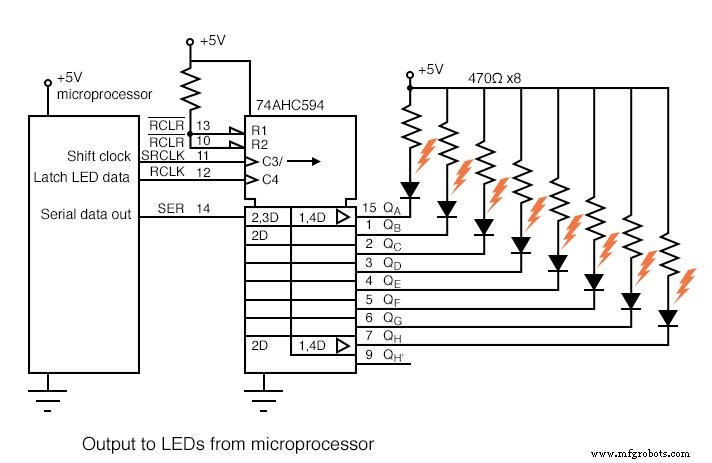

我们选用了74AHC594的串入、并出移位寄存器,带输出寄存器;但是,它需要一个额外的引脚,RCLK , 将移入的数据并行加载到输出引脚。

当数据移入时,这个额外的引脚可防止输出发生变化。这对 LED 来说不是什么大问题。但是,如果驱动继电器、阀门、电机等,就会有问题。

在微处理器内执行的代码将从要输出的 8 位数据开始。一位将在“串行数据输出”引脚上输出,驱动 SER 远程74AHC594。

接下来,微处理器在“移位时钟”上产生一个从低到高的转换,驱动 SRCLK '595 移位寄存器。

此正时钟将 SER 处的数据位移位 从第一级移位寄存器的“D”到“Q”。

这对 QA 没有影响 由于移位寄存器和输出引脚之间的内部 8 位输出寄存器(QA QH ).

最后,“移位时钟”被微处理器拉回低电平。这样就完成了一位向‘595’的移位。

再重复上述过程7次,完成8位数据从微处理器移入74AHC594串行输入并行输出移位寄存器。

要将内部‘595 移位寄存器中的 8 位数据传输到输出,需要微处理器在 RCLK 上产生一个从低到高的转换 , 输出寄存器时钟。

这将新数据应用于 LED。 RCLK 需要拉低以期待下一次 8 位数据传输。

'595 输出端的数据将保留,直到对新的 8 位数据重复上述两段中的过程。

特别是,新数据可以移入‘595 内部移位寄存器,而不会影响 LED。 LED 只会在应用 RCLK 时使用新数据更新 上升沿。

如果我们需要驱动八个以上的 LED 怎么办?只需级联另一个 74AHC594 SER 固定到 QH' 现有移位器。

并行SRCLK 和 RCLK 针脚。在生成 RCLK 之前,微处理器需要以 16 时钟传输 16 位数据 喂两个设备。

我们展示的离散 LED 指示灯可以是 7 段 LED。不过,也有能够驱动多个 7 段数字的 LSI(大规模集成)设备。

该器件以串行格式接受来自微处理器的数据,通过复用 LED 驱动比引脚数更多的 LED 段。

相关工作表:

- 移位寄存器工作表

工业技术