移位寄存器简介

移位寄存器与计数器一样,是一种顺序逻辑 .

与组合逻辑不同,顺序逻辑不仅受当前输入的影响,还受先前历史的影响。

换句话说,时序逻辑会记住过去的事件。

移位寄存器产生数字信号或波形的离散延迟。

与时钟同步的波形 ,一个重复的方波,延迟 “n” 离散时钟时间,其中 “n” 是移位寄存器级数。

因此,四级移位寄存器将“数据输入”延迟四个时钟到“数据输出”。

移位寄存器中的级是延迟级 , 通常键入 “D” 人字拖或输入 “JK” 人字拖。

以前,很长的(数百级)移位寄存器用作数字存储器。

这个过时的应用程序让人想起用作早期计算机内存的声学汞延迟线。

串行数据传输,在米到千米的距离内,使用移位寄存器将并行数据转换为串行形式。

串行数据通信用单个串行高速电路代替了许多慢速并行数据线。

数十厘米的短距离串行数据,使用移位寄存器将数据输入和输出微处理器。

许多外围设备,包括模数转换器、数模转换器、显示驱动器和存储器,都使用移位寄存器来减少电路板上的布线量。

一些专门的计数器电路实际上使用移位寄存器来产生重复波形。

更长的移位寄存器,在反馈的帮助下,生成的模式看起来像随机噪声,伪噪声 .

基本移位寄存器按结构分为以下几类:

- 串行输入/串行输出

- 并行输入/串行输出

- 串行输入/并行输出

- 通用并行输入/并行输出

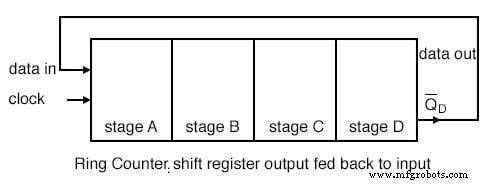

- 环形计数器

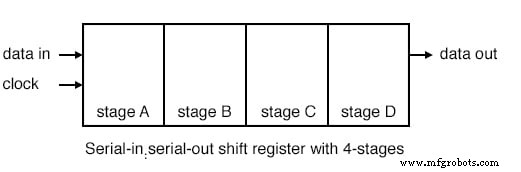

上图是一个串行输入/串行输出移位寄存器的框图,长度为4级。

输入端的数据从输入端到移位寄存器的输出端会延迟四个时钟周期。

上面“数据输入”中的数据将出现在阶段 A 在第一个时钟脉冲后输出。在第二个脉冲阶段A之后 数据传输到阶段B 输出,并且“数据输入”被传输到阶段A 输出。在第三个时钟之后,阶段 C 被阶段 B 取代;阶段 B 被阶段 A 取代;阶段A被“数据输入”替换。

在第四个时钟之后,原本出现在“data in”的数据处于阶段D , “输出”。

“先进”数据是“先出”,因为它从“数据输入”转移到“数据输出”。

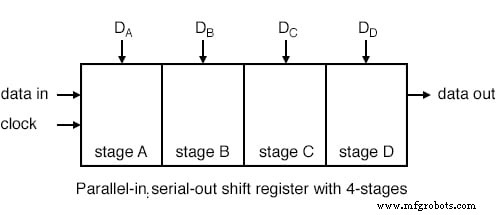

数据同时加载到并行输入/串行输出移位寄存器的所有阶段。

然后通过时钟脉冲通过“数据输出”将数据移出。由于上图显示的是一个四级移位寄存器,因此需要四个时钟脉冲才能将所有数据移出。

在上图中,阶段 D 数据将出现在“数据输出”处,直到第一个时钟脉冲;阶段 C 数据将出现在第一个时钟和第二个时钟脉冲之间的“数据输出”处;阶段 B 数据将出现在第二个时钟和第三个时钟之间;和阶段 A 数据将出现在第三个和第四个时钟之间。

在第四个时钟脉冲之后,延迟四个时钟脉冲后,移位寄存器的“数据输出”处应出现连续的“数据输入”位。

如果四个开关通过DD连接到DA,则可以仅使用一个数据引脚和一个时钟引脚将状态读入微处理器。

由于添加更多开关不需要额外的引脚,因此这种方法对于许多输入来说看起来很有吸引力。

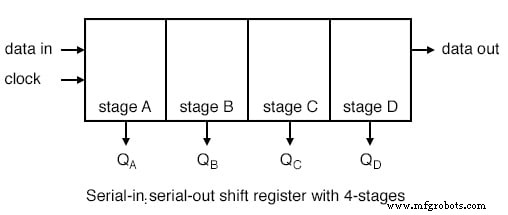

上面,四个数据位将通过四个时钟脉冲从“数据输入”移入,并在 QA 到 QD 处可用,用于驱动 LED、灯、继电器驱动器和喇叭等外部电路。在第一个时钟之后,“data in”处的数据出现在 QA 处。

第二个时钟后,旧的QA数据出现在QB处; QA 从“数据输入”接收下一个数据。第三个时钟后,QB数据在QC。

在第四个时钟之后,QC 数据在 QD。此阶段包含首先出现在“数据输入”处的数据。移位寄存器现在应该包含四个数据位。

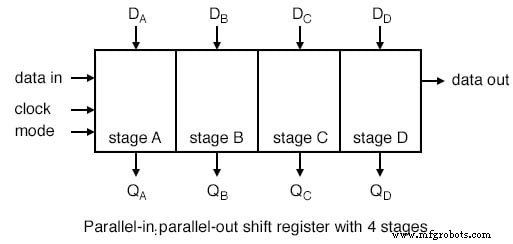

并入/并出移位寄存器将并入、串行出移位寄存器的功能与串入、并出移位寄存器的功能相结合,形成通用移位寄存器。

“无所不能”的移位器是有代价的——I/O(输入/输出)引脚数量的增加可能会减少可以封装的级数。

DA 到 DD 的数据被并行加载到寄存器中。

QA 到 QD 的数据可能会偏移时钟输入端的脉冲数。

移位后的数据可在 QA 到 QD 处获得。

“模式”输入,可以是多个输入,控制从DA到DD的数据并行加载、数据移位和移位方向。

有向左或向右移位数据的移位寄存器。

如果移位寄存器的串行输出连接到串行输入,只要存在时钟脉冲,数据就可以永久地围绕环移动。

如果输出如上图所示在反馈前被反转,我们就不用担心将初始数据加载到“环形计数器”中。

相关工作表:

- 移位寄存器工作表

工业技术