在本文中,我们将研究一个 Verilog 模块的基本结构,看一些使用 Verilog “wire”数据类型及其向量形式,并简要介绍 VHDL 和 Verilog 之间的一些差异。 在本文中,我们将研究一个 Verilog 模块的基本结构,看一些使用 Verilog “wire”数据类型及其向量形式的例子,并简要介绍 VHDL 和 Verilog 之间的一些区别。 Verilog 和 VHDL 是两种常用来描述数字电路的语言。 AAC 有一系列技术文章讨论 VHDL 的基本概念。本文是我们关于 Verilog 的系列文章的起点。 我需要 Verilog 和 VHDL 吗? 在开始我们的讨论

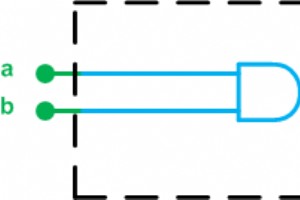

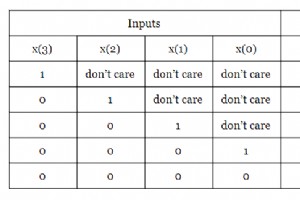

Steve Arar 博士于 2019 年 1 月 6 日 本文通过研究如何使用条件运算符来描述组合真值表,介绍了在 Verilog 中描述组合电路的技术。 本文通过研究如何使用条件运算符来描述组合真值表,介绍了在 Verilog 中描述组合电路的技术。它还展示了如何利用 Verilog 的“always”块来描述组合电路——“always”块可以为我们提供更简单的解决方案来描述数字电路。 在上一篇文章中,我们讨论了使用 Verilog “assign”关键字来执行连续赋值。此类分配始终处于活动状态,可用于获取数字电路的门级描述。例如,在以下描述与门的代码中,会不断评估右

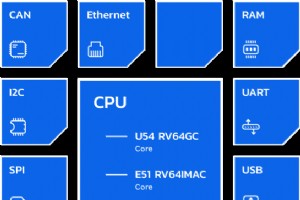

在本文中,我们将解释如何使用像 Antmicro 的 Renode 这样的开源功能模拟器可以成为软硬件协同设计工作的一个组成部分. 在本文中,我们将解释如何使用像 Antmicro 的 Renode 这样的开源功能模拟器可以成为软硬件协同设计工作的一个组成部分。 据 Semico Research 称,随着市场对其嵌入式系统的要求越来越高,下一代 SoC 变得越来越复杂,导致设计周期延长和成本上升。 对于设备制造商来说,令人沮丧的现实是,提供客户要求的新的和创新的功能、更高的安全性和更好的性能的唯一方法是参与“全栈”协同设计、不断发展的硬件、固件、运行时(OS) 和开发工具链协同工作。这

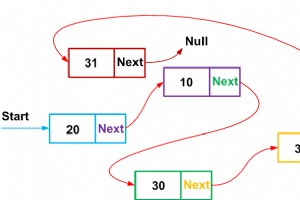

介绍完结构之后,我们将看看这个强大的数据对象的一些重要应用。然后,我们将检查 C 语言语法来声明一个结构。最后,我们将简要介绍数据对齐要求。我们将看到,我们可以通过简单地重新排列其成员的顺序来减小结构的大小。 本文提供了有关嵌入式 C 编程中结构的一些基本信息。 介绍完结构之后,我们将看看这个强大的数据对象的一些重要应用。然后,我们将检查 C 语言语法来声明一个结构。最后,我们将简要介绍数据对齐要求。我们将看到,我们可以通过简单地重新排列其成员的顺序来减小结构的大小。 结构 可以将多个在逻辑上相互关联的相同类型的变量分组为一个数组。处理一组而不是一组自变量使我们能够更方便地排列数据并

EE 在日常工作中可以在哪里使用 Python?下面来看看 Python 擅长的应用。 EE 日常可以在哪里使用 Python?下面来看看 Python 擅长的应用。 在上一篇文章中,我们提出了一个问题“为什么工程师还要费心学习 Python?” 现在,让我们讨论 Python 如何与电气工程师的工作相关。 瑞士军刀工程师 EE 不仅仅处理电路设计。我们还面临着许多必须处理的其他任务。有固件编程、调试、测试原型硬件和软件、测试生产样品、进行质量控制,以及看似永无止境的大量数据收集、评估和分析。 Python 如何帮助解决这一切? 进入瑞士军刀语言 Python P

了解嵌入式 C 语言中称为联合的数据对象。 了解嵌入式 C 语言中称为联合的数据对象。 嵌入式C中结构和联合的区别 在本系列的前一篇文章中,我们讨论了嵌入式 C 中的结构允许我们将不同数据类型的变量分组,并将它们作为单个数据对象进行处理。 除了结构之外,C 语言还支持另一种数据结构,称为联合,可以将不同的数据类型分组为单个数据对象。本文将提供有关工会的一些基本信息。我们将首先看一个声明联合的介绍性示例,然后我们将研究该数据对象的一个重要应用。 介绍性示例 声明联合很像声明结构。我们只需要将关键字“struct”替换为“union”即可。考虑以下示例代码: union test

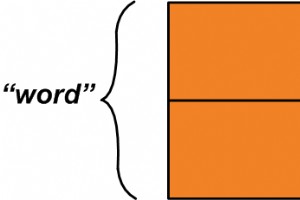

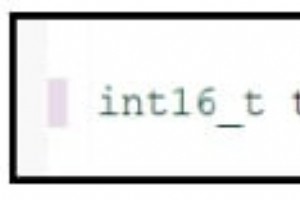

了解如何使用 C 语言中的联合打包和解包数据。 了解如何在 C 语言中使用联合打包和解包数据。 在上一篇文章中,我们讨论了联合的最初应用一直在为互斥变量创建共享内存区域。然而,随着时间的推移,程序员已经广泛地将联合用于一个完全不同的应用程序:从一个更大的数据对象中提取更小的数据部分。在本文中,我们将更详细地研究联合的这种特殊应用。 使用联合来打包/解包数据 联合的成员存储在共享内存区域中。这是使我们能够找到有趣的工会应用程序的关键功能。 考虑下面的联合: union { uint16_t 字;结构 { uint8_t 字节 1; uint8_t 字节 2; };} u1; 这个

本文展示了如何使用文本文件中的值在 C 程序中初始化数组。 本文展示了如何使用文本文件中的值在 C 程序中初始化数组。数据不存储在源文件中。在编译程序时读取文件。考虑一维和多维数组。示例还展示了如何控制将数组放入 RAM 或非易失性存储器中以及选择用于初始化的数据文件。 示例中使用的编译器是 GCC for ARM,以 32 位微控制器为目标。所有示例均使用标准 C 语言并使用此编译器。 初始化数组的基础 数组可以在“声明”时使用值进行初始化。此处显示了一个典型的声明。花括号内的值称为“初始化器”。 如果括号内未指定数组的大小,则大小将为初始值设定项的数量。如果初始值设定项

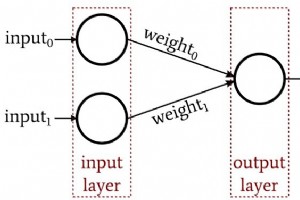

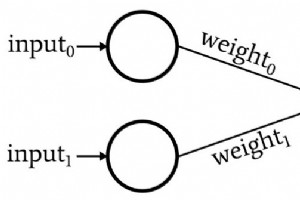

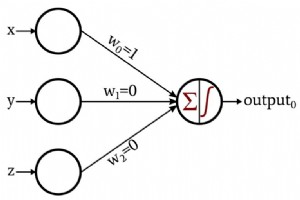

本文探讨了著名神经网络拓扑的基本理论和结构。 这是一系列文章中的第一篇,详细介绍了神经网络的设计、训练和评估。目标是使用 Python 计算机程序执行复杂的分类,该程序实现了称为多层感知器的神经网络架构。 为方便起见,您可以在此处找到感知器系列的其余部分: 如何使用神经网络进行分类:什么是感知器? 如何使用简单的感知器神经网络示例对数据进行分类 如何训练基本的感知器神经网络 了解简单的神经网络训练 神经网络训练理论简介 了解神经网络中的学习率 使用多层感知器进行高级机器学习 Sigmoid 激活函数:多层感知器神经网络中的激活 如何训练多层感知器神经网络 了解多层感知器的训练公式和反向

本文演示了感知器神经网络的基本功能并解释了训练的目的。 本文是感知器神经网络系列文章的一部分。 如果您想从头开始或继续前进,可以在此处查看其他文章: 如何使用神经网络进行分类:什么是感知器? 如何使用简单的感知器神经网络示例对数据进行分类 如何训练基本的感知器神经网络 了解简单的神经网络训练 神经网络训练理论简介 了解神经网络中的学习率 使用多层感知器进行高级机器学习 Sigmoid 激活函数:多层感知器神经网络中的激活 如何训练多层感知器神经网络 了解多层感知器的训练公式和反向传播 Python 实现的神经网络架构 如何在 Python 中创建多层感知器神经网络 使用神经网络进行信号处

本文介绍了 Python 代码,可让您为简单的神经网络自动生成权重。 欢迎来到 AAC 的感知器神经网络系列。如果您希望从头开始了解背景知识或继续前进,请查看此处的其余文章: 如何使用神经网络进行分类:什么是感知器? 如何使用简单的感知器神经网络示例对数据进行分类 如何训练基本的感知器神经网络 了解简单的神经网络训练 神经网络训练理论简介 了解神经网络中的学习率 使用多层感知器进行高级机器学习 Sigmoid 激活函数:多层感知器神经网络中的激活 如何训练多层感知器神经网络 了解多层感知器的训练公式和反向传播 Python 实现的神经网络架构 如何在 Python 中创建多层感知器神经网络

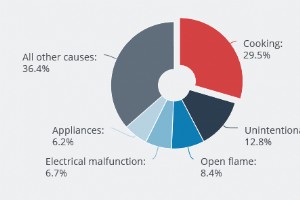

本文探讨了 IEC 60730 B 类功能安全标准,以解决电器中的机械和电气设计问题。了解标准的含义以及帮助满足这些标准的控制者。 许多电器简化了家中的日常或定期活动,并帮助用户始终如一地以最小的压力执行这些活动。当他们正常工作时,他们很棒。然而,如果发生故障,一些电器会变得非常不安全,并导致包括火灾在内的重大问题。 为确保电器设计安全,国际电工委员会 (IEC) 制定了 IEC 60730 B 级功能安全标准,以解决美国保险商实验室也已批准的机械和电气设计。为炉灶和炉灶面以及洗衣设备等提供更安全的用户体验,新设计的触摸屏集成电路 (IC) 具有内置功能安全性,已通过认证符合该标准。

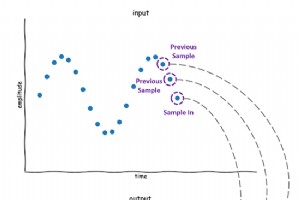

了解在时域中过滤和处理数据样本的广泛使用的方法,同时仔细查看 PowerQuad 单元的 Dual Biquad IIR 引擎在 LPC55S69 MCU 中。 在处理随时间或在时域中收集的数据样本时,最基本的操作之一是“过滤”数据。重要的是要了解可以对数据进行数字过滤以获得最佳结果并释放 CPU 以执行其他任务的常用方法,尤其是在涉及嵌入式微控制器时。 在本文中,了解在时域中过滤和处理数据样本的广泛使用的方法。此外,请仔细查看 LPC55S69 MCU 中 PowerQuad 单元的 Dual Biquad IIR 引擎 — 一种可用于许多过滤用例的多功能 DSP 构建块。 连

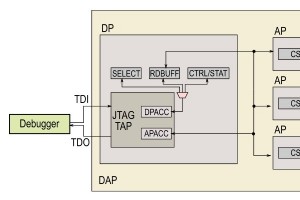

这篇文章将教你JTAG和Arm核心设备之间的交叉,特别关注Arm调试接口或ADI。 到目前为止,在我们关于 JTAG 的系列中,我们已经研究了 IEEE 1149.1 标准,包括测试访问端口 (TAP) 控制器和 TAP 状态机。然后我们回顾了可用于 JTAG 的不同物理接口,包括连接器的常见引脚分配,以及市场上可用的 JTAG 接口和调试探针。 在本文中,我们将稍微偏离 JTAG 标准,而是看看 JTAG 如何在无处不在的 ARM 核心设备中实现。 什么是手臂? Arm 指的是处理器架构,以及大量与微处理器和微控制器接口相关的知识产权。消费类 PC 倾向于使用 x86 派生处理器

本文研究了变换引擎,PowerQuad 的另一部分,它使 LPC55S69 MCU 能够计算快速傅立叶变换 (FFT)。 NXP 的 LPC55S69 微控制器包含许多特性,使其适用于各种应用。 LPC55S69 MCU 及其 PowerQuad 单元包括独特的组件 — Biquad 和转换引擎 — 用于完成各种任务,让主 CPU 内核空闲用于其他事情。 上一篇文章“使用嵌入式微控制器了解数字滤波”探讨了各种广泛使用的时域数据样本滤波和处理方法。为此,它利用了 LPC55S69 的 PowerQuad 单元的 Biquad 引擎。 本文研究了 PowerQuad 的另一部分变换引擎,

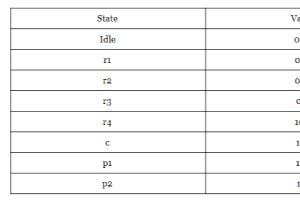

本文比较了使用二进制、格雷和单热编码在 FPGA 中实现状态机的实现。这些编码通常由综合和实现工具评估和应用,因此了解软件做出这些决定的原因很重要。 有限状态机 (FSM) 是几乎所有数字系统中非常常见的部分。这就是为什么综合工具经常检查您的代码以检测 FSM 并执行可能修改状态编码的优化。如果您在源代码中仔细选择并指定了实现您的状态的值并不重要,综合工具可能会用其他值替换这些值,这些值甚至可能与您的原始编码具有不同的位长。 如果你想复习在 Verilog 中实现状态机,你应该阅读我的文章,标题为在 Verilog 中创建有限状态机。 状态编码:Gray vs. Binary vs.

遵循三个实验,这些实验展示了确定哪种编码适合给定 FPGA 的过程。 我的 FPGA 应该使用哪种编码类型?正如我在上一篇文章中所讨论的,编译器通常会为您做出决定——我建议您遵循编译器的决定。 然而,了解编码类型之间的差异以及编译器可能得出某个结论的原因很重要。考虑到这一点,本文将引导您完成一个实验,该实验展示了一个示例 FPGA 应用程序,并逐步讨论哪种编码类型最好。 到目前为止,在本系列中,我们讨论了如何使用 Verilog 创建有限状态机 (FSM)、初始状态以及内存如何影响 FPGA 编码,以及比较二进制编码与单热编码与格雷编码的高级概述. 被测系统 对于这个实验,我想多次

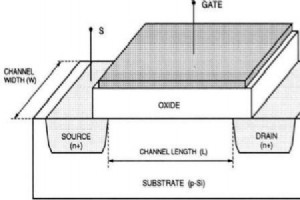

本文介绍了 MOS 晶体管的基础知识,以期更好地了解此类晶体管中可能出现的漏电流。 MOS 晶体管正在按比例缩小,以最大限度地提高集成电路内部的封装密度。这导致氧化物厚度的减少,进而降低了 MOS 器件的阈值电压。在较低的阈值电压下,漏电流变得很重要,并且会导致功耗。这就是为什么了解 MOS 晶体管中各种类型的漏电流至关重要。 在我们尝试了解各种漏电流组件之前,让我们先回顾一下 MOS 晶体管核心概念。这将有助于我们更好地了解该主题。 再谈 MOS 晶体管结构 MOS晶体管结构由金属、氧化物和半导体结构(因此,MOS)组成。 考虑具有 p 衬底和 n+ 扩散阱作为漏极和源极端子的

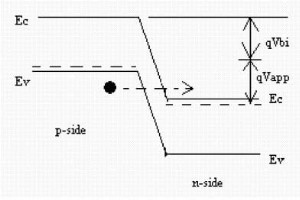

漏电流会导致功耗,尤其是在较低的阈值电压下。了解 MOS 晶体管中的六种漏电流。 在讨论MOS晶体管时,短沟道器件中的漏电流成分基本上有六种: 反向偏置-pn结漏电流 亚阈值漏电流 漏极引起的屏障降低 Vth 滚降 工作温度的影响 隧道进入和穿过栅极氧化物漏电流 由于热载流子从衬底注入栅极氧化物导致的漏电流 栅极感应漏极降低 (GIDL) 导致的漏电流 在继续之前,请确保您熟悉 MOS 晶体管的基本概念,这将为您准备以下信息。 1.反向偏置 pn 结漏电流 MOS 晶体管中的漏极/源极和衬底结在晶体管工作期间被反向偏置。这会导致器件中的反向偏置漏电流。这种漏电流可能是由于反向

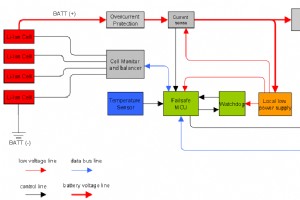

了解有关电池管理系统 (BMS) 在电源设计中所起的作用以及其基本功能需要哪些组件的高级基础知识。 如今,锂离子电池占据主导地位,能量密度高达 265 Wh/kg。然而,他们确实有名声,如果他们承受过度的压力,偶尔会爆发和燃烧所有的能量。这就是为什么他们经常需要电池管理系统 (BMS) 来控制它们。 在本文中,我们将讨论 BMS 概念的基础知识,并介绍构成典型 BMS 的几个基础部分。 BMS 基本配置 在图 1 中,我们看到了 BMS 在提供防止主要电池故障的功能时的外观基本块。 图 1。 一个典型的BMS框图 这个示例 BMS 可以处理四个串联的锂离子电池。电池监

嵌入式