内存处理器芯片加速 AI 计算

Imec 和 GlobalFoundries 已经展示了一种内存处理器芯片,可以实现高达 2900 TOPS/W 的能效,比当今商用内存处理器芯片高出大约两个数量级。该芯片采用了一种既定的想法,即模拟计算,在 GlobalFoundries 的 22 纳米全耗尽绝缘体上硅 (FD-SOI) 工艺技术中在 SRAM 中实现。 Imec 的模拟内存计算 (AiMC) 将作为一项可在公司的 22FDX 平台上实施的功能提供给 GlobalFoundries 客户。

Imec 的 AnIA 测试芯片,如图所示安装在用于测量和表征的 PCB 上,可实现高达 2900 TOPS/W(图片:Imec)

模拟计算

模拟计算或内存处理器是一种成熟的技术,已被用于 Mythic、Syntiant、Gyrfalcon 等初创公司的商业 AI 加速器芯片中。

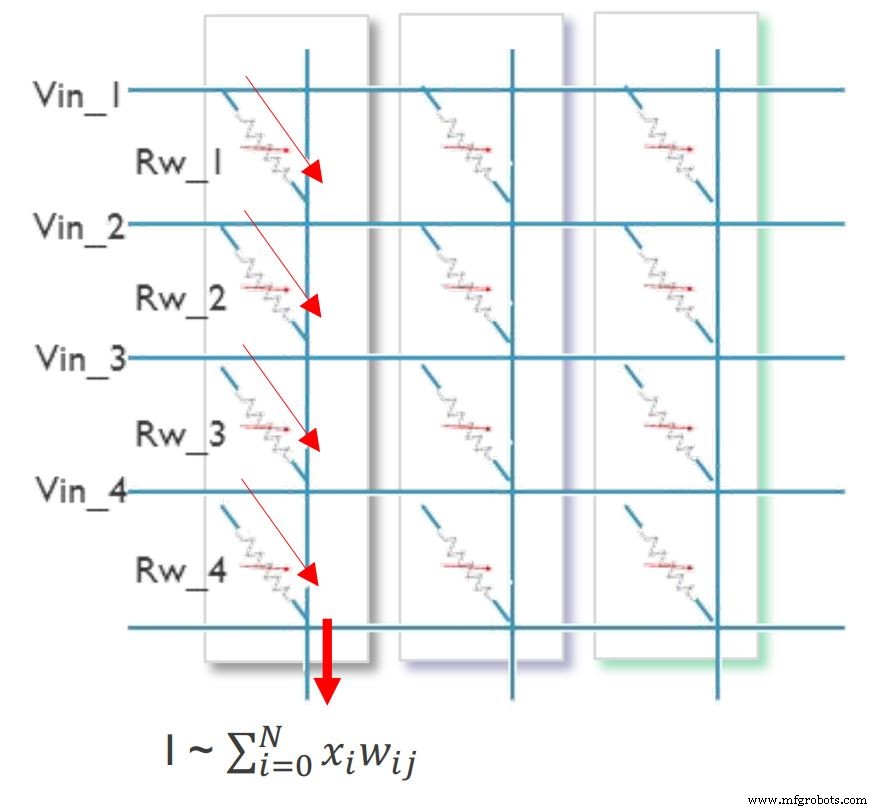

由于神经网络模型可能有数千万或数亿个权重,因此在内存和处理器之间来回发送数据是低效的。模拟计算使用内存阵列来存储权重并执行乘法累加 (MAC) 运算,因此不需要内存到处理器的传输。每个忆阻器元件(可能是 ReRAM 单元)的电导被编程为与所需重量成正比的模拟电平。

施加与输入激活成正比的电压(通过数模转换 - 在下图的左侧)意味着通过每个元件的电流与激活和重量的乘积成正比。通过每条垂直位线(下图中的垂直线)的电流是这些激活权重乘积的总和,可以通过模数转换器馈送。这个激活权重积的总和对神经网络算法的计算至关重要。

模拟计算使用一组忆阻器单元来计算矩阵向量乘法,而无需在内存和处理器之间发送数据(图片:Imec)

“在实践中,除了 ReRAM 之外,还有许多选择——我们可以使用 MRAM、闪存、DRAM……该计划的目的是了解哪种最适合应用程序并优化每个应用程序域的选项,”计划的 Diederik Verkest 解释说Imec 机器学习总监。

测试芯片

Imec 基于 GlobalFoundries 的 22nm FD-SOI 工艺构建了一个名为模拟推理加速器 (AnIA) 的测试芯片。 AnIA 的 512k SRAM 单元阵列以及包括 1024 个 DAC 和 512 个 ADC 在内的数字基础设施占用 4mm 2 .它可以执行大约五十万

Ioannis Papistas(图片:Imec)

每个操作周期的计算基于 6 位(加号位)输入激活、三元权重(-1、0、+1)和 6 位输出。

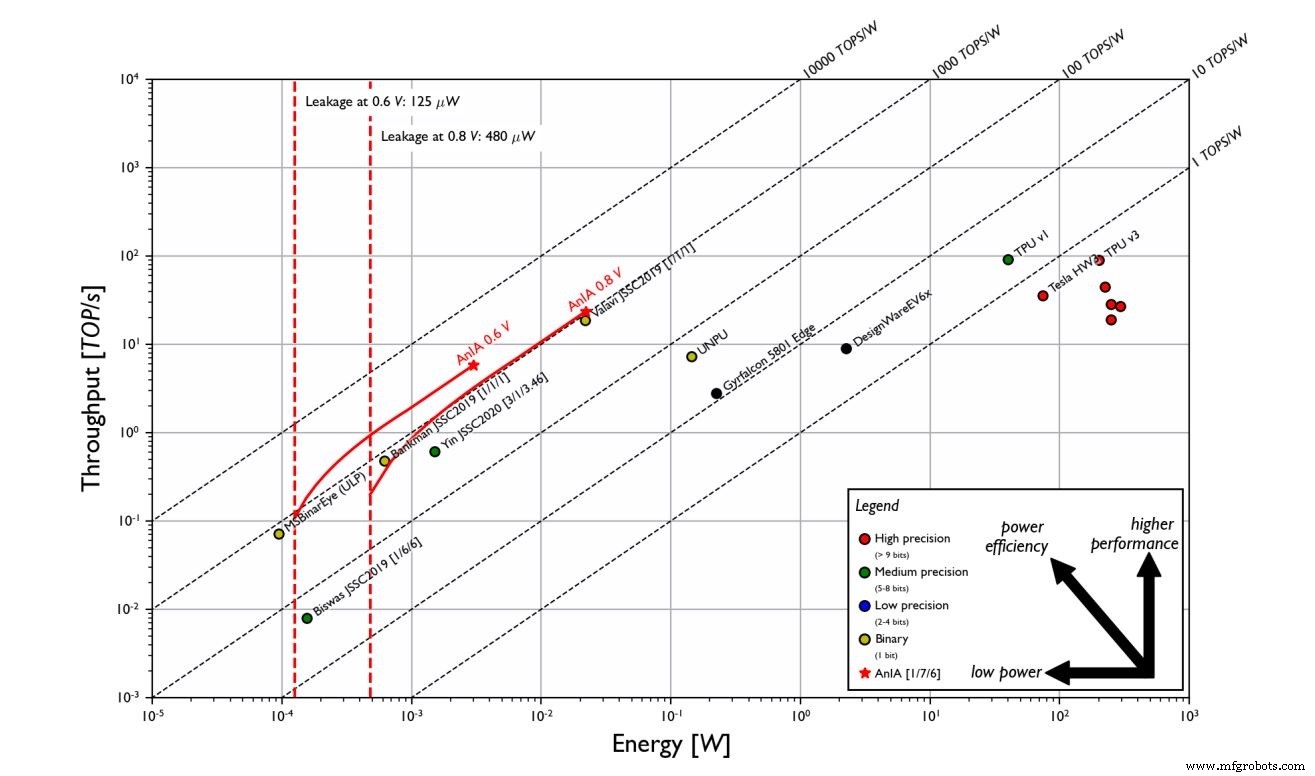

“我们能够在不同的电源电压(0.8 和 0.6V)下产生矩阵向量乘法输出,”Imec 机器学习小组的 Ioannis Papistas 说。 “在不影响操作精度的较低电源电压下操作可以显着降低操作的功耗,这对于能量受限系统中的推理尤其重要。这是我们设计的一个重要特征,由 22FDX 流程支持,可在边缘进行竞争性推理。”

Imec 在 CIFAR 10 数据集上显示了对象识别推理的准确度结果,与类似的量化基线相比,该数据集仅下降了一个百分点。电源电压为 0.8 V 时,AnIA 的能效在 23.5 TOPS 时介于 1050 至 1500 TOPS/W 之间。对于 0.6 V 电源电压,AnIA 在 1800-2900 TOPS/W 左右实现了 5.8 TOPS。

与 Imec 的 AnIA 测试芯片相比,各种 AI 加速器的能效(点击放大)(图片:Imec)

主流创新

“[Imec 展示的] 创新将成为主流,”GlobalFoundries 计算业务部副总裁兼总经理 Hiren Majmudar 说。 “我们看到处于后期生产阶段的 GlobalFoundries 的合作伙伴和客户使用经过验证的硅……我们预计基于模拟计算的硅将在今年年底或明年初左右投产。在大众市场部署方面,我们预计模拟计算肯定不会迟于 2022 年开始进入大众市场。但它可能会比这更早。”

Diederik Verkest(图片:Imec)

GlobalFoundries 正在努力将 Imec 的 AiMC 技术作为可在 22 FDX 平台上实施的一项功能,以实现节能的 AI 加速器。 FD-SOI 工艺专为低功耗而设计,能够在低至 0.5 V 的电压下以每微米 1 微微安培的电流运行,以实现超低待机泄漏。格罗方德位于德国德累斯顿 Fab 1 的 300mm 生产线正在开发具有新 AiMC 功能的 22FDX。

至于 Imec,机器学习计划将继续进行。 Verkest 表示,该集团的目标是使永远在线的智能传感器和消费类可穿戴设备达到 10,000 TOPS/W(低于 100mW 的 10 TOPS)。

“在我们的 ML 计划中,我们的下一步是减少这些计算单元的大小,并开始将新兴存储设备视为这一原则的下一代实现,”他说。

>> 本文最初发表于我们的姊妹网站 EE Times。

嵌入式