使用 FPGA 进行嵌入式设计:构建项目

编者注:随着用于智能产品设计的高级算法不断涌现,开发人员经常发现自己难以实现能够满足这些算法相关处理需求的嵌入式系统。 FPGA 可以提供所需的性能,但长期以来,使用 FPGA 进行设计一直被认为仅限于 FPGA 编程专家的权限。然而,如今功能更强大的 FPGA 和更有效的开发环境的出现使得 FPGA 开发变得更加容易。在此摘录中,即《架构高性能嵌入式系统》一书中的第 4 章,作者全面回顾了 FPGA 器件、实现语言和 FPGA 开发过程,并详细介绍了如何开始在您自己的环境中实现 FPGA。设计。完整的摘录在以下系列文章中提供:

编者注:随着用于智能产品设计的高级算法不断涌现,开发人员经常发现自己难以实现能够满足这些算法相关处理需求的嵌入式系统。 FPGA 可以提供所需的性能,但长期以来,使用 FPGA 进行设计一直被认为仅限于 FPGA 编程专家的权限。然而,如今功能更强大的 FPGA 和更有效的开发环境的出现使得 FPGA 开发变得更加容易。在此摘录中,即《架构高性能嵌入式系统》一书中的第 4 章,作者全面回顾了 FPGA 器件、实现语言和 FPGA 开发过程,并详细介绍了如何开始在您自己的环境中实现 FPGA。设计。完整的摘录在以下系列文章中提供:

1:硬件资源

2:实现语言

3:开发过程

4:构建项目(本文)

5:实现

改编自《架构高性能嵌入式系统》,作者:Jim Ledin。

开发你的第一个 FPGA 项目

在本节中,我们将使用安装在 Digilent Arty A7 开发板上的 Xilinx Artix-7 FPGA 器件开发和实现一个简单但完整的项目。该板有两种变体,一种是低成本版本(129 美元),型号以-35T 结尾,另一种是功能更强大但成本更高的版本(249 美元),型号以-100T 结尾。两块板卡的唯一区别是板上安装的 Artix-7 FPGA 的型号。正如您所料,-35T 的可用资源比 -100T 少。

您可以为此项目使用 -35T 或 -100T 变体。开发过程中的唯一区别是在需要时指定正确的电路板模型。但是,在后面的章节中,由于示例数字示波器项目设计的资源需求,将需要 -100T 变体,因此建议使用功能更强大的板。

Arty A7 开发板可在 https://store.digilentinnc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ 和其他来源(例如亚马逊)购买。

就本项目而言,感兴趣的板上资源是 FPGA 设备本身,以及四个开关、四个按钮和五个 LED。该项目将演示如何安装 Vivado 工具套件、创建项目、输入 HDL 代码、测试代码,并最终生成比特流并将其下载到电路板。将比特流下载到板上后,您将能够手动测试系统的运行情况。您还将看到如何将 FPGA 映像编程到 Arty A7 板上的闪存中,以便它在每次板加电时加载和运行。

项目描述

该项目将在 FPGA 中实现一个四位二进制加法器。这是一个非常简单的设计,因为这里的重点是设置工具和学习如何使用它们,而不是实现复杂的 HDL 模型。

板上的四个开关代表一个 4 位二进制数,四个按钮代表另一个 4 位数字。 FPGA 逻辑将连续执行这两个数字之间的加法运算,并在四个 LED 上以 4 位二进制数的形式显示结果,第五个 LED 代表进位位。

4 位加法器代码基于硬件设计语言中描述的单比特全加器电路 第一章的部分 , 构建高性能嵌入式系统 .

安装 Vivado 工具

我们将在本项目和后续章节中的项目中使用 Xilinx Vivado FPGA 开发工具套件。这些工具是免费提供的,并在 Windows 和 Linux 操作系统上受支持。您可以在任一操作系统上安装这些工具。本节中的描述涵盖了 Windows 版本的工具,但如果您在 Linux 上安装,差异应该很明显。在不同的操作系统上使用 Vivado 工具应该几乎相同:

- 如果您还没有,请在 https://www.xilinx.com/registration/create-account.html 创建一个 Xilinx 用户帐户。

- 访问 https://xilinx.com 并登录您的用户帐户。登录后,转到 https://www.xilinx.com/support/download.html 上的工具下载页面。

- 下载 Xilinx 统一安装程序:Windows 自解压 Web 安装程序 .您可能应该选择可用的最新版本,但如果您想使用本书中使用的版本,请选择版本 2020.1 .

- 安装程序文件的名称类似于 Xilinx_1_0602_1208_Win64.exe。在您的下载目录中找到此文件并运行它。如果对话框警告您安装未经 Microsoft 验证的应用程序,请点击仍然安装 .

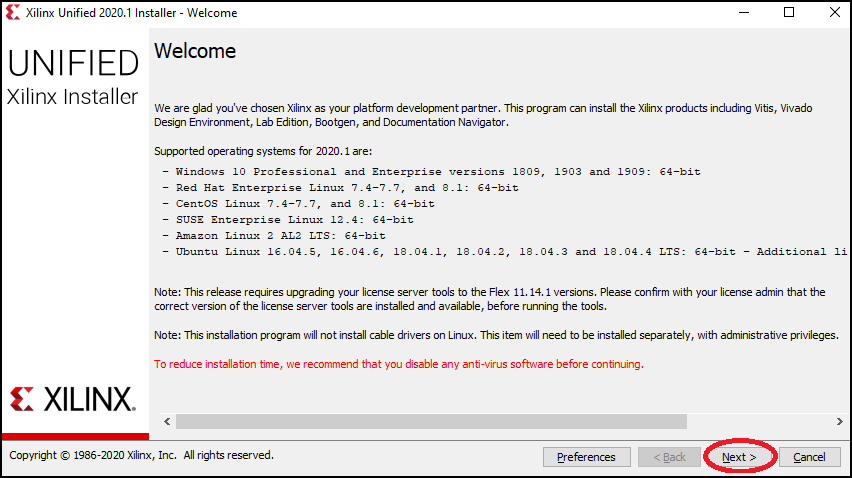

- 当欢迎 屏幕出现,点击下一步 :

图 4.3 – 安装程序欢迎对话框

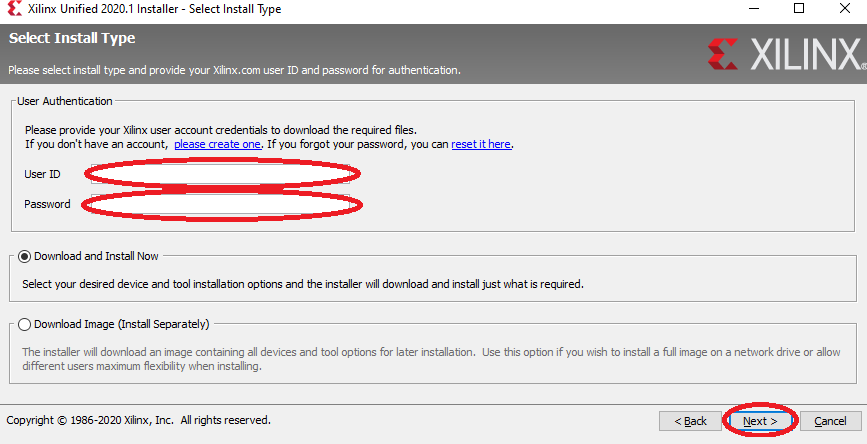

- 在以下屏幕上,输入您的 xilinx.com 用户 ID 和密码,然后单击下一步 :

图 4.4 – 安装程序登录对话框

- 下一个对话框要求您接受一些许可协议。勾选我同意 ,然后点击下一步 .

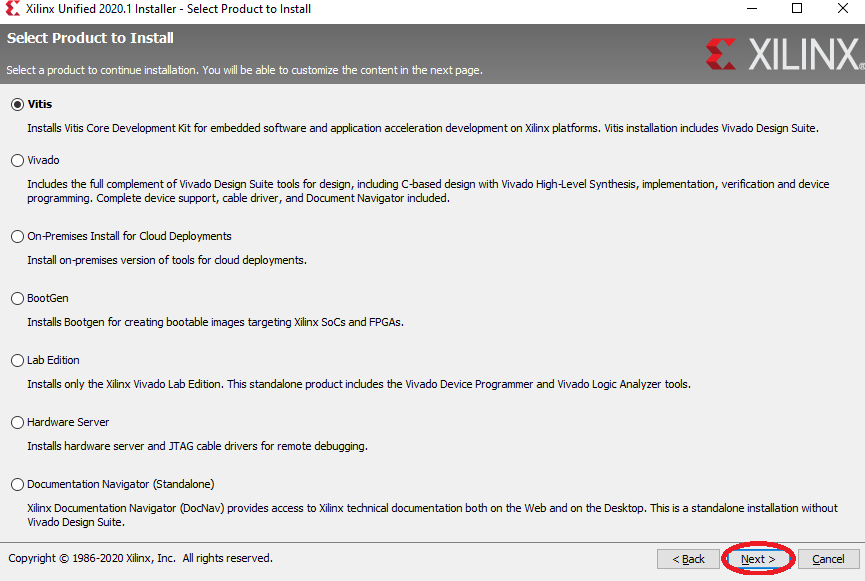

- 在下一个对话框中,离开 Vitis 选择作为要安装的产品,然后单击下一步 . Vitis 包括 Vivado 工具套件以及一系列其他 Xilinx 开发工具:

图 4.5 – 安装程序产品选择对话框

- 下一个对话框允许您选择要安装的软件组件。将选择保留为默认值,然后单击下一步 .

- 下一个对话框允许您选择目标目录并指定程序快捷方式选项。 C:\Xilinx 的目标目录是一个合适的位置。如果该目录不存在,则创建该目录。点击下一步 .

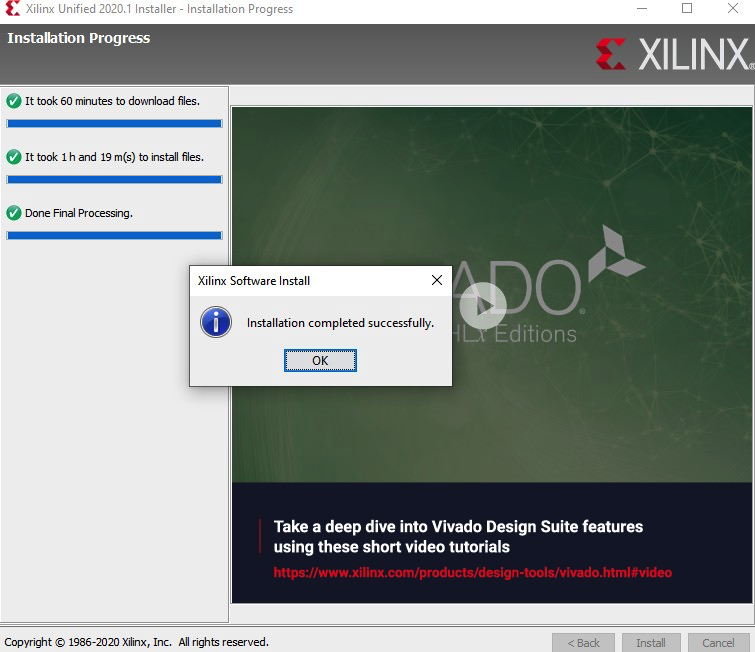

- 下一个对话框显示安装选项的摘要。点击安装 继续安装。根据您的计算机速度和互联网连接速度,安装可能需要几个小时才能完成:

图 4.6 – 安装完成对话框

安装完成后,我们接下来将创建我们的第一个项目。

创建项目

按照以下步骤为 Arty A7 开发板创建和构建 4 位二进制加法器项目:

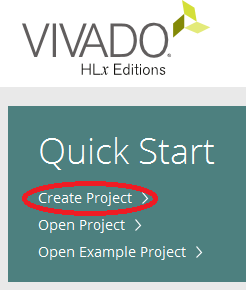

- 找到标题为 Vivado 2020.1 的桌面图标 (或查找您的版本号,如果不同)并双击它。

- 当 Vivado 显示其主屏幕时,单击创建项目 在快速入门 部分:

图 4.7 – Vivado 快速启动对话框

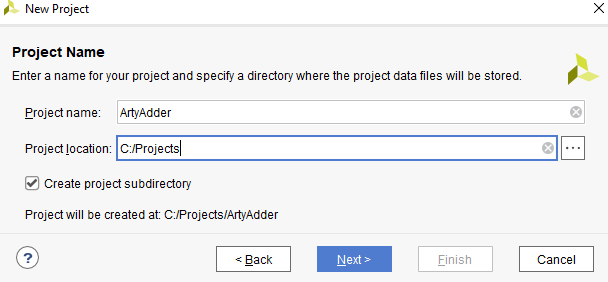

- 这将启动创建新的 Vivado 项目 向导。点击下一步 到达项目名称 页面并输入 ArtyAdder 作为项目名称。为项目选择合适的目录位置并选中创建子目录的复选框,然后单击下一步 .本书中的示例将使用 C:\Projects 目录作为所有项目的位置:

图 4.8 – 项目名称对话框

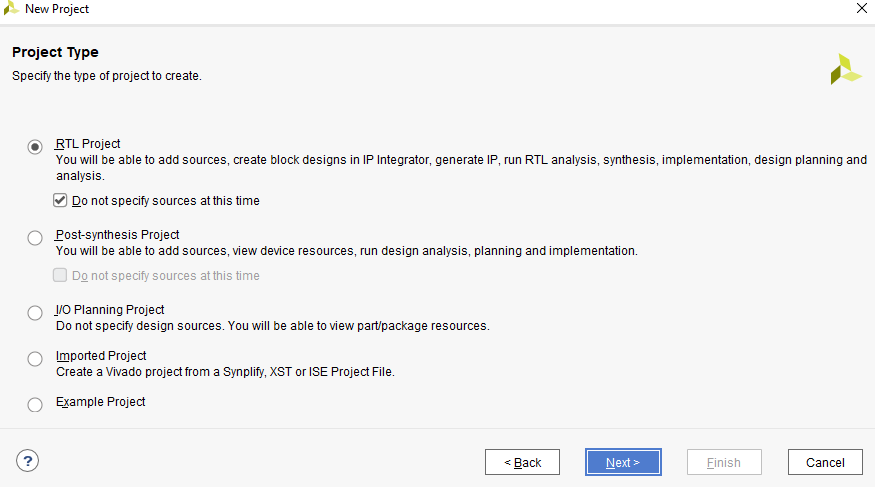

- 在项目类型 对话框,选择 RTL 项目 并选中此时不指定来源旁边的框 .点击下一步 :

图 4.9 – 项目类型对话框

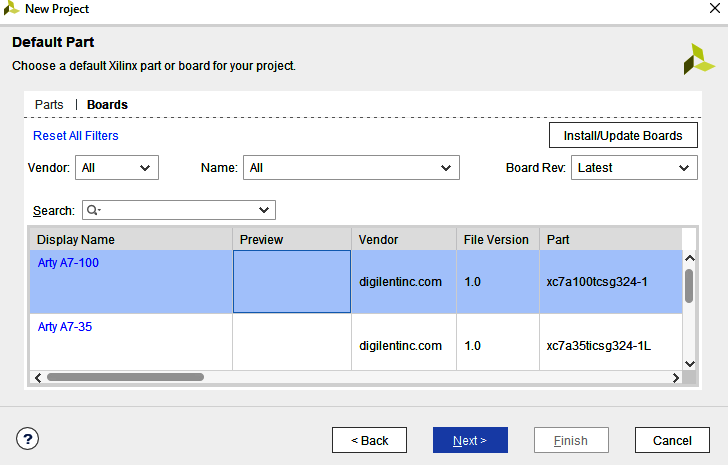

- 在默认部分 对话框,单击板 选项卡,然后在 搜索 中输入 Arty 场地。根据您拥有的电路板类型(或者如果您还没有电路板),选择 Arty A7-100 或 Arty A7-35 然后点击下一步 :

图 4.10 – 默认零件对话框

- 在新项目摘要 对话框,点击完成 .

我们现在已经创建了一个空项目。在下一节中,我们将创建包含该项目的逻辑电路设计的 VHDL 源文件。

创建 VHDL 源文件

以下步骤描述了创建 VHDL 源文件、输入源代码和编译 FPGA 设计的过程:

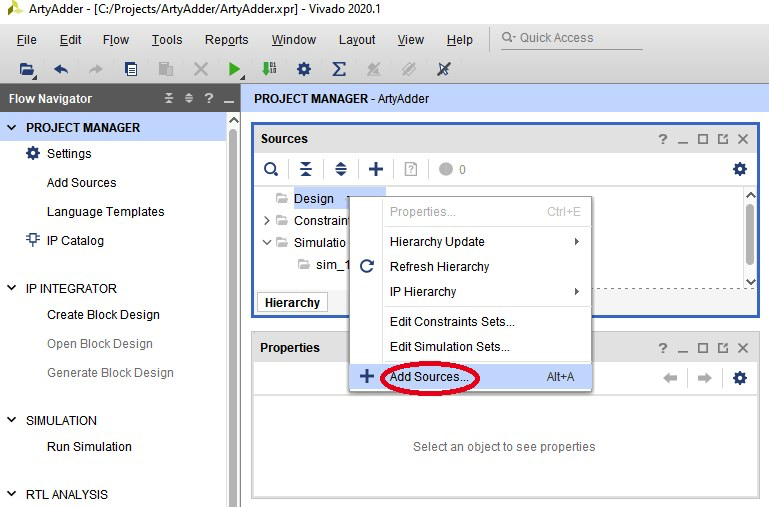

- 在来源 子窗口,右击 Design Sources 并选择添加来源... :

图 4.11 – 添加源...菜单选择

- 在添加来源 对话框,确保添加或创建设计源 被选中,然后点击下一步 .

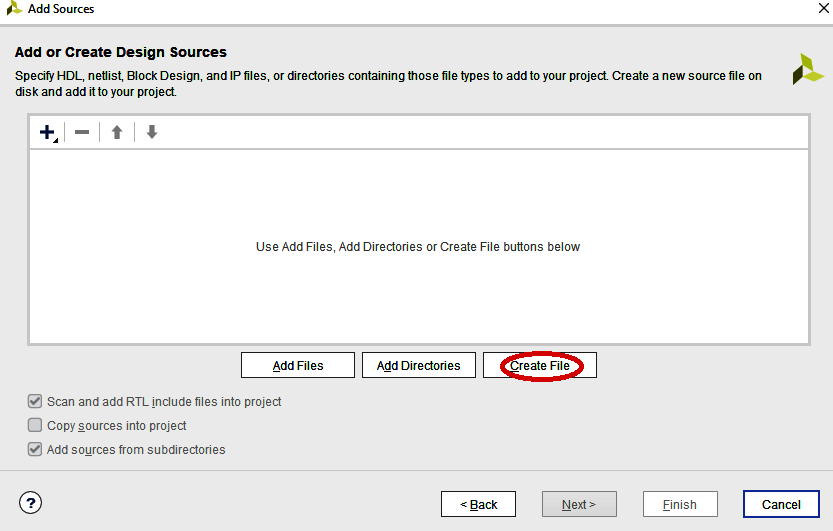

- 在添加或创建设计源 对话框,点击创建文件 :

图 4.12 – 添加或创建设计源对话框

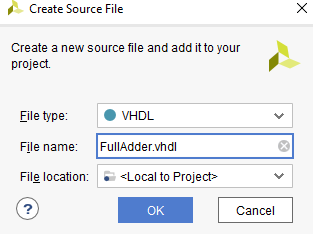

- 输入文件名 FullAdder.vhdl 并点击确定 :

图 4.13 – 创建源文件对话框

- 重复前两步创建另一个名为Adder4.vhdl的文件,然后点击Finish 在添加或创建设计源 对话框。

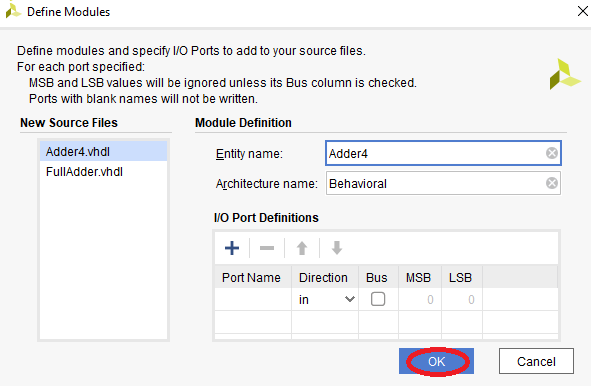

- 定义模块 接下来会出现对话框。我们不会在这里输入任何内容。点击确定 关闭它 您将被询问是否确定要使用这些值。点击是 :

图 4.14 – 定义模块对话框

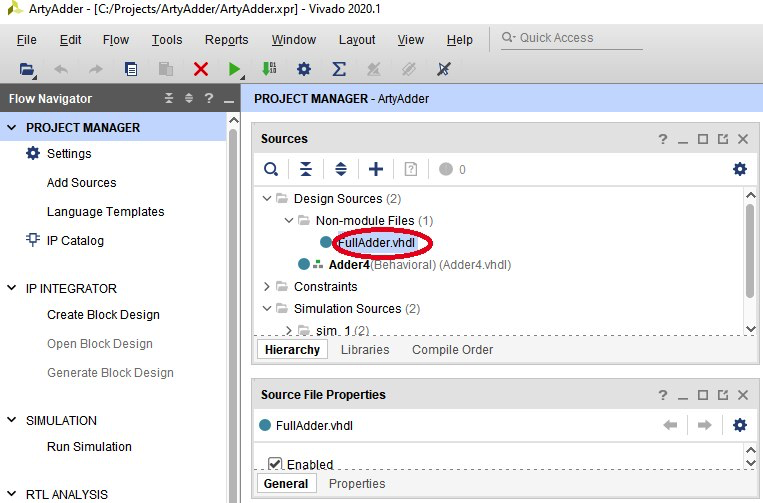

- 展开非模块文件 在设计来源下 ,然后双击 FullAdder.vhdl。将打开一个编辑器窗口,显示空的 FullAdder.vhdl 文件:

图 4.15 – 新创建的源文件

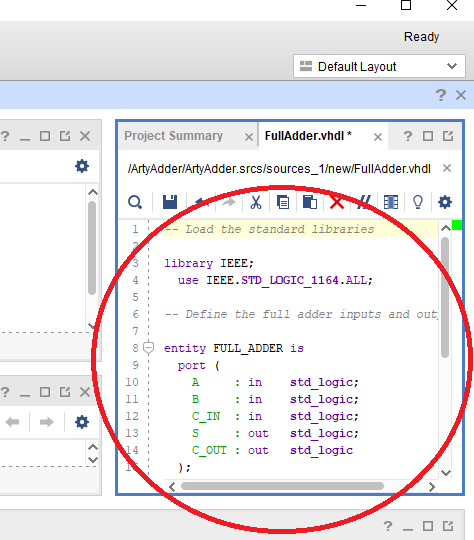

- 在 FullAdder.vhdl 编辑器窗口中输入以下 VHDL 代码:

-- 加载标准库 IEEE;使用IEEE.STD_LOGIC_1164.ALL;--定义全加器输入和输出实体FULL_ADDER是端口(A:在std_logic中;B:在std_logic中;C_IN:在std_logic中;S:在std_logic中;S:在std_logic中;C_OUT:在std_logic中);末端实体FULL_ADDER; -- 定义FULL_ADDER的全加器架构BEHAVIORAL的行为 isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A AND B) OR ((A XOR B) AND C_IN);端架构行为;

这与我们在硬件设计语言中检查的单比特全加器代码相同 第 1 章,构建高性能嵌入式系统的部分 . 图 4.16 在 Vivado 编辑器窗口中显示代码:

图 4.16 – FullAdder.vhdl 源代码

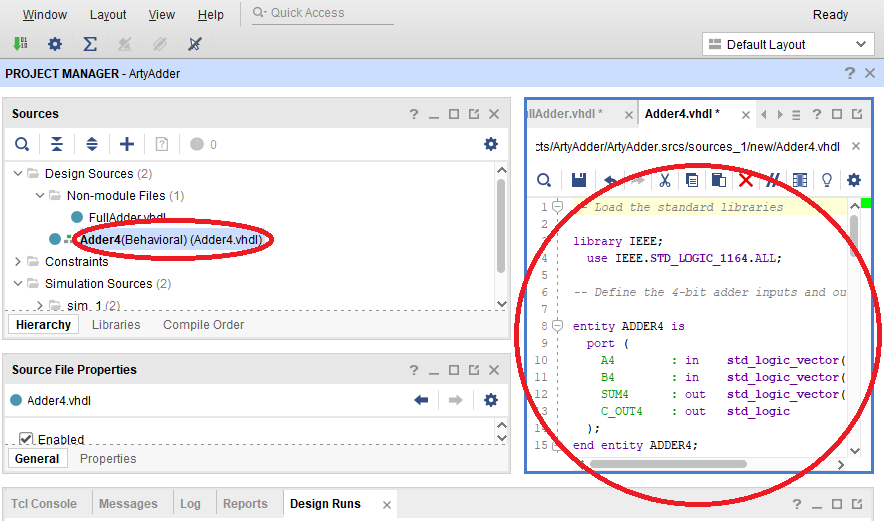

- 以同样的方式,双击Adder4(Behavioral) (Adder4.vhdl) 在设计来源下 .删除 Adder4.vhdl 的自动填充内容 编辑器窗口并在 Adder4.vhdl 中输入以下代码 编辑:

-- 加载标准库 IEEE;使用 IEEE.STD_LOGIC_1164.ALL;-- 定义 4 位加法器输入和输出实体 ADDER4 是端口 ( A4 :in std_logic_vector(3 downto 0); B4 :in std_logic_vector(3 downto 0); SUM4 :out std_logic_vector(3 downto 0) ); C_OUT4 :out std_logic );end entity ADDER4;-- 定义4-bit adderarchitecture BEHAVIORAL of ADDER4的行为是 -- 参考之前定义的全加器组件FULL_ADDER is port ( A :in std_logic; B :in std_logic; C_IN :in std_logic; S :out std_logic; C_OUT :out std_logic );终端组件; -- 定义4位加法器信号c0、c1、c2内部使用的信号:std_logic;begin -- 第一个加法器的进位输入设置为0 FULL_ADDER0 :FULL_ADDER 端口映射( A => A4(0), B => B4(0), C_IN => '0', S => SUM4(0), C_OUT => c0 ); FULL_ADDER1 :FULL_ADDER 端口映射 (A => A4(1), B => B4(1), C_IN => c0, S => SUM4(1), C_OUT => c1); FULL_ADDER2 :FULL_ADDER 端口映射 ( A => A4(2), B => B4(2), C_IN => c1, S => SUM4(2), C_OUT => c2); FULL_ADDER3 :FULL_ADDER 端口映射 (A => A4(3), B => B4(3), C_IN => c2, S => SUM4(3), C_OUT => C_OUT4 );终端架构行为;

此代码实例化了单位全加器的四个副本。最低有效加法器的进位设置为零,每个加法器的进位波动到下一个最高有效加法器。两个4位数字相加的结果是一个4位结果和一个单位进位:

图 4.17 – Adder4.vhdl 源代码

下一篇文章将展示如何测试设计并实现我们的 Arty 板设计。

经 Packt Publishing 许可转载。版权所有 © 2021 Packt Publishing

吉姆·莱丁 是 Ledin Engineering, Inc. 的首席执行官。Jim 是嵌入式软件和硬件设计、开发和测试方面的专家。他还擅长嵌入式系统网络安全评估和渗透测试。他拥有学士学位爱荷华州立大学航空航天工程学士学位和硕士学位。佐治亚理工学院电气和计算机工程学士学位。 Jim 是加利福尼亚州的注册专业电气工程师、认证信息系统安全专家 (CISSP)、认证道德黑客 (CEH) 和认证渗透测试员 (CPT)。

吉姆·莱丁 是 Ledin Engineering, Inc. 的首席执行官。Jim 是嵌入式软件和硬件设计、开发和测试方面的专家。他还擅长嵌入式系统网络安全评估和渗透测试。他拥有学士学位爱荷华州立大学航空航天工程学士学位和硕士学位。佐治亚理工学院电气和计算机工程学士学位。 Jim 是加利福尼亚州的注册专业电气工程师、认证信息系统安全专家 (CISSP)、认证道德黑客 (CEH) 和认证渗透测试员 (CPT)。 相关内容:

- 使用 FPGA 进行嵌入式设计:硬件资源

- 使用 FPGA 进行嵌入式设计:实现语言

- 使用 FPGA 进行嵌入式设计:开发过程

- 开源工具有助于简化 FPGA 编程

- 在 FPGA 或 ASIC 中实现浮点算法

- 利用 FPGA 进行深度学习

- 软件工具将 GPU 代码迁移到 FPGA 以用于 AI 应用

- FPGA 取代了 Subaru Eyesight 基于视觉的 ADAS 中的 ASIC

有关 Embedded 的更多信息,请订阅 Embedded 的每周电子邮件通讯。

嵌入式