V/SiOx/AlOy/p++Si 器件作为选择器和存储器的双重功能

摘要

这封信展示了双重功能,包括 V/SiOx 中的选择器和存储器切换 /AlOy /p ++ 通过简单地控制顺从电流限制 (CCL) 来实现硅电阻存储器件。在具有 1 μA 的低 CCL 的正形成后观察到单向阈值切换。 VOx 向氧的 V 电极侧移动 层,其中阈值切换可以通过金属绝缘过渡现象来解释。对于应用于器件的更高 CCL (30 μA),获得双极存储器切换,这归因于 SiOy 中导电丝的形成和破裂 层。 1.5 纳米厚的 AlOy 具有高热导率的层在降低存储器和阈值开关的关断电流方面起着重要作用。通过温度依赖性,确认了 LRS 中的高能垒 (0.463 eV),这会导致低电阻状态下的非线性。 CCL 越小,非线性度越高,这在交叉点阵列中提供了更大的阵列尺寸。符合 CCL 的存储器和阈值切换的共存为控制设备的预期用途提供了灵活性。

背景

电阻式随机存取存储器 (RRAM) 因其开关速度快 [1, 2]、低功耗 [3,4,5,6,7 ,8],多级能力[9,10,11,12,13,14,15],高可扩展性[16,17,18,19,20],3D堆叠能力[21,22,23,24,25] ]。这些特性特别适用于存储类内存 (SCM),它可以填补作为主存储器的动态随机存取存储器 (DRAM) 与作为存储存储器的固态驱动器 (SSD) 之间的性能差距。尽管 RRAM 设备在过去几年取得了很大进展 [1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19 ,20,21,22,23,24,25],然而,仍然存在一个主要缺点:通过相邻单元的潜行电流发生在高密度交叉点阵列中 [26]。具有选择器组件的存储设备应提供非线性电流-电压 (I-V) 特性来克服这个问题 [26,27,28,29,30,31,32,33,34,35]。到目前为止,具有非线性概念的各种器件,例如互补电阻开关 (CRS) [26]、隧道势垒 [27,28,29,30,31,32,33]、基于银的阈值开关 [34]、二极管型选择器 [35, 36]、ovonic 阈值切换 (OTS) [37, 38] 和金属绝缘体过渡 (MIT) [39,40,41,42,43] 已被报道。 VOx 作为典型的 MIT 材料之一,它可以作为光和电开关组件广泛用于潜在应用中 [40,41,42]。 SiO2在半导体工业中被广泛用作钝化层。此外,富硅 SiOx (x <2) 可用作 RRAM 中的电阻变化层 [44,45,46,47,48,49,50,51,52,53,54,55]。二氧化硅x 在与 CMOS 工艺的兼容性和低成本方面,它比许多其他材料更受欢迎。二氧化硅x 据报道,基于 RRAM 的器件仅通过使用具有高扩散率的 Cu 和 Ag 等电极就可以充当传导桥的中介 [44,45,46,47]。在另一种情况下,存储器切换是由 SiOx 内部的价变效应引起的 层,这可以通过产生氧空位或质子交换模型来解释 [48,49,50,51,52,53,54,55]。在设置操作先于复位的单极开关中,它对环境气氛很敏感。空气中的开关性能显着降低 [48,49,50,51,52,53]。另一方面,没有反向扫描效应的丝状开关在各种 SiOx 中表现出典型的单极和双极开关 基于RRAM设备[52,53,54]。

在这里,我们展示了 V/SiOx 中阈值切换和存储器切换的共存 /AlOy /p ++ Si 器件取决于合规电流限制 (CCL)。与传统金属电极相比,具有硅底电极 (BE) 的器件具有多个优点。具有存储器或阈值开关的 RRAM 器件直接连接到晶体管中的源极或漏极侧,这是嵌入式存储器和陡坡器件的潜在应用。由于 Si BE 的串联电阻,可以降低过冲电流。此外,通过湿法蚀刻和调整硅表面掺杂浓度的硅BE纳米尖端可以提高开关性能。氧化铝y 层是具有绝缘特性的大带隙,有助于降低阈值和存储器切换期间的工作电流。 SiOx 层在高 CCL 时充当存储器切换层,而在低 CCL 时为 V TE 提供氧气,从而提供阈值切换。

方法

V/SiOx /AlOy /p ++ Si器件制作如下:首先,以40 keV的加速能量和5 × 10 15 的剂量注入BF2离子 cm −2 进入 Si 衬底到重掺杂的 Si BE。通过在 1050°C 下进行 10 分钟的退火工艺来治愈晶格损伤。重掺杂的 Si BE 具有 30.4 Ω/□ 的薄层电阻。接下来,1.5 纳米厚的 AlOy 层通过原子层沉积 (ALD) 系统使用 H2O 和 Al (CH3)3 以及 5.5 nm 厚的 SiOx 沉积 通过在 300°C 下使 5% SiH4/N2 (160 sccm)、N2O (1300 sccm) 和 N2 (240 sccm) 反应,该层经历了等离子体增强化学气相沉积 (PECVD)。随后,通过使用 Ar 气 (30 sccm) 直流溅射 V 靶来沉积直径为 100 μm 的 50 nm 厚的钒 (V) 顶部电极 (TE)。最后,通过直流溅射沉积 50 nm 厚的 Al 作为保护层,以防止 V TE 进一步氧化。使用吉时利 4200-SCS 半导体参数分析仪 (SPA) 和 4225-PMU 超快电流-电压 (I-V) 模块在室温下分别通过直流电压扫描和脉冲模式表征所有电气特性。对于器件操作,TiN BE 接地并控制 Ni TE 偏置。

结果与讨论

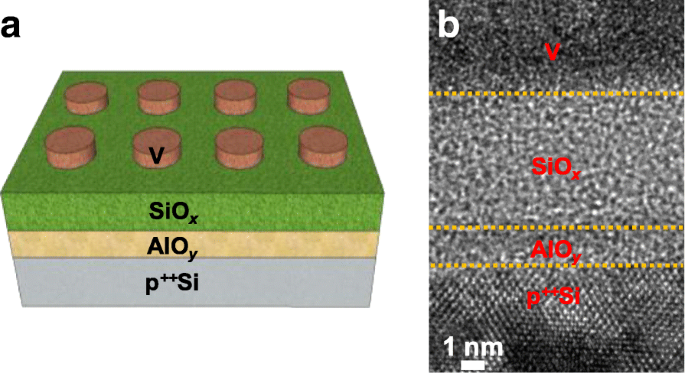

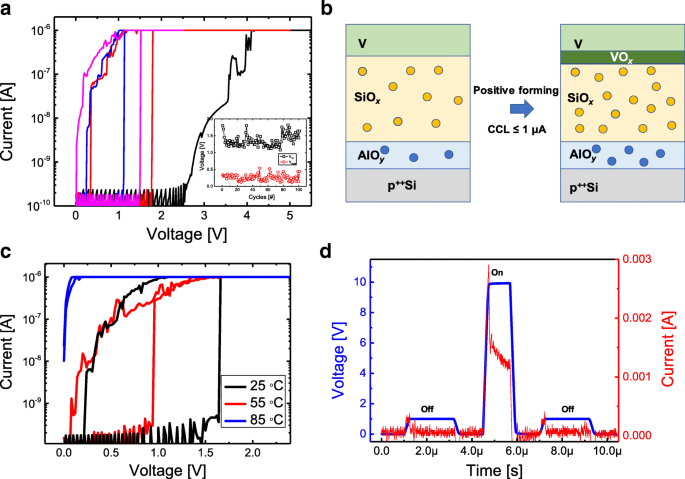

图 1a 显示了 V/SiOx 的结构示意图 /AlOy /p ++ 硅装置。三无定形V,SiOx , 和 AlOy 通过透射电子显微镜(TEM)横截面图像观察层和单晶硅层,如图 1b 所示。 SiOx 的厚度 和AlOy 层分别为 5.5 和 1.5 纳米。为了确认两种介电薄膜的组成比,进行了 XPS 分析(附加文件 1)。 x SiOx 的值 和 y AlOy 的值 分别为 0.88 和 1.33。我们的 SiOx 与使用干氧化沉积的 SiO2 相比,使用 PECVD 的薄膜在低得多的温度下沉积并且具有更多的缺陷,使其适合在相对较低的电压下进行电阻开关。图 2a 显示了 V/SiOx 的典型阈值切换 /AlOy /p ++ 硅装置。由于介电层最初具有较小的缺陷,因此使用正形成工艺的初始切换比随后的阈值切换需要更高的电压。将 1 μA 的 CCL 应用于器件以避免在 SiOx 中形成过多的导电细丝 层。与之前报道的 VOx 阈值切换相比,漏电流非常低(1 V 时为 100 pA) .这一优势归因于与 SiO2 相比具有更高介电常数和热导率的 Al2O3。断态具有绝缘特性,因为灯丝很容易破裂,然后没有剩余的灯丝。阈值切换的一种可能机制是来自 SiOx 提供的氧对 VTE 的氧化 如图 2b 所示。 VOx的电学性质 V TE 和 SiOx 之间 层可能会从绝缘状态变为金属状态,从而导致电阻的突然变化。 1 μA 的低 CCL 不足以在 SiOx 内形成有效的导电细丝 电影。因此,SiOx 具有绝缘特性可能是降低关断电流的另一个原因。对于 V/SiOx 的负形成过程 /AlOy /p ++ Si 设备,未观察到阈值切换(请参阅附加文件 1)。当对V TE 施加负偏压时,氧化物的运动向Si BE 移动,因此V TE 不再像VOx 那样参与阈值切换 .图 2a 的插图展示了 100 个周期期间的阈值电压 (Vth) 和保持电压 (Vhold)。电流以几乎无穷大的斜率急剧增加的 Vth 介于 1.08 和 1.82 V 之间,而此时电流返回到高电阻状态的 Vhold 介于 0.12 和 0.54 V 之间。图 2c 显示了导通中的 I-V 特性- 不同温度下的电流。在 25°C 和 55°C 下,它们显示出几乎相似的阈值切换,但在 85°C 的较高温度下的 I-V 曲线失去了阈值切换特性。众所周知,VOx 在高温下失去其 MIT。因此,这个结果是另一个证明 VOx 是阈值切换的主要原因。图 2d 显示了阈值切换的瞬态特性。幅度为 1 V 的脉冲监测宽度为 1 μs 的写入脉冲前后的读取电流。在对器件施加高振幅脉冲的同时监测高电流,然后,V/SiOx /AlOy /p ++ Si 器件在删除写入脉冲后立即关闭电流。当与低于 1 μA 的存储器元件的操作相结合时,可以使用上面分析的选择器属性 [55, 56]。

<图片>

V/SiOx的器件配置 /AlOy /p ++ 西。 一 示意图和b 透射电镜图像

<图片>

V/SiOx/AlOy/p ++ 的单向阈值切换 当使用 1 μA 的 CCL 进行正成型时的 Si。 一 典型的 I-V 曲线。 b 成型工艺示意图。 c 温度依赖性的 I-V 特性。 d 瞬态特性

图 3a 显示了 V/SiOx 的双极电阻切换 /AlOy /p ++ 使用 100 μA 的 CCL 进行正成型后的 Si 器件。然后,通过扫负电压进行电阻快速增加的复位过程,器件切换到高阻状态(HRS)。然后在正偏置电压下发生电阻快速下降的设置过程,导致器件返回到低电阻状态 (LRS)。为了了解导电灯丝的特性,我们观察归一化电导和温度依赖性。 LRS 中的传导是间接告知导电灯丝特性的重要指南。图 3b 显示了归一化电导 (GN),其定义为动态电导 (Gd) 除以静态电导 (G0),用于 V/SiOx 的 I-V 曲线 /AlOy /p ++ 具有不同温度的 LRS 中的 Si 器件。无论温度如何,当电压为零时,GN 值都会收敛到 1。这使我们可以排除众所周知的传导机制,例如肖特基发射、福勒-诺德海姆隧道效应和柴尔德定律 (I~V 2 ) 在空间电荷限制电流 (SCLC) 中。考虑到温度依赖性,也可以排除金属欧姆传导,如图 3c 所示。电阻随温度升高而降低表明导电丝具有半导体特性。因此,我们可以排除 V 渗透到 SiOx V/SiOx 主导电丝层 /AlOy /p ++ LRS 中的 Si 器件。因此,V/SiOx的双极记忆操作 /AlOy /p ++ Si器件主要是SiOx的本征转换 .还证实正负电流没有太大不同,这表明它不是像肖特基发射这样的界面类型,而是由体传导主导。考虑到上述归一化电导,有两种可能的体主导传导机制。第一个是跳跃传导,公式如下:

$$ J={qnav}_o{e}^{-q{\o}_T/ kT}{e}^{qaV/2 dkT} $$ <图片>

V/SiOx的内存切换 /AlOy /p ++ 当使用 30 μA 的 CCL 进行正成型时的 Si。 一 典型的 I-V 曲线。 b 归一化电导。 c 在 (I) 与 1000/T 中。 d 成型工艺示意图

其中 q , n , a , ø T , v o , 和 d 分别是电荷、空间电荷浓度、跳跃距离的平均值、跳跃的电子势垒高度、固有振动频率和介电膜的厚度。 ø T 从 ln (I) 与 1000/T 的线性图的斜率计算的 0.463 eV,如图 3c 所示。根据 Ea 和 V 之间的关系计算得出的值为 5.17 nm,表明在 SiOx 中形成了导电细丝 不强,接近HRS状态。另一种传导机制,Poole-Frenkel (P-F) 发射,在附加文件 1 中有介绍。基于上述结果,V/SiOx 存储器操作中的导电灯丝模型 /AlOy /p ++ Si 器件如图 3d 所示。在正极形成过程中,氧化过程在 V TE 侧进行,但由于高 CCL,可以在 SiOx 内部形成导电细丝 和AlOy 由于氧空位的移动。在复位过程中,与形成和设置相反的电场诱导氧并与氧空位复合,导致导电丝断裂。需要注意的是,选择器和内存操作是在同一个单元格中观察到的。发生阈值操作后,可以进行内存操作,然后开关完全关闭。然而,相反的方向是不可能的,因为存储器操作的复位开关没有完全关闭。

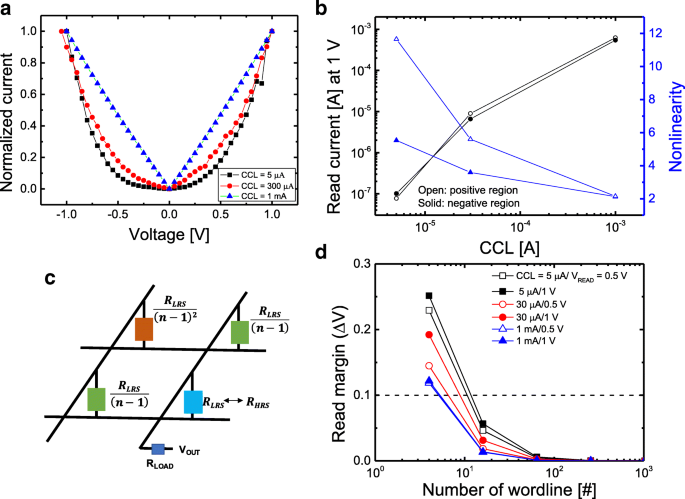

图 4a 显示了 V/SiOx 的 LRS 中的归一化 I-V 曲线 /AlOy /p ++ 不同 CCL 条件(5 μA、30 μA 和 1 mA)下处于低电压状态 (0~1 V) 的 Si 器件。这里,归一化的 I-V 曲线定义为每个电压下的电流除以 1 V 处的电流。由于 LRS 电流的水平取决于 CCL,我们将电流值设置为 1 V 以轻松比较非线性。可以观察到,随着 CCL 降低,电流在较低电压状态下被抑制。为了推导出更定量的关系,非线性被定义为 VREAD 处的电流与 VREAD 一半处的电流之比。图 4b 显示了 V/SiOx 在 1 V 时的读取电流和作为 CCL 函数的非线性 /AlOy /p ++ 硅装置。由于 CCL 减少而导致读取电流的降低表明导电灯丝变得更细,然后非线性度增加。本征氧化硅膜即使在单层中也表现出高非线性。固有的非线性特性是由于氧化硅的本体性质而不是硅的界面。 CCL 越小,SiOx 中产生的降解越少 ,因此与 HRS 相比,LRS 中陷阱能级的降低可以最小化。因此,当较低的 CCL 应用于器件时,较高的能量势垒可以最大限度地提高 LRS 状态的非线性。类似地,由 TaOx 中的 P-F 发射描述的传导 /TiOy 堆栈确保高非线性[57]。另一种可能性是因为氧化物的介电常数较小,由于场的集中,对氧化物膜进行了更多的通过。这会导致氧化物层的陷阱能级降低,可以预期作为 Al2O3 的隧道势垒。获得n中的读取余量(ΔV) × n 交叉点阵列,我们使用简化的等效电路,如图 4c 所示。考虑到最坏的情况,相邻小区设置为 LRS,负载电阻 (RL) 设置为 LRS 电阻。 ∆V 是根据 LRS 处的 VOUT 和 HRS 处的 VOUT 之间的差异计算得出的。图 4d 显示了作为字线数 (n ) 对于 V/SiOx /AlOy /p ++ 硅装置。 CCL 越小,ΔV 越高,因为非线性增加。当确保 10% 的读取余量时,对于 5 μA 的 CCL,阵列可以扩展到大约 10 × 10 以上,对于 1 mA 的 CCL,可以扩展到 5 × 5。能够承受潜行电流的阵列尺寸是不够的,但是当具有选择器功能的器件连接在 V/SiOx 中时,它有助于扩大阵列尺寸 /AlOy /p ++ 硅装置。与所有 CCL 中的 0.5-V 读取相比,它在 1 V 读取时具有更高的非线性。虽然低 VREAD 导致读取操作中的静态功耗低,但非线性值变小,这是由于电场在 SiOx 上较少 /AlOy 较小的 VREAD 中的层。

<图片>

V/SiOx的非线性特性 /AlOy /p ++ Si 用于内存切换。 一 具有不同 CCL 的 I-V 曲线。 b 读取电流和非线性作为 CCL 的函数。 c 交叉点阵列的等效电路。 d 作为不同 CCL 的字线数和读取电压的函数的读取裕量

结论

在这项工作中,V/SiOx /AlOy /p ++ 研究了通过简单地控制CCL同时具有选择器和存储功能的Si器件。当应用 1 μA 或更小的 CCL 时,会观察到选择器应用的单向阈值切换。正形成氧化 V 电极和 VOx 的 MIT 现象 可以诱导阈值切换。氧化铝y 层能够实现10 4 的高选择性 通过降低关断电流。另一方面,当应用 5 μA 或更大的 CCL 时,观察到存储器切换,因为在 SiOx 上形成了有效的导电细丝 层。 CCL越低,非线性越大,有助于增加交叉点阵列的尺寸。

缩写

- ALD:

-

原子层沉积

- 基础:

-

底部电极

- CCL:

-

合规电流限制

- CRS:

-

互补电阻开关

- DRAM:

-

动态随机存取存储器

- HRS:

-

高阻态

- I-V:

-

电流-电压

- LRS:

-

低阻态

- 麻省理工学院:

-

金属绝缘体过渡

- OTS:

-

卵巢阈值切换

- PECVD:

-

等离子体增强化学气相沉积

- P-F:

-

普尔-弗兰克尔

- RRAM:

-

电阻式随机存取存储器

- SCLC:

-

空间电荷限制电流

- 单片机:

-

存储类内存

- SPA:

-

半导体参数分析仪

- SSD:

-

固态硬盘

- TE:

-

顶部电极

- TEM:

-

透射电子显微镜

- V:

-

钒

纳米材料