蚀刻变化对 Ge/Si 沟道形成和器件性能的影响

摘要

在绝缘体上硅 (SOI) 衬底上形成 Ge 鳍结构期间,我们发现必须仔细控制干蚀刻工艺。否则,可能会导致 Ge 过度蚀刻或形成不良的 Ge 鳍片轮廓。如果蚀刻工艺控制不好,顶部的Ge/SOI结构会被蚀刻掉,只剩下Si fin层。在这种情况下,设备表现出异常特性。蚀刻工艺正在成为器件缩放和封装的关键步骤,并影响增加封装密度和提高器件性能的尝试。因此,建议通过模拟来执行操作等离子体反应器的优化,以便不仅调整所使用的工艺参数而且修改所使用的硬件。我们将通过采用更新的制造参数来开发 Ge 无结器件。此外,我们希望通过循环热退火工艺消除界面处的错配位错或减少螺纹位错,以达到获得高质量外延Ge层悬浮结构的目标。

背景

提高半导体器件响应速度并降低其功耗的一种方法是使用具有高载流子迁移率的半导体。这种材料的例子包括Ge及其合金和化合物。然而,当通过在不同半导体的衬底上堆叠一层半导体材料来形成结构时,可能会出现问题。例如,半导体衬底和不同半导体材料的上覆层的晶格尺寸的差异可能导致位错,这可能对器件性能产生不利影响。传统上,为了制造包括Si衬底的Ge基半导体器件,在硅衬底上形成更厚的缓冲层或牺牲层(例如,Si/Ge缓冲层)。随后,在Si/Ge缓冲层上生长Ge外延层。接着,依次进行各向异性和各向同性刻蚀工艺,去除部分缓冲层,保留Ge外延层。 VLSI 器件必须表现出高驱动电流、低断态泄漏电流和低电源电压,以确保高性能,包括低待机功耗和降低的动态功耗。目前,应变增强迁移率、高 k/金属栅极和 22 nm 节点的三维 (3D) 器件架构 [1] 是一些用于互补金属氧化物半导体连续缩放的技术。 CMOS) 具有 Si 通道的器件。除了高迁移率等特性外,还需要新的器件架构,例如环栅 (GAA) [2] 和超薄体场效应晶体管 (FET) [3] 的结构,以改善子器件中的静电控制。 -10 纳米节点。已经证明了具有反转模式 (INV) 操作的基于 Ge 的 GAA pFET [4] 和 nFET [5]。然而,由于掺杂剂溶解度低、掺杂剂扩散快和热预算低,Ge INV 器件中的结形成是一个关键问题。为了解决这些问题,已建议使用与源极/漏极 (S/D) 区域相同载流子类型的重掺杂沟道的无结 (JL) 器件 [6] 作为替代方案。然而,晶体管的快速缩放需要开发能够赶上现代晶体管的新的、更有效的设备。近年来,人们发现 JL-FET 有望作为下一代晶体管。 JL-FET 基本上是一个电阻,其中的移动载流子密度可以由栅极控制。在导通状态下,由于沟道区的掺杂浓度较高,因此存在较大的体电流;将表面累积电流添加到该电流中 JL-FET 中的掺杂水平需要很高以实现合适的电流驱动,同时器件横截面需要足够小以便器件可以关断.然而,在高掺杂 JL-FET 的情况下,载流子经历了显着的杂质散射,因此驱动电流显着降低 [7]。此外,与 INV 器件相比,JL-FET 具有制造简单、电荷迁移率高和栅极电容低的优点 [8,9,10,11,12]。最近,双栅极[13]和体连接三栅极[14]Ge JL-FET pMOSFET分别在绝缘体上锗衬底和体硅上进行了演示。

随着微电子设备的不断缩小和工艺要求变得越来越严格,等离子体建模和仿真作为等离子体反应器的设计、控制和优化工具变得越来越有吸引力 [15]。基于长度和时间尺度的差异,使用了多种技术来模拟等离子体过程的行为。模拟技术之一,计算流体动力学 (CFD),广泛用于预测工程设计特征的流场和推断实验限制。它的建模已被应用于研究流动混合现象 [16],但在蚀刻过程中很少研究。因此,本研究提出对刻蚀过程中等离子体反应器的热流场进行详细表征,进而推导出对实验有益的数值参数。

在这项工作中,进行蚀刻以在 Si 以及其他合金半导体上形成悬浮的外延 Ge 层,用于器件集成。模拟结果将通过实验验证;因此,将修改初始和边界条件以及数值模型中的参数以提高数据可靠性。我们预计可以通过实验和模拟获得最佳参数以改进蚀刻技术,并通过执行更高的制造工艺质量和更低的生产成本来实现晶体管的开发。

方法/实验

起始衬底是具有 70 nm 顶部硅层(p 型,9-18 Ω cm)的 SOI 晶片。使用 RCA 标准清洁 1 (SC-1) 和 RCA 标准清洁 2 (SC-2) 工艺清洁晶片,以去除任何有机物、不需要的金属和存在的颗粒。随后在去离子水中漂洗并在N 2 中干燥。 Ge 薄膜在低压化学气相沉积外延反应器 (Epsilon 2000, ASM) 中沉积,使用 10% GeH4 作为前驱体。氢气用作载气。在沉积 Ge 膜之前,在 850 °C 和 10 Torr 下进行原位 HCl 基预处理以制备晶片表面。然后将衬底温度更改为 400 °C,以使用 10% GeH4 在 SOI 晶片上生长 Ge 膜。使用透射电子显微镜(TEM,热发射肖特基型,0.5-200 kV)确定沉积的 Ge 膜的厚度。使用X射线衍射(XRD)分析(D8A,Bruker,CuKα辐射,λ =1.5408 Å,20-70°)检查Ge膜的结晶度。此外,使用 X'Pert MRD(帕纳科)系统在 (004) 衍射峰周围进行 Ω-2θ 扫描。使用双重 Ge {400} 通道切割晶体准直器来选择 CuKα1 辐射。在标准 XRD 测量期间,样品固定在水平位置,衍射仪的源和探测器臂在 θ-θ 模式下移动。使用上述晶体准直器在中等分辨率模式下进行倒易空间映射;闪烁计数器前面的探测器臂上存在 0.4 毫米宽的狭缝。 Ge 层的厚度通过椭圆光度法测量 (M2000, J. A. Woollam Co., λ =193–1690 nm) 确定。鳍是通过使用 Cl2/HBr 气体的各向异性等离子体蚀刻形成的。 ZrO2/TiN 栅极形成后,S/D 注入 B(1 × 10 15 cm −2 , 15 keV) 并在 550 °C 下快速热退火 30 s 激活。

锗机制的高选择性干蚀刻

电子和中性反应是各向同性的,而离子反应是高度定向的,并随施加的偏压而变化。通过调整偏置功率,离子可以沿所需方向加速以帮助蚀刻反应。人们普遍认为 Br 不会与 Si 自发反应,并且需要高能离子才能发生反应。离子辅助的 Br 和 Cl 原子可以在活化下与 Ge 或 Si 原子自发反应,形成挥发性产物 GeBr4、GeCl4、SiBr4 和 SiCl4,这些产物从衬底表面解吸并可以被抽走。 Si 与 Br 的这种离子辅助化学反应已被证明是高度各向异性的。使用 HBr 获得更高的垂直蚀刻速率以改变偏置功率,这证实在 Cl2 中添加 HBr 可以提高蚀刻速率 [17]。由于 Cl 和 Br 基等离子体通过离子辅助机制蚀刻 Ge 和 Si,因此离子的能量如 Br + , Br 2+ , HBr + , Cl + , 和 Cl2 + 可以通过偏压基板支架来控制。通过改变顶部表面和颈缩区域蚀刻的偏置功率,横向蚀刻速率没有明显变化。在缩颈区域使用 HBr 混合物蚀刻的鳍结构中发现了底切,因为沿 Ge/Si 界面的缺陷增强了横向蚀刻。并且由于侧壁受到离子通量的撞击,掩模可能会影响形状演变。随着轮廓变深和横向离子速度分量增加,这种现象被放大。由于 HBr 等离子体蚀刻工艺 [18] 的高角度依赖性,因此可以得出结论,Ge/Si 界面处的晶体结构相对较弱,因为来自错配位错的部分束缚原子和相对较弱的Ge-Ge 和 Ge-Si 键。通过调整 HBr/Cl2 的比例和偏置功率,可以在 Ge 器件制造过程中获得不同类型的鳍状结构。 Ge和Si的蚀刻特性非常相似。蚀刻 Si 的气体通常以更大的速率蚀刻 Ge。 Ge和Si键的强度已显示为Ge-Ge =263.6 ± 7.1 kJ mol -1 并且Si-Si =325 ± 7 kJ mol -1 [2]。施加不同的偏置功率以通过离子的定向加速来调整垂直蚀刻速率。在门堆叠过程之后记录图像。垂直蚀刻速率由相对于氧化物衬底的膜高度计算。横向蚀刻速率由鳍的两个部分确定:鳍顶表面的横向蚀刻,以及靠近 Ge/Si 界面的颈缩区域的蚀刻。总之,实验发现偏置功率是蚀刻工艺中最关键的参数,因此会相应地影响器件特性。

在本研究中,所有蚀刻工艺均在来自 Lam Research 的 TCP 9600 反应器中进行。这是一个变压器耦合等离子体反应器,允许单独控制线圈(顶部电极)功率和基板(下电极)偏置。加入氦气背面冷却以更有效地控制基板的温度。样品安装在一个 6 英寸。在被引入蚀刻室之前,带有真空润滑脂的硅载体晶片。 HBr/Cl2 化学被用于各向异性蚀刻工艺。工艺压力控制在 10 mTorr。详细的实验设置和条件在 Hsu 等人的研究中进行了说明。 [4].

物理模型

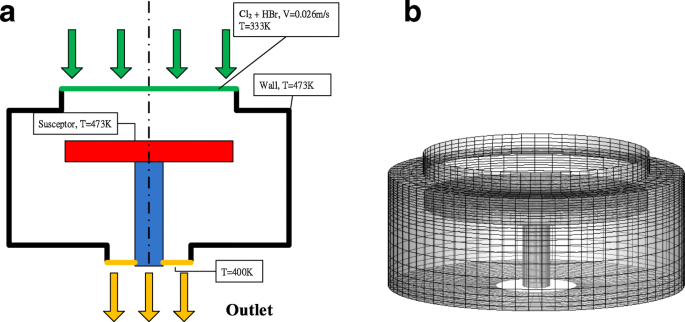

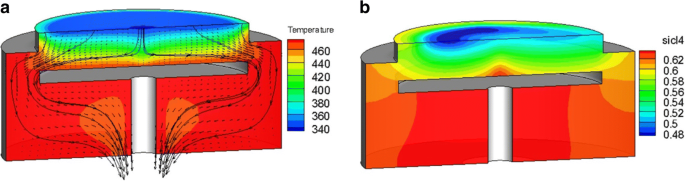

CFD 用于访问反应器内部的内部信息,由于腔室中的克努森数较高,因此流动被认为是具有滑动边界条件的层流(图 1)。在本模拟中,等离子体热流在动量方程中被视为混合;在物质控制方程中考虑了粒子传输,并且在感受器壁上涉及化学反应。图 3 显示了一种模拟模型。入口气体是氯气 (Cl2) 和溴化氢 (HBR) 的混合物。入口处的混合速度为 0.026 m/s,温度保持在 333 K。基座和室壁被加热到工作温度 473 K。这些等离子体流由电势偏压驱动,并在基座表面发生化学反应均匀、可重复的方式,最后从反应器中排出。通过 CAD 软件建立实体模型后,在 50, 000 个节点的结构化网格中构建网格系统,如图 3 所示。 标量 ϕ 传输的瞬态守恒方程由以下积分方程表示任意控制体积V的形式如下[19]:

<图片>

等离子体反应器数值模拟的物理模型。 一 具有指定边界条件的反应室草图。 b 用于数值模拟的网格系统

$$ \frac{d}{dt}\underset{V}{\oint}\rho \varphi\;dV+\oint \kern0.27em \rho \varphi \overset{\rightharpoonup }{v}\cdot \mathrm{ d}\overrightarrow{\mathrm{A}}=\oint \Gamma \mathrm{\nabla}\varphi \cdot \mathrm{d}\overrightarrow{\mathrm{A}}+{\int}_{\mathrm{ V}}{\mathrm{S}}_{\varphi}\mathrm{dV} $$ (1*)其中 ρ 表示密度; \( \overset{\rightharpoonup }{v} \) 是速度矢量; \( \overset{\rightharpoonup {A} \) 是表面积矢量; V 是体积; Γ 是 ϕ 的扩散系数,Sϕ 是每单位体积 ϕ 的源项。对于连续性方程 u,符号 可以用 1 代替 , v , 和 w 分别是 X、Y 和 Z 方向的动量方程,以及反应室中物质传输方程的 Ci。等式(1*) 可以使用模拟的有限体积方法以广义坐标表示。结合边界条件后,方程。 (1*) 可以线性化并在计算域中表示为一组代数方程,可以通过使用 CFD 技术的 SIMPLE 算法求解 [19]。注意到大多数半导体制造设备在远低于大气压力的情况下运行。在如此低的压力下,流体流动处于滑移状态,通常使用的速度和温度的无滑移边界条件不再有效。目前在极低压力下的等离子体流处于滑移状态,介于自由分子流和连续流状态之间 [20]。因此,我们在数值模拟中强加了速度和温度的滑动边界条件来模拟流体流动。

半导体材料 Si(s) 和 Ge(s) 在受热的基座表面被蚀刻掉,由以下表面反应控制:

$$ {\mathrm{Cl}}_2+\mathrm{Si}={\mathrm{SiCl}}_4 $$ (2*.1) $$ 4\mathrm{HBr}+\mathrm{Si}={\mathrm {SiBr}}_4+2{\mathrm{H}}_2 $$ (2*.2) $$ 2{\mathrm{Cl}}_2+\mathrm{Ge}={\mathrm{GeCl}}_4 $$ (2*.3) $$ 4\mathrm{HBr}+\mathrm{Ge}={\mathrm{GeBr}}_4+2{\mathrm{H}}_2 $$ (2*.4)化学反应与方程式中的 Si 蚀刻相似。 (2*.1) 和方程。 (2*.2) 或等式中的 Ge 蚀刻。 (2*.3) 和方程。 (2*.4)。因此,在以下模拟中展示了通过氯和溴化氢的混合物进行的Si蚀刻工艺。

结果与讨论

材料表征

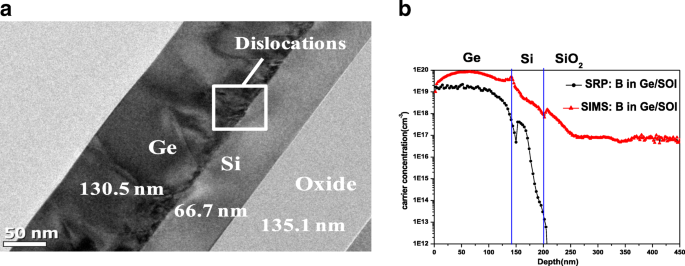

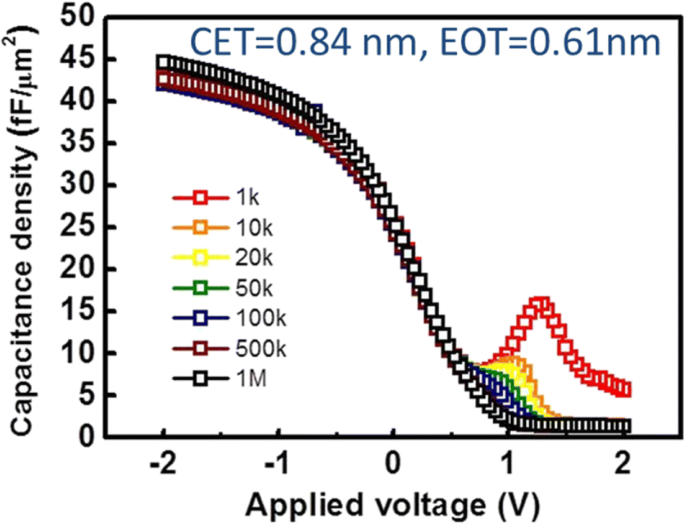

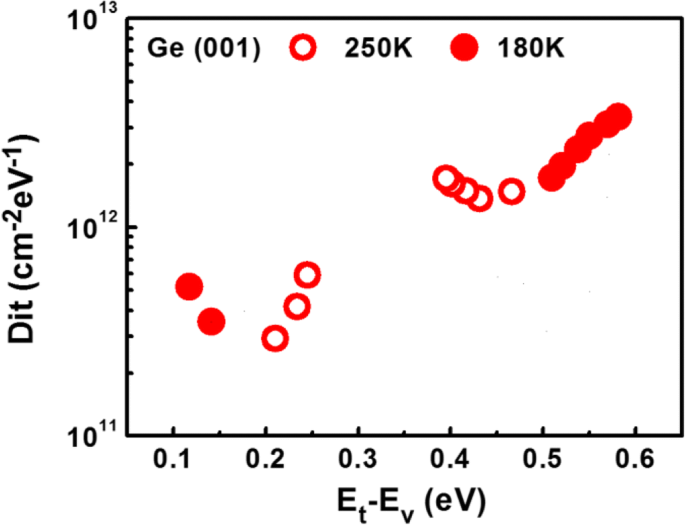

在 SOI 衬底上形成的 Ge 层的横截面 TEM 图像如图 2a 所示。可以看出,Ge/Si 界面存在错配位错;反过来,这些会导致贯穿外延 Ge 膜的穿透位错。这些穿透位错被认为是为了适应 Ge 和 Si 之间的热失配。大多数穿透位错终止于距界面 80 nm 以内;然而,许多也传播到薄膜表面。 SOI 衬底上的外延 Ge 膜被注入硼并随后被激活,以检查掺杂分布和激活水平。对于 Ge 层的顶部 130 nm 部分,硼激活率为 ~ 85%,如 PCOR-SIMS 和扩散电阻分析 (SRP) 曲线所示。 (见图2b)。由于缺陷的存在和 SRP 的测量限制,在 Ge/Si 界面附近的 Ge 层底部的情况下,空穴浓度显着下降。在制造的器件的情况下,通过选择性蚀刻去除Ge/Si界面附近的缺陷Ge;因此,在信道中执行的 PCOR-SIMS 和 SRP 测量应该是准确的。 ~的最大激活级别 3 × 10 19 厘米 −3 与常规的激活极限完全一致。请注意,由于在硼注入过程中进行了低温激活(550°C),寄生硅通道附近的 S/D 具有高电阻(图 2);这防止了寄生硅传导。图 3 显示了 TiN/ZrO2/Ge 金属-绝缘体-半导体电容器 (MISCAP) 的电容-电压 (CV) 特性。为了防止在高 k 介电沉积和沉积后退火过程中形成不稳定的 GeOx 层,氮化物基材料 Ge3N4 而不是 GeO2 作为界面层通过 NH3/H2 插入 Ge(001)表面上远程等离子体处理。 ZrO2 层通过原子层沉积在 250°C 下沉积 20 个循环。测得的 CV 曲线不表示频率色散或从 1 KHz 延伸到 1 MHz,并且是一致的。这种损失在 ZrO2/Ge 界面附近产生陷阱能级,将少数载流子生成的热激活能从对应于 p-Ge 带隙能量的热激活能转移到中带隙能量。等效氧化层厚度 (EOT) 为 0.6 nm,D 它(接口陷阱密度)值为 ~ 3 × 10 12 厘米 2 eV −1 中隙附近,采用低温电导法测量(见图4的插图)。

<图片>

一 SOI 衬底上 p 型 Ge 的 TEM 图像。 b SOI 上原位掺硼外延锗层的 SIMS 和 SRP 分布。 Ge/Si界面附近的底部缺陷Ge空穴浓度低

<图片>

具有 EOT ~ 0.6 nm 的 TiN/ZrO2/Ge MISCAPs 的 C-V 特性

<图片>

低温电导法测定的Dit

反应堆运行参数模拟

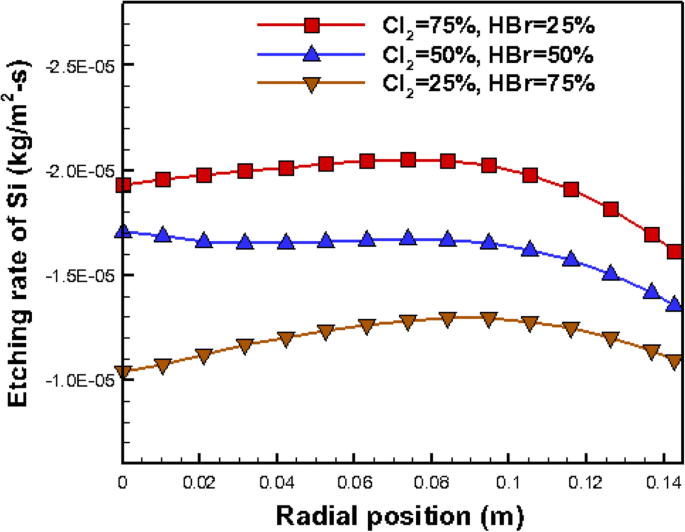

在高速个人计算机上模拟了稳定层流等离子体流的典型模型。入口气体是质量分数为 0.75 的 Cl2 和质量分数为 0.25 的 HBr 的混合物。图 5a 说明了低温流入、在内部操作较高温度和反应室中的粒子路径线的轮廓。图 5b 显示了产物 SiCl4 的质量分数等高线,其在基座上方的浓度较低,而在基座下方的出口处浓度较高。此外,较高质量分数的 Cl2 在蚀刻中具有良好的性能,这一技术已通过图 6 所示的当前模拟得到验证。横轴表示沿着基座上的一个径向位置,纵轴表示蚀刻速率(公斤/米 2 s) 的 Si。图 6 表明,75% Cl2 和 25% HBr 的入口混合物形成了更好的蚀刻工艺,本研究采用这种混合物进行实验。

<图片>

反应器内等离子体参数的轮廓。 一 温度分布和粒子路径线 r。 b 产物SiCl4的质量分数等高线

<图片>

不同比例的进气混合气对基座上硅的刻蚀速率

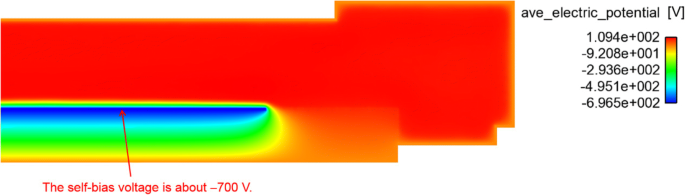

显示计算机辅助实验可行性的另一个案例是等离子体蚀刻室中的电位分布。基于该蚀刻工艺的基本机理,开发了等离子体功率密度分布的二维仿真模型,如图7所示,用于拟合测量数据,以确认模型的准确性并辅助实验。

<图片>

腔内等离子刻蚀电位分布模拟

Sugai [21] 提出,自偏置电压与射频电极(CK)和接地电极(CA)上的护套电容有关,表示如下:

$$ {V}_{\mathrm{DC}}=\frac{C_{\mathrm{K}}-{C}_{\mathrm{A}}}{C_{\mathrm{K}}+{C }_{\mathrm{A}}}\ {V}_{\mathrm{RF}} $$ (3*)根据图 7 所示的当前模拟,自偏置电压约为 - 700 V,接近理论值 - 650 V,由公式计算得出。 (3*)。因此,建议使用模拟进行优化,以便不仅调整所使用的工艺参数,而且修改所使用的硬件。这将有助于确保整个运行的一致性,并优化高质量、低成本的流程。

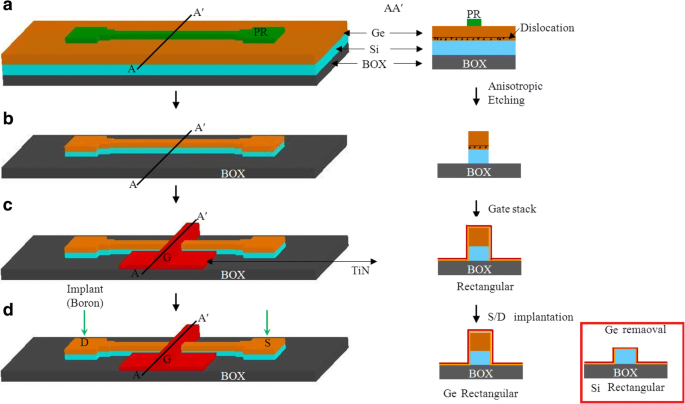

设备制造和表征

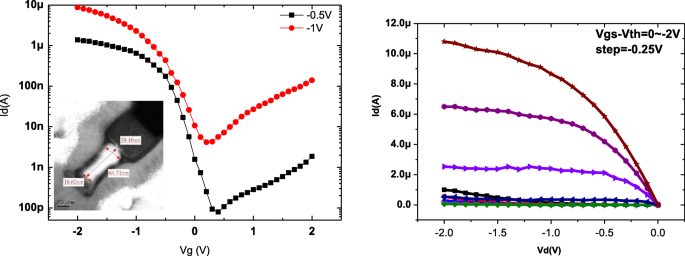

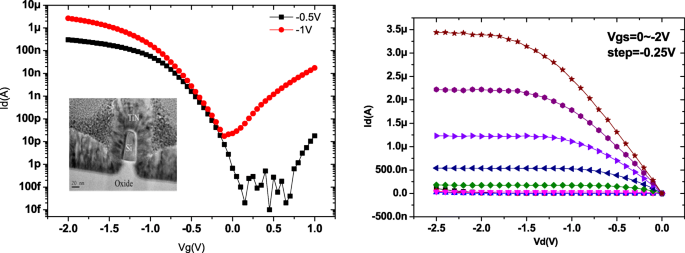

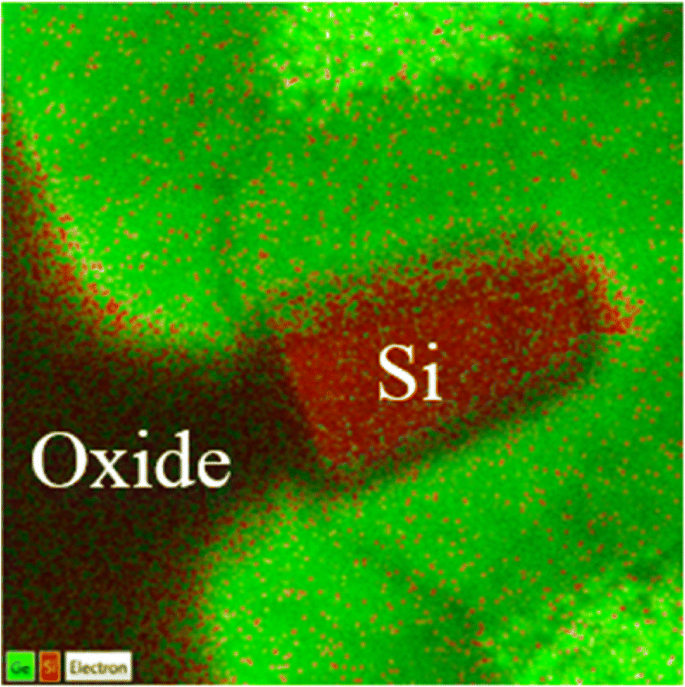

使用电子束光刻将外延 Ge 层图案化为具有所需特征尺寸的鳍。鳍是通过使用 Cl2/HBr 基等离子体进行各向异性蚀刻以蚀刻掉 Ge/Si 界面附近的高缺陷 Ge 形成的。在 SOI 上形成的浮动 Ge 鳍具有比 Si 更高的 Ge 蚀刻选择性和提高的缺陷区域的蚀刻速率 [4]。然后沉积 SiO2 覆盖层并在栅极图案化后成为间隔物。定义有源区后,分别通过ALD形成ZrO2层的栅叠层。制造器件的通道横截面如图 8 所示。鳍片宽度 (W fin) 用于通道浓度为 8 × 10 19 cm − 3 它是使用范德堡方法在 SOI 上的覆盖 Ge 外延层上提取的。注意通道可控性随着通道浓度的增加和W的增加而降低 鳍 [12, 13]。大的通道集中需要小的W 鳍保持低SS。最后,定义并沉积栅电极。图 9 显示了具有鳍宽度 (W) 的三角形 Ge FinFET 的输出和传输特性 fin) 为 18 nm,栅极长度 (L g) 90 纳米。 我 在/我 Ge JL-FET的截止比高达10 5 亚阈值摆幅 (SS) 为 ~ 100 mV dec − 1 . Si JL-FET 的传输特性如图 10 所示。I 在/我 Si JL-FET的关断比高达~ 10 8 , 其 SS 为 90 mV dec − 1 , 它的 L g 为 80 nm,其 W 鳍为 20 纳米。图 8 还显示了栅极电压的跨度 ΔV g, 约为 0.5 V,接近 Ge 的带隙 (E g/q =0.66 V)。这证实了 I d–V 图 8 中所示的 g 曲线是针对 Ge FinFET 的。然而,栅极电压的跨度 ΔV g,如图 6 所示,约为 1.8 V,接近 Si 的带隙 (E g/q =1.1 V) 但不是 Ge (E g/q =0.66 V)。因此,I d–V 图 9 中所示的 g 曲线是针对 Si JL-FET 而不是 Ge JL-FET。该观察结果基于半导体器件物理,并得到实验确定的 I d–V Ge 和 Si FinFET 的 g 曲线以及横截面 TEM/EDS Si 图。从图 11 中的插图中可以明显看出两件事。插图显示了 Ge 过蚀刻后意外的 Si JL-FET 的输出和传输特性; 我 在/我 该设备的关断比高达10 8 .然而,其导通电流仅为 17 μA μm − 1 在 − 1 V. 高 I 在/我 off 比率归因于 Si 层而不是 Ge 层。当只剩下Si层时,器件实际上是Si JL-FET,而不是Ge JL-FET。

<图片>

器件制造示意图。 一 鳍图案。起始材料是 BOX 上的 Ge (130 nm)。 b 各向异性蚀刻和光刻胶剥离。 c 通过 ZrO2 和 TiN 沉积的原子层沉积形成栅极。 d S/D 上的自对准硼注入以实现良好接触。注:左侧为3D原理图,右侧为对应截面图

<图片>

我 d–V g 和 I d–V Ge FinFET的d曲线

<图片>

我 d–V g 和 I d–V d 用于不小心蚀刻掉顶部 Ge 后的 Si FinFET。虽然我 在/我 关可以达到10 8 ,其on电流值很低

<图片>

过刻蚀通道结构的TEM图

结论

我们确认仿真模型和测量数据之间的关系。因此,建议使用模拟进行优化,以便不仅调整所使用的工艺参数,而且修改所使用的硬件。通过数值模拟确定反应器的工作参数,我们表明可以通过实验优化形成Ge/Si通道的蚀刻工艺参数,以改进蚀刻工艺并帮助晶体管的发展提高制造质量,降低生产成本。实验结果表明,为Ge FinFET开发的干法刻蚀技术对于高鳍CMOS器件的制造也非常有用。

纳米材料

- 用于 Micro-LED 和 VCSEL 的高级原子层沉积技术

- 三态电致变色器件的浸涂工艺工程和性能优化

- 通过等离子体增强原子层沉积原位形成 SiO2 中间层的 HfO2/Ge 叠层的界面、电学和能带对准特性

- 铝硅酸盐矿物的替代掺杂和优异的水分解性能

- 化学蚀刻制备的硅纳米线的光学和电学特性

- Li/Nb 比对 Li-Nb-O 化合物制备和光催化性能的影响

- 通过界面层设计调整 ZnO 薄膜的表面形貌和特性

- 中空结构LiNb3O8光催化剂的制备和光催化性能

- 超材料中表面等离子体激元和磁偶极子共振的耦合效应

- 硅纳米线 FET 传感器中的光电导率、pH 灵敏度、噪声和通道长度效应

- Si、Ge 和 Si/Ge 超晶格对低能辐射的辐射响应的理论模拟

- 激光蚀刻和激光雕刻